DSP技术协助进行高速串行数据分析

时间:09-25

来源:互联网

点击:

信号完整性

串行总线技术上的信号完整性测量已经成为设计人员测量工作的重要组成部分,如PCI Express 2.0、串行ATA III和HDMI 1.3。一致性测试中遇到的许多问题源于波形上的不理想特点,如噪声、抖动和定时畸变。串行标准缩窄了定时容限,要求测量工具中提供更多的带宽和更高的精度。与此同时,还要求使测量本身的影响达到最小化。

眼图测量

示波器的带宽影响着至关重要的信号眼图。眼图是一种行业标准示波器图像,也是一致性测试和验证测试的基石,它显示1个数据“位”或单位间隔,所有可能的边沿跳变和状态都叠加在一个完善的视图中。得到的屏幕在中心大体呈六角形张开区域的周围显示大量的波形轨迹,这有点象“眼睛”,其张开程度用来衡量信号质量(“张开”得越多越好)。串行逻辑设备必须区分眼图区域内部清楚的状态‘1’或状态‘0’,以正确对数据作出响应。通常会使用图形“模板”定义眼图测试通过/失败的区域。

在采集信号时,带宽不足的示波器滚降的幅度可能会高达1 dB (垂直幅度)。遗憾的是,这种损耗一般会落在眼图张开的区域中,恰好是进行二进制判定的地方。因此,充足的带宽在眼图测量及边沿测量中至关重要。

幸运的是,现在市场上出现了许多仪器,可以提供最关键的定时和边沿测量要求的带宽。最新的串行分析仪拥有20 GHz的带宽,再加上所有通道上50 GS/s的采样率,可以满足当前使用的全系列串行总线的需求 。在这些速率上,波形边沿10-90%部分的输入上升时间仅为22 ps。正如本文后面讨论的那样,基于DSP的带宽增强技术提供了直到最快速的第一代串行标准第五个谐波范围的平坦的频率性能。这一功能也保证了所有通道中的最优频率和幅度响应匹配。

第五个谐波测量

大多数第一代串行总线结构的数据速率主要集中在2.5Gbit/s和3.125 Gbit/s之间,这些速率似乎完全位于当前4GHz和5 GHz 示波器的掌控范围内。但是,信号保真度测量需要的带宽要高得多,大多数标准机构已经认识到这种需求,他们指定速度足够快的仪器,以捕获时钟信号的第五个谐波。

捕获第五个谐波为检定和分析快速上升时间信号提供了所需的精度,同时为保证准确的结果提供了更多的余量。

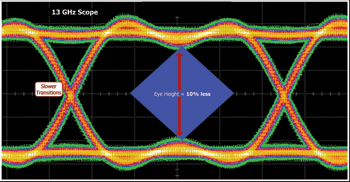

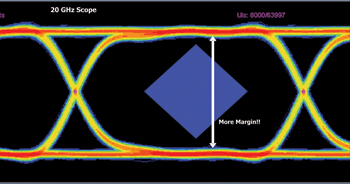

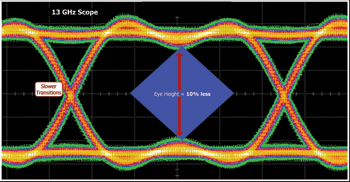

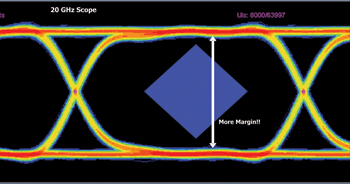

图1说明了怎样增强幅度余量。特别是,它说明了20 GHz 示波器和13 GHz 示波器之间的差异,表明带宽更高的仪器在6.25 Gbit/s 数据流PCI-E Gen2信号上提供的余量要高得多。在20 GHz时,它捕获第五个谐波,在非常“干净的”眼图中可以明显看出充足的余量。在13 GHz 示波器上,没有足够的带宽捕获第五个信号,信号落在模板外面。

某些标准小组,特别是PCI SIG,正努力确定捕获第五个谐波必须提供的具体带宽。

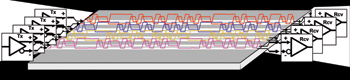

多路结构

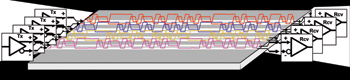

更快的串行总线,包括第二代和第三代串行总线结构,如HDMI 1.3、SATA III和PCI-Express 2.0,在单路应用中提供了更高的性能,同时它们也作为串行数据总线结构实现,其采用多条通路,实现更高的数据交换速率。在多路配置中,串行数据包先被分解,然后基本上同时通过4条、8条或更多的“通路”进行传送(图2)。在多路串行总线上执行验证或调试工作的设计人员需要测试解决方案,同时在4条或4条以上的通路中捕获实时数据,并提供必要的性能,满足最新一代串行总线技术。在验证中,必需在所有信号通路中同时捕获数据,并实现时间相关。市场上现在提供了实时采样率高达50 GS/s的仪器,可以在所有输入通道中实现杰出的时间分辨率,同时在全部4条通道上捕获长达4 ms的时间相关的串行数据业务。这种实时捕获能力与深存储器相结合,使得设计人员能够在每条通路中分析有问题的事件或之前或之后与总线业务相关的错误。

抖动测试

抖动是串行总线开发人员关注的另一个问题。在某些情况下,必须量化其对各个信号边沿的影响,但更重要的是,抖动在眼图测量中发挥着一定的作用。它可以降低上升沿和下降沿相关的眼图宽度,可能会导致模板违规。

如果观察到抖动,那么抖动是来自被测设备还是由于仪器导致的测量附属产物示波器的触发抖动和抖动噪底(JNF)可能会影响测得的抖动,它们可能会使眼图变窄,产生误导性的模板失败。

业内已经开发出精心设计的软件校正方案,以使示波器的触发抖动达到最小,这种方法可望改善等效时间采集模式下的性能,其中必须对每个样点重新触发采集。但是,触发抖动对基于单次实时采集的抖动测量没有影响。在这种情况下,JNF系数会影响等效时间捕获和实时捕获。

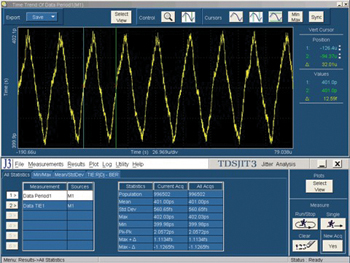

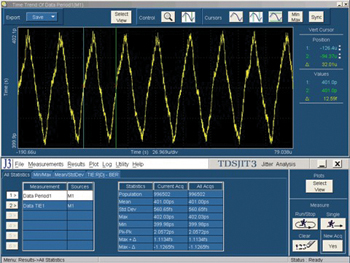

更好的方法是使用在垂直模数转换器中拥有充足动态范围(如垂直格)的仪器,以实现高信噪比及极低的JNF (典型值为400 fs RMS)。这种示波器可以实现抖动测量,仪器本身对抖动的影响不大(图3)。

测量低频抖动是一个挑战。它对示波器提出了两个相互矛盾的需求:示波器要捕获细微的定时细节,同时要在很长的时间跨度内实现这一点。为以足够的分辨率捕获抖动细节,通常必需进入最大采样率(如50 GS/s,相当于20 ps的采样间隔)。采样数据以该速率迅速累积在波形存储器中。但是,低频抖动趋势会在几毫秒内形成。因此,如果仪器要捕获足够的运行周期,确定低频抖动对测量的影响,那么需要非常深的存储器。

对存储容量每条通道高达200 M样点的仪器,在全部采样率下可以存储最长4 ms的采样数据。工程师可以查看各个边沿上及几百万个周期后发生的同一波形记录抖动变化中的深入抖动细节。

串行总线技术上的信号完整性测量已经成为设计人员测量工作的重要组成部分,如PCI Express 2.0、串行ATA III和HDMI 1.3。一致性测试中遇到的许多问题源于波形上的不理想特点,如噪声、抖动和定时畸变。串行标准缩窄了定时容限,要求测量工具中提供更多的带宽和更高的精度。与此同时,还要求使测量本身的影响达到最小化。

眼图测量

示波器的带宽影响着至关重要的信号眼图。眼图是一种行业标准示波器图像,也是一致性测试和验证测试的基石,它显示1个数据“位”或单位间隔,所有可能的边沿跳变和状态都叠加在一个完善的视图中。得到的屏幕在中心大体呈六角形张开区域的周围显示大量的波形轨迹,这有点象“眼睛”,其张开程度用来衡量信号质量(“张开”得越多越好)。串行逻辑设备必须区分眼图区域内部清楚的状态‘1’或状态‘0’,以正确对数据作出响应。通常会使用图形“模板”定义眼图测试通过/失败的区域。

在采集信号时,带宽不足的示波器滚降的幅度可能会高达1 dB (垂直幅度)。遗憾的是,这种损耗一般会落在眼图张开的区域中,恰好是进行二进制判定的地方。因此,充足的带宽在眼图测量及边沿测量中至关重要。

幸运的是,现在市场上出现了许多仪器,可以提供最关键的定时和边沿测量要求的带宽。最新的串行分析仪拥有20 GHz的带宽,再加上所有通道上50 GS/s的采样率,可以满足当前使用的全系列串行总线的需求 。在这些速率上,波形边沿10-90%部分的输入上升时间仅为22 ps。正如本文后面讨论的那样,基于DSP的带宽增强技术提供了直到最快速的第一代串行标准第五个谐波范围的平坦的频率性能。这一功能也保证了所有通道中的最优频率和幅度响应匹配。

第五个谐波测量

大多数第一代串行总线结构的数据速率主要集中在2.5Gbit/s和3.125 Gbit/s之间,这些速率似乎完全位于当前4GHz和5 GHz 示波器的掌控范围内。但是,信号保真度测量需要的带宽要高得多,大多数标准机构已经认识到这种需求,他们指定速度足够快的仪器,以捕获时钟信号的第五个谐波。

捕获第五个谐波为检定和分析快速上升时间信号提供了所需的精度,同时为保证准确的结果提供了更多的余量。

图1说明了怎样增强幅度余量。特别是,它说明了20 GHz 示波器和13 GHz 示波器之间的差异,表明带宽更高的仪器在6.25 Gbit/s 数据流PCI-E Gen2信号上提供的余量要高得多。在20 GHz时,它捕获第五个谐波,在非常“干净的”眼图中可以明显看出充足的余量。在13 GHz 示波器上,没有足够的带宽捕获第五个信号,信号落在模板外面。

某些标准小组,特别是PCI SIG,正努力确定捕获第五个谐波必须提供的具体带宽。

多路结构

更快的串行总线,包括第二代和第三代串行总线结构,如HDMI 1.3、SATA III和PCI-Express 2.0,在单路应用中提供了更高的性能,同时它们也作为串行数据总线结构实现,其采用多条通路,实现更高的数据交换速率。在多路配置中,串行数据包先被分解,然后基本上同时通过4条、8条或更多的“通路”进行传送(图2)。在多路串行总线上执行验证或调试工作的设计人员需要测试解决方案,同时在4条或4条以上的通路中捕获实时数据,并提供必要的性能,满足最新一代串行总线技术。在验证中,必需在所有信号通路中同时捕获数据,并实现时间相关。市场上现在提供了实时采样率高达50 GS/s的仪器,可以在所有输入通道中实现杰出的时间分辨率,同时在全部4条通道上捕获长达4 ms的时间相关的串行数据业务。这种实时捕获能力与深存储器相结合,使得设计人员能够在每条通路中分析有问题的事件或之前或之后与总线业务相关的错误。

抖动测试

抖动是串行总线开发人员关注的另一个问题。在某些情况下,必须量化其对各个信号边沿的影响,但更重要的是,抖动在眼图测量中发挥着一定的作用。它可以降低上升沿和下降沿相关的眼图宽度,可能会导致模板违规。

如果观察到抖动,那么抖动是来自被测设备还是由于仪器导致的测量附属产物示波器的触发抖动和抖动噪底(JNF)可能会影响测得的抖动,它们可能会使眼图变窄,产生误导性的模板失败。

业内已经开发出精心设计的软件校正方案,以使示波器的触发抖动达到最小,这种方法可望改善等效时间采集模式下的性能,其中必须对每个样点重新触发采集。但是,触发抖动对基于单次实时采集的抖动测量没有影响。在这种情况下,JNF系数会影响等效时间捕获和实时捕获。

更好的方法是使用在垂直模数转换器中拥有充足动态范围(如垂直格)的仪器,以实现高信噪比及极低的JNF (典型值为400 fs RMS)。这种示波器可以实现抖动测量,仪器本身对抖动的影响不大(图3)。

测量低频抖动是一个挑战。它对示波器提出了两个相互矛盾的需求:示波器要捕获细微的定时细节,同时要在很长的时间跨度内实现这一点。为以足够的分辨率捕获抖动细节,通常必需进入最大采样率(如50 GS/s,相当于20 ps的采样间隔)。采样数据以该速率迅速累积在波形存储器中。但是,低频抖动趋势会在几毫秒内形成。因此,如果仪器要捕获足够的运行周期,确定低频抖动对测量的影响,那么需要非常深的存储器。

对存储容量每条通道高达200 M样点的仪器,在全部采样率下可以存储最长4 ms的采样数据。工程师可以查看各个边沿上及几百万个周期后发生的同一波形记录抖动变化中的深入抖动细节。

总线 HDMI 示波器 DSP 电子 滤波器 电阻 电容 电感 电路 PCB 连接器 相关文章:

- 基于MSP430系列单片机的CAN总线接口转换卡设计(01-17)

- 各种通讯总线介绍(01-18)

- I2C总线原理及应用实例 (01-18)

- I2C总线在多机通信中的应用(01-17)

- 基于SPI总线的电能计量芯片ATT7022及其在配电监测终端的应用(01-18)

- CAN总线—PROFIBUS-DP总线网关的实现方法(01-17)