嵌入式阵列处理器的发展

时间:09-30

来源:互联网

点击:

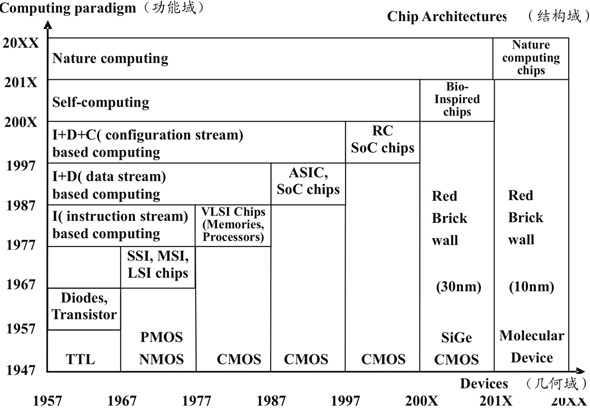

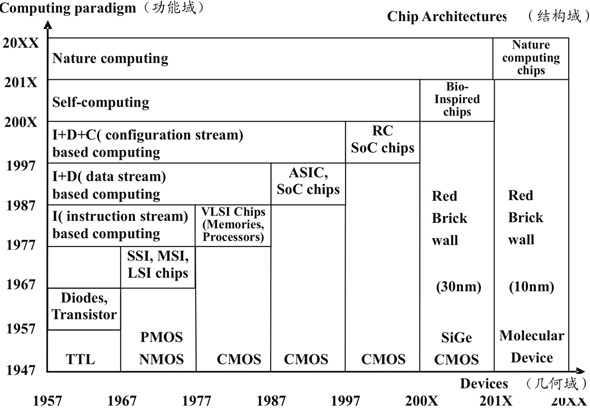

1971年的处理器芯片以及在其基础上发展而来的PC机的问世,使计算机的应用从科学殿堂走进了“寻常百姓家”,同时开辟了计算机嵌入式应用的新模式,促进了工业产品的知识化/智能化。随着芯片集成度的提高与计算模式的演变,如图1所示,1987年人们提出了系统芯片(SoC,System on Chip)的概念,要将计算机的系统设计也转移到芯片设计上来。从提出一个新概念到这一概念的成果市场化,一般大约需要30年左右的时间。系统芯片概念提出之后,经过20多年的努力,逐渐形成了两种系统芯片。一种是以处理器为IP核的多处理器系统芯片(MP SoC,Multi Processor SoC),简称MP系统芯片;另一种是根据并行计算技术与深亚微米技术的发展需要而发展起来的大规模并行处理系统芯片(MPP SoC, Massively Parallel Processing SoC),简称MPP系统芯片。因为采用了阵列的实现方法,对处理器来说又可以叫做阵列处理器(Array Processor)。下面将主要讨论嵌入式阵列处理器的阵列设计、制造技术与应用领域的新发展。

图1 芯片集成度,计算模式与芯片体系结构的发展

阵列设计的发展

处理器芯片,以及在其基础上发展起来的MP系统芯片,设计和应用都发展得比较成熟。目前许多嵌入式计算机的系统设计,已经转移到嵌入式MP系统芯片的设计上来;不仅如此,1985年开始的FPGA技术,在2000年就推出了带嵌入式处理器ARM的FPGA芯片,现在已发展成了嵌入式MP系统芯片的一种硬件设计平台。国内已研制出以8位、16位以及32位处理器为核心的,与应用领域紧密相关的嵌入式MP系统芯片。随着嵌入式应用的微型化与并行计算的要求越来越高,以及深亚微米技术的不断发展所带来的“红墙”问题,使嵌入式阵列处理器的设计成了新的研究热点。

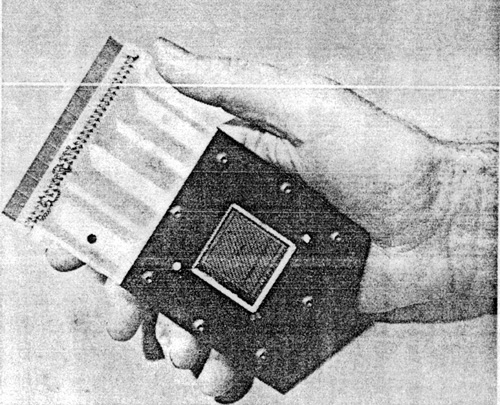

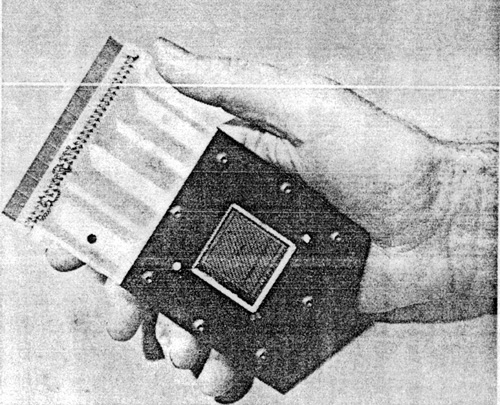

为了航空航天图像处理电子设备的微型化,美国休斯(Hughes)公司在3um CMOS工艺的基础上,采用圆片级的3D 二次集成电路技术,按照SIMD PE阵列的体系结构,于1987年10月就研制成功了一种3D 阵列处理器。该阵列处理器由5个大圆片(Wafer)组成了32×32个16位定点处理元的PE阵列,工作频率10 MHz,峰值速度为600 MOPS,功耗约1.5W,体积只有手掌大小,如图2所示。除了32×32的PE阵列外,休斯公司还先后研制了每个大圆片上有128×128与256×256(=65536)个功能模块的阵列处理器。

图2 休斯公司的第一台3-D MPP计算机

与其它嵌入式处理器不同,嵌入式阵列处理器设计的发展,从休斯公司的图像处理的阵列处理器可以看出,是由成千上万的处理元PE的阵列组成的。其它的阵列处理器是存在一个并行编程的语言问题的,早期的解决方法是把常用的程序设计语言扩充成并行程序设计语言,但没有得到推广;现在的解决方法是采用面向并行编程模式的映射语言。由于图像处理的嵌入式阵列处理器,是一种支持数据并行计算的可编程的阵列处理器,采用的是指令流计算模式的SIMD PE阵列的体系结构,与超级计算的阵列处理器不同。这是一种自然的实现数据并行计算的阵列处理器的体系结构,因为按时间映射方法执行数据并行算法时,SIMD PE阵列上所有PE每个周期执行的是同样的一条指令的“数组操作”,数组大小理论上是没有限制的;SIMD PE阵列的阵列处理器可以看作是数据并行算法的算法处理器(Algorithm Processor),而不必看作是一个多处理器,从而得到了图像处理器的并行编程简单性、高效性与通用性。由于SIMD计算方式对数据并行计算的效果非常显著,在有些处理器/多核处理器/众核处理器的指令集合中,也增加了支持SIMD 计算的MMX指令。

现代的阵列处理器的PE阵列基本上是支持两维算法的,因为现在计算机的传感器输入主要是空间上的两维阵列,显示器输出也主要还是空间上的两维阵列,相应的PE阵列自然是两维的;而可视空间是三维的,计算科学家是通过立体视觉算法在两维阵列的显示器上形成三维的立体感的。其实,随应用领域的不同,完成空间并行计算的阵列处理器还可以是三维的。阵列大小是可以系列化的,阵列设计的发展主要是处理元PE的概念,以及处理元PE中的操作的概念,都应当是广义的,还有一般处理器中所没有的处理元PE之间的互连方法以及阵列处理器芯片之间的互连方法。

随应用领域的不同,处理元PE的设计参数(字长精度、存储容量与运算速度,以及体积、重量、功耗与可靠性等)是可以像处理器一样系列化的。不仅如此,为了实现阵列处理器芯片的换代作用,使阵列处理器芯片不仅能够替代处理器芯片,还可以替代现在的可重构的空间映射的并行处理芯片(静态可重构的FPGA芯片与动态可重构的RC Device芯片),处理元PE的概念应当是广义的。随应用领域的要求不同,可以是现在已知的处理器(RISC/DSP),也可以是现在未知的,例如,RC Device阵列中的功能模块,FPGA阵列中的逻辑门或神经元,FPAA阵列中的模拟器件,FPTA阵列中的晶体管等。相应的处理元PE中的操作的概念也是广义的,可以是现在已知的处理器操作(算术/逻辑等);也可以是现在未知的“操作”,例如,对模拟器件的“操作”,对晶体管的“操作”等。处理元PE之间的互连方法以及阵列处理器芯片之间的互连方法,现在都还没有发展到成熟的地步,为阵列设计提供了广阔的发展空间。

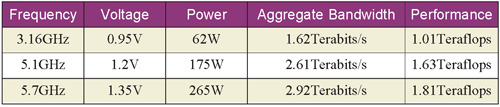

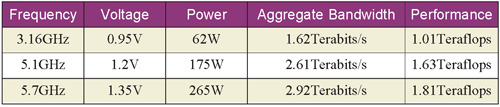

表1 Intel阵列处理器的性能

图1 芯片集成度,计算模式与芯片体系结构的发展

阵列设计的发展

处理器芯片,以及在其基础上发展起来的MP系统芯片,设计和应用都发展得比较成熟。目前许多嵌入式计算机的系统设计,已经转移到嵌入式MP系统芯片的设计上来;不仅如此,1985年开始的FPGA技术,在2000年就推出了带嵌入式处理器ARM的FPGA芯片,现在已发展成了嵌入式MP系统芯片的一种硬件设计平台。国内已研制出以8位、16位以及32位处理器为核心的,与应用领域紧密相关的嵌入式MP系统芯片。随着嵌入式应用的微型化与并行计算的要求越来越高,以及深亚微米技术的不断发展所带来的“红墙”问题,使嵌入式阵列处理器的设计成了新的研究热点。

为了航空航天图像处理电子设备的微型化,美国休斯(Hughes)公司在3um CMOS工艺的基础上,采用圆片级的3D 二次集成电路技术,按照SIMD PE阵列的体系结构,于1987年10月就研制成功了一种3D 阵列处理器。该阵列处理器由5个大圆片(Wafer)组成了32×32个16位定点处理元的PE阵列,工作频率10 MHz,峰值速度为600 MOPS,功耗约1.5W,体积只有手掌大小,如图2所示。除了32×32的PE阵列外,休斯公司还先后研制了每个大圆片上有128×128与256×256(=65536)个功能模块的阵列处理器。

图2 休斯公司的第一台3-D MPP计算机

与其它嵌入式处理器不同,嵌入式阵列处理器设计的发展,从休斯公司的图像处理的阵列处理器可以看出,是由成千上万的处理元PE的阵列组成的。其它的阵列处理器是存在一个并行编程的语言问题的,早期的解决方法是把常用的程序设计语言扩充成并行程序设计语言,但没有得到推广;现在的解决方法是采用面向并行编程模式的映射语言。由于图像处理的嵌入式阵列处理器,是一种支持数据并行计算的可编程的阵列处理器,采用的是指令流计算模式的SIMD PE阵列的体系结构,与超级计算的阵列处理器不同。这是一种自然的实现数据并行计算的阵列处理器的体系结构,因为按时间映射方法执行数据并行算法时,SIMD PE阵列上所有PE每个周期执行的是同样的一条指令的“数组操作”,数组大小理论上是没有限制的;SIMD PE阵列的阵列处理器可以看作是数据并行算法的算法处理器(Algorithm Processor),而不必看作是一个多处理器,从而得到了图像处理器的并行编程简单性、高效性与通用性。由于SIMD计算方式对数据并行计算的效果非常显著,在有些处理器/多核处理器/众核处理器的指令集合中,也增加了支持SIMD 计算的MMX指令。

现代的阵列处理器的PE阵列基本上是支持两维算法的,因为现在计算机的传感器输入主要是空间上的两维阵列,显示器输出也主要还是空间上的两维阵列,相应的PE阵列自然是两维的;而可视空间是三维的,计算科学家是通过立体视觉算法在两维阵列的显示器上形成三维的立体感的。其实,随应用领域的不同,完成空间并行计算的阵列处理器还可以是三维的。阵列大小是可以系列化的,阵列设计的发展主要是处理元PE的概念,以及处理元PE中的操作的概念,都应当是广义的,还有一般处理器中所没有的处理元PE之间的互连方法以及阵列处理器芯片之间的互连方法。

随应用领域的不同,处理元PE的设计参数(字长精度、存储容量与运算速度,以及体积、重量、功耗与可靠性等)是可以像处理器一样系列化的。不仅如此,为了实现阵列处理器芯片的换代作用,使阵列处理器芯片不仅能够替代处理器芯片,还可以替代现在的可重构的空间映射的并行处理芯片(静态可重构的FPGA芯片与动态可重构的RC Device芯片),处理元PE的概念应当是广义的。随应用领域的要求不同,可以是现在已知的处理器(RISC/DSP),也可以是现在未知的,例如,RC Device阵列中的功能模块,FPGA阵列中的逻辑门或神经元,FPAA阵列中的模拟器件,FPTA阵列中的晶体管等。相应的处理元PE中的操作的概念也是广义的,可以是现在已知的处理器操作(算术/逻辑等);也可以是现在未知的“操作”,例如,对模拟器件的“操作”,对晶体管的“操作”等。处理元PE之间的互连方法以及阵列处理器芯片之间的互连方法,现在都还没有发展到成熟的地步,为阵列设计提供了广阔的发展空间。

表1 Intel阵列处理器的性能

嵌入式 SoC FPGA ARM 电子 CMOS 集成电路 传感器 显示器 DSP 电路 电流 相关文章:

- 嵌入式系统的定义与发展历史(11-15)

- 嵌入式系统亲密接触(11-22)

- 嵌入式系统设计中的USB OTG方案(02-01)

- 嵌入式线控驾驶系统开发过程中设计和测试考虑(02-02)

- 一个典型的嵌入式系统设计和实现 (02-02)

- DDR SDRAM在嵌入式系统中的应用(02-07)