调节多核处理器硬件适应软件设计方法

时间:09-24

来源:互联网

点击:

- 存储器

第三个问题跟所需的存储器数量有关。在一个典型的系统中,所能存储的代码和数据的数量是固定的。如果你的设计没有满足这一要求,就需要做大量的工作来将多出的内容压缩到存储空间中。但是在使用FPGA时,只要所需存储器的数量在芯片所能提供的范围之内,就能够按照实际需要为每个处理器分配存储空间。在更典型的情况下,所有的存储空间的大小都相同(由于每个块的最小容量为2k,这就限制了进行微调的程度)。

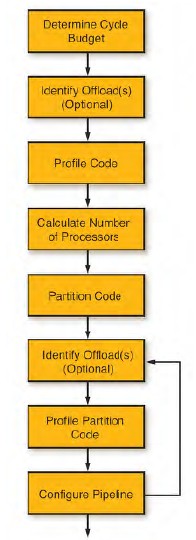

图2 - 配置并行流水线的流程

代码编译时提供所需存储器的大小,并且可以使用下面的陈述式来编辑配置头文件,在这个示例中为代码和数据存储分配的存储空间均为8KB:

#define CPE_CODE_MEM_SIZE_KB 8

#define CPE_DATA_MEM_SIZE_KB 8

使用减负器来加快处理速度

第四个问题和创建硬件加速器有关。可能有一部分程序会占用太多的周期。要减少周期就需要更多的处理器,而使用硬件加速器就能减少处理器的数量。只要硬件加速器比其所替代的处理器占用更少的门,就能够减少整个硬件实现的面积。

Teja有一项功能就是用来从代码中直接创建这样的加速器或减负器。通过对程序进行注释,此功能就可创建:

- 实现代码的硬件逻辑

- 通过系统接口在处理器基础设施中添加加速器

- 调用原型替换程序中最初的代码

- 在将减负器集成于系统之前,先使用测试台对其进行验证。

一旦创建了减负器,周期数就会减少,因此你需要重新安排处理器。但由于重新定义流水线结构的操作十分方便,因此这是一项很简单的任务。

一个简单直接的方法

将前面所述的步骤组合在一起,就产生了图2中所示的设计流程。你可以先定义减负器(对于明显需要减负器的任务),或在配置好流水线之后再定义减负器(如果现有的代码使用了太多的处理器)。

软件工程师所能控制的是一些在他们看来自然和简单的参数,这里使用自然的软件语言(ANSI C)来表达这些参数。对硬件进行实体化的所有细节都由TejaCC程序来处理,它会为Xilinx嵌入式开发系统(EDK)创建一个项目。剩下的编译/综合/布局/布线和产生比特流以及镜像代码的工作全都由EDK来完成。

在这种方式下,电路板可以由硬件工程师设计,但通过使用FPGA,硬件工程师能够将最终的实现中硬件配置的关键部分,留给软件设计者去完成。这一方法还支持在设计即将完成时对电路板进行改动(例如,由于性能原因要对存储器的类型和容量进行改动)。由于Teja工具能创建FPGA的硬件定义,其中包括存储器控制器和其他外设,因此设计人员可以轻松地调节电路板。最终的结果是,由于硬件实现可以适应软件的变化,因此软件设计者不再需要花费大量的时间来围绕一个固定的硬件设置编写程序。

通过利用灵活的Virtex - 4 FPGA和MicroBlaze核,Teja FP环境和基本结构使得所有这一切都变成了可能。有了这一强大的工具,你就能够将开发周期缩短几周甚至几个月。

Teja还提供了一些高级应用程序,这些应用程序能用来启动一个项目,并减少所需的工作量。将一个灵活省时的设计方法和一个事先定义好的应用程序结合起来使用,网络设备的制造者就能更快地完成他们的设计。

嵌入式 FPGA 电路 总线 Xilinx 硬件工程师 相关文章:

- 嵌入式系统的定义与发展历史(11-15)

- 嵌入式系统亲密接触(11-22)

- 嵌入式系统设计中的USB OTG方案(02-01)

- 嵌入式线控驾驶系统开发过程中设计和测试考虑(02-02)

- 一个典型的嵌入式系统设计和实现 (02-02)

- DDR SDRAM在嵌入式系统中的应用(02-07)