基于XC166单片机的DSP优化方法

时间:09-02

来源:互联网

点击:

2 与芯片相关的优化技术

2.1 XC166指令流水线

XC166单片机指令流水线共有7级,前两级为取指令流水线,后5级为执行流水线,所有指令都必须经过5级执行流水线的每一级。

第1级--指令预取。这一级根据预测顺序,把指令从程序管理单元(PMU)取出,取出的指令在跳转检测单元进行前期处理,以检测是否有跳转,预测逻辑决定是否接收转移。

第2级--取指令。根据转移预测规则计算出下一条被取指令的指针。对于零机器周期转移,转移合并单元先预处理,并将检测到的转移与正在执行的指令结合起来。预取出的指令存在FIFO缓存器中,同时,下一条要执行的指令输出FIFO缓存器,进入执行流水线。

第3级--译码。指令被译码,如需要,在间接寻址模式中,寄存器文件将被访问,以读取通用寄存器GPR。

第4级--寻址。计算所有操作数地址,对于所有隐含访问系统堆栈的指令,堆栈指针递减或增加。

第5级--存储。所有需要的操作数被取出。

第6级--执行。使用已取出的操作数进行MAC单元操作。对于非MAC单元指令,在这一级中,指令将由算术逻辑单元(ALU)执行。条件标志被更新,执行所有直接对CPU特殊功能寄存器CPU_SFRs进行写操作的指令,在间接寻址时,作为地址指针的GPRs自动递减或增加。

第7级--写回。所有外部操作数以及剩余的,在内部DPRAM空间内的操作器被写回。定位在内部SRAM中的操作数进入写回缓冲区。

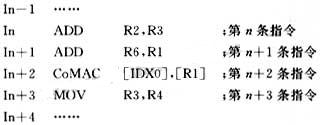

下面给出一个具体例子:

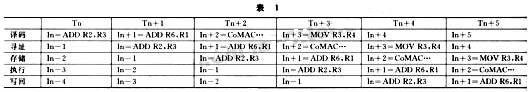

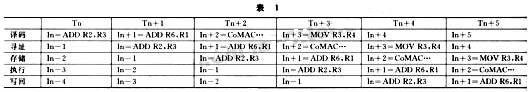

上面程序的指令流水线如表1所列,(Tn表示机器周期)

2.2 数据相关性排除

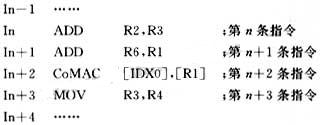

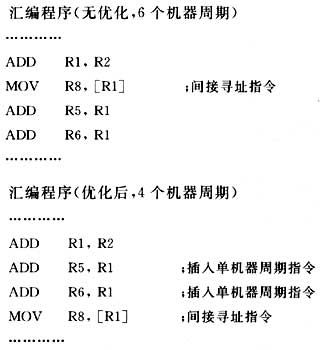

在XC166的CPU中,由于指令流水线的设计要求,在使用通用寄存器(GPRs)的指令之间存在一些数据相互依赖的情况,尽管XC166单片机已经使用了专用硬件来检测及解决数据相关性,但仍然有一些不可避免的数据相关性。在编程时,可以充分利用数据相关性来达到程序优化的目的,比如,在用GPR作为间接寻址指针时,如果PGR中的地址值被改变,间接寻址操作必须等待2个机器指令周期后,才能使用GPR作为地址指针寻址。在这种情况下,可以在这2个等待机器周期内插入2条其他单机器周期指令,充分利用这2个周期的等待时间以便程序更优化。

下面举一个例子:

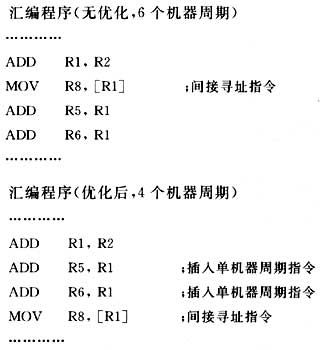

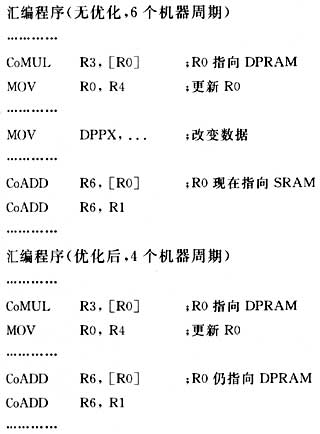

另外一种数据相关性发生在间接寻址访问内存时,XC166单片机中的地址产生单元使用推测原理,在地址译码前,数据的读取路经将根据历史记录表中选出;在历史记录表中,每个GPR都有一个入口。这些入口记录了用相应GPR所访问的内存空间情况。如果这种预测发生错误,读取操作必须重新开始。

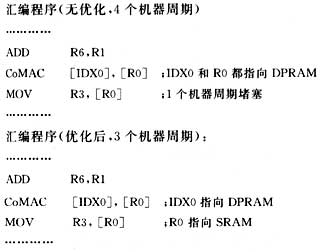

因此,如果用GPR作为间接寻址,GPR最好能指向相同内存空间。如果更新后的GPR指向不同内存空间,下一个操作将出现访问错误,读操作必须重复,这就产生了指令流水线堵塞。例如:

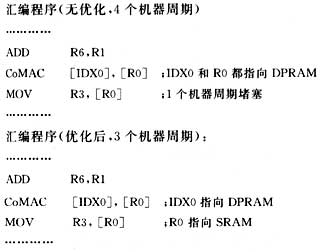

2.3 内存带宽冲突排除

如果在流水线上的指令在同一时间访问同一内存,就会发生内存带宽冲突,MAC单元的CoXXX指令是特别为实现DSP设计的。为了避免在DPRAM中发生带宽冲突,CoXXX指令的其中一个操作数必须放在SRAM中,以保证在单个机器周期内执行MAC单元指令。例如:

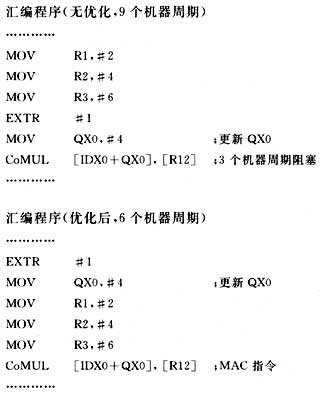

2.4 指令重排

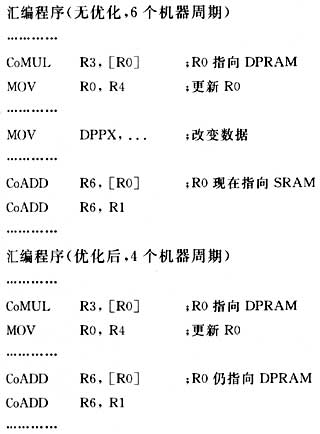

在用MAC单元指令编程时,经常要改变MAC单元的特殊功能寄存器,比如IDX0,IDX1、QX0、QX1、QR0以及QR1等,在XC166单片机中,有一些指令将会阻塞在译码阶段,如果这些指令正好在一条修改特殊功能寄存器(SFR)指令之后执行,这种阻塞将引起3个机器周期的延时。

这些指令包括:

◇使用长地址模式的指令;

◇使用间接寻址的指令,除JMPS和CALLI外;

◇所有MAC单元指令(CoXXX指令)。

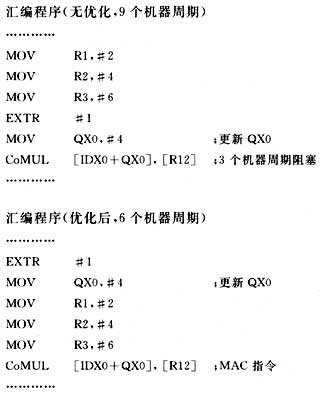

为了避免指令阻塞,在使用上述指令时,如有阻塞情况发生,应该重新重排指令,以消除延时,例如:

3 结论

用于英飞凌XC166单片机的DSP优化技术分为两类:与硬件相关的优化技术和独立于硬件的优化技术。独立于硬件的优化技术也可以用于其他的单片机或专用数字信号处理器。

2.1 XC166指令流水线

XC166单片机指令流水线共有7级,前两级为取指令流水线,后5级为执行流水线,所有指令都必须经过5级执行流水线的每一级。

第1级--指令预取。这一级根据预测顺序,把指令从程序管理单元(PMU)取出,取出的指令在跳转检测单元进行前期处理,以检测是否有跳转,预测逻辑决定是否接收转移。

第2级--取指令。根据转移预测规则计算出下一条被取指令的指针。对于零机器周期转移,转移合并单元先预处理,并将检测到的转移与正在执行的指令结合起来。预取出的指令存在FIFO缓存器中,同时,下一条要执行的指令输出FIFO缓存器,进入执行流水线。

第3级--译码。指令被译码,如需要,在间接寻址模式中,寄存器文件将被访问,以读取通用寄存器GPR。

第4级--寻址。计算所有操作数地址,对于所有隐含访问系统堆栈的指令,堆栈指针递减或增加。

第5级--存储。所有需要的操作数被取出。

第6级--执行。使用已取出的操作数进行MAC单元操作。对于非MAC单元指令,在这一级中,指令将由算术逻辑单元(ALU)执行。条件标志被更新,执行所有直接对CPU特殊功能寄存器CPU_SFRs进行写操作的指令,在间接寻址时,作为地址指针的GPRs自动递减或增加。

第7级--写回。所有外部操作数以及剩余的,在内部DPRAM空间内的操作器被写回。定位在内部SRAM中的操作数进入写回缓冲区。

下面给出一个具体例子:

上面程序的指令流水线如表1所列,(Tn表示机器周期)

2.2 数据相关性排除

在XC166的CPU中,由于指令流水线的设计要求,在使用通用寄存器(GPRs)的指令之间存在一些数据相互依赖的情况,尽管XC166单片机已经使用了专用硬件来检测及解决数据相关性,但仍然有一些不可避免的数据相关性。在编程时,可以充分利用数据相关性来达到程序优化的目的,比如,在用GPR作为间接寻址指针时,如果PGR中的地址值被改变,间接寻址操作必须等待2个机器指令周期后,才能使用GPR作为地址指针寻址。在这种情况下,可以在这2个等待机器周期内插入2条其他单机器周期指令,充分利用这2个周期的等待时间以便程序更优化。

下面举一个例子:

另外一种数据相关性发生在间接寻址访问内存时,XC166单片机中的地址产生单元使用推测原理,在地址译码前,数据的读取路经将根据历史记录表中选出;在历史记录表中,每个GPR都有一个入口。这些入口记录了用相应GPR所访问的内存空间情况。如果这种预测发生错误,读取操作必须重新开始。

因此,如果用GPR作为间接寻址,GPR最好能指向相同内存空间。如果更新后的GPR指向不同内存空间,下一个操作将出现访问错误,读操作必须重复,这就产生了指令流水线堵塞。例如:

2.3 内存带宽冲突排除

如果在流水线上的指令在同一时间访问同一内存,就会发生内存带宽冲突,MAC单元的CoXXX指令是特别为实现DSP设计的。为了避免在DPRAM中发生带宽冲突,CoXXX指令的其中一个操作数必须放在SRAM中,以保证在单个机器周期内执行MAC单元指令。例如:

2.4 指令重排

在用MAC单元指令编程时,经常要改变MAC单元的特殊功能寄存器,比如IDX0,IDX1、QX0、QX1、QR0以及QR1等,在XC166单片机中,有一些指令将会阻塞在译码阶段,如果这些指令正好在一条修改特殊功能寄存器(SFR)指令之后执行,这种阻塞将引起3个机器周期的延时。

这些指令包括:

◇使用长地址模式的指令;

◇使用间接寻址的指令,除JMPS和CALLI外;

◇所有MAC单元指令(CoXXX指令)。

为了避免指令阻塞,在使用上述指令时,如有阻塞情况发生,应该重新重排指令,以消除延时,例如:

3 结论

用于英飞凌XC166单片机的DSP优化技术分为两类:与硬件相关的优化技术和独立于硬件的优化技术。独立于硬件的优化技术也可以用于其他的单片机或专用数字信号处理器。

- F1aSh存储器在TMS320C3X系统中的应用(11-11)

- 基于PIC18F系列单片机的嵌入式系统设计(11-19)

- DSP在卫星测控多波束系统中的应用(01-25)

- 基于PCI总线的双DSP系统及WDM驱动程序设计(01-26)

- 利用Virtex-5 FPGA实现更高性能的方法(03-08)

- DSP与单片机通信的多种方案设计(03-08)