一种基于嵌入式技术的VoIP网关设计

时间:09-01

来源:互联网

点击:

VoIP的应用趋势

作为NGN(下一代网络)中的重要组成部分,VoIP是面向未来、可持续发展的语音解决方案,可以为商业和家庭用户提供质优价廉的IP语音服务。随着 NGN网络技术的快速发展,VoIP的通信量也已得到快速增长,并以其低廉的价格优势迅速占有市场。

VoIP语音技术与传统电话的区别

VoIP(又称IP PHONE)是建立在IP技术上的分组化、数字化语音传输技术。其基本原理是:通过语音压缩算法对语音数据进行压缩编码处理,然后把这些语音数据按IP等相关协议进行打包,经过IP网络把数据包传输到接收地,再把这些语音数据包串起来,经过解码解压处理后,恢复成原来的语音信号,从而达到由IP网络传送语音的目的。VoIP系统把传统电话的模拟信号转换成计算机可联入因特网传送的IP数据包,同时也将收到的IP数据包转换成声音的模拟电信号。经过VoIP系统的转换及压缩处理,每个普通电话传输速率约占用8~11kbit/s带宽,因此在与普通电信网同样使用传输速率为64kbit/s的带宽时, VoIP线路数是原来的5~8倍。同时,IP技术允许多个用户共用同一带宽资源,改变了传统电话由单个用户独占一个信道的方式,节省了用户使用单独信道的费用。

VoIP的基本结构由网关(GW)和网守(GK)两部分构成。网关的主要功能是信令处理、H.323协议处理、语音编解码和路由协议处理等,对外分别提供与PSTN网连接的中继接口以及与IP网络连接的接口。网守的主要功能是用户认证、地址解析、带宽管理、路由管理、安全管理和区域管理。VoIP的核心与关键设备是VoIP网关。

基于嵌入式技术的VoIP功能实现框图

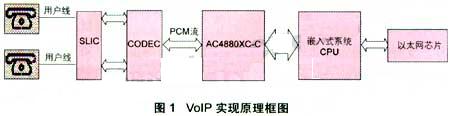

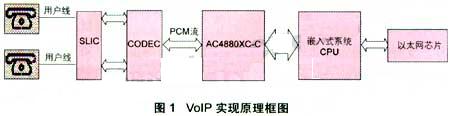

1、VoIP实现原理框图:(如图1)

2、嵌入式系统中VoIP的工作过程:

① 在单个独立的嵌入式系统内部进行语音通信时,该系统实现功能的过程如下:用户话音脉冲通过SLIC和CODEC电路产生PCM流,载入语音处理器 AC4880XC-C中,通过片内DSP进行语音压缩、成帧(包括地址等用户信息及语音信息),AC4880XC-C再将数据包通过HPI口传送到主系统,完成交换功能后,认定目的地是本系统的另一个用户,将处理过的话音数据包传给AC4880XC-C,AC4880XC-C进行解压缩后,以PCM流返回到CODEC部分,根据目的地址信息驱动目的用户。

② 在嵌入式系统之间进行语音通信时,过程如下:AC4880XC-C将话音数据包通过HPI口传给本系统后,本系统的交换功能认定目的地是另一个嵌入式系统的一个用户,本系统将数据包重组后,通过I/O端口传给目的系统,由目的系统自动完成解压缩,驱动目的用户的功能。

系统设计实现

硬件设计为以下六块组成

1、SLIC(用户线接口电路)部分

采用AMD公司生产的AM79R70PLCC芯片,通过该芯片产生输入、输出话音脉冲和铃音脉冲。

2、CODEC(编解码)部分

采用AMD公司生产的AM79Q021JC编解码芯片,通过该芯片产生的PCM流送到语音处理芯片处理。

3、语音处理部分

作为本系统中的核心部分,语音处理采用以色列AudioCodes公司生产的专用多通道语音处理芯片AC4880XC-C。它具有以下特点:

⊙ 支持ITU的G.711、G.723.1、G.726、G.729A等分组语音处理标准;

⊙ 支持回波抵制和抵消、静音检测和舒适噪音等提高分组语音处理性能的配套模块;

⊙ 高质量坏帧插补;

⊙ 支持2.4"14.4 kbps的T.38和FRF.11的功能传真业务;

⊙ 支持各种信令,如DTMF等;

⊙ 提供语音、传真、数据或信令等PCM高速接口;

⊙ 可选择 或o 律;

⊙ 输入输出增益控制;

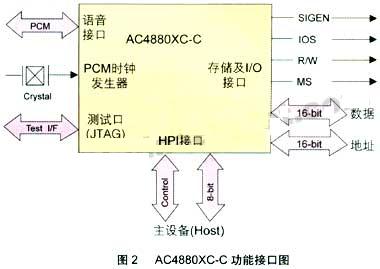

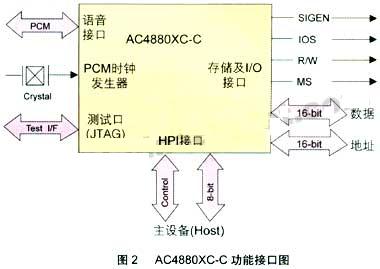

⊙ 提供同步HPI、PCM、时钟、存储器以及I/O和仿真测试接口(如图2);

⊙ 144pin,TQFP封装,1.8V内核电压,3.3V芯片电压。

4、CPLD部分

AC4880XC-C采用8位并行的主处理器接口HPI接口与主系统进行数据交换。鉴于嵌入式系统中接口逻辑繁杂,选用CPLD实现接口适配功能。主 CPU可通过CPLD控制实现CODEC 和SLIC部分的功能。

[table][/table]

5、HPI接口部分

本设计中,嵌入式系统CPU与AC4880XC-C通过HPI接口进行数据通信,CPU通过AC4880XC-C片内共享的双口存储器与其片内DSP实现数据交互。HPI接口包括1根8位数据总线和11根控制总线。主系统CPU通过三个寄存器(HPIC、HPIA和HPID)控制AC4880XC-C及访问片内存储空间。HPIC为控制寄存器,用来选择AC4880XC-C的高低字节顺序。HPIA为地址寄存器,用来寻址片内的2K存储空间。HPID为数据寄存器,用来缓存每次读写的两个字节数据,外部CPU以单个Word或块数据访问HPID。以块数据方式访问时,HPIA寄存器自动累加,可减少外部 CPU写HPIA寄存器的开销。AC4880XC-C的内部寄存器和存储器为16位,外部CPU每次访问AC4880XC-C必须以两个字节为基本单位,信号线HI/LO用来选择高低字节,信号HRS1、HRS0指示当前访问的是哪个寄存器。

作为NGN(下一代网络)中的重要组成部分,VoIP是面向未来、可持续发展的语音解决方案,可以为商业和家庭用户提供质优价廉的IP语音服务。随着 NGN网络技术的快速发展,VoIP的通信量也已得到快速增长,并以其低廉的价格优势迅速占有市场。

VoIP语音技术与传统电话的区别

VoIP(又称IP PHONE)是建立在IP技术上的分组化、数字化语音传输技术。其基本原理是:通过语音压缩算法对语音数据进行压缩编码处理,然后把这些语音数据按IP等相关协议进行打包,经过IP网络把数据包传输到接收地,再把这些语音数据包串起来,经过解码解压处理后,恢复成原来的语音信号,从而达到由IP网络传送语音的目的。VoIP系统把传统电话的模拟信号转换成计算机可联入因特网传送的IP数据包,同时也将收到的IP数据包转换成声音的模拟电信号。经过VoIP系统的转换及压缩处理,每个普通电话传输速率约占用8~11kbit/s带宽,因此在与普通电信网同样使用传输速率为64kbit/s的带宽时, VoIP线路数是原来的5~8倍。同时,IP技术允许多个用户共用同一带宽资源,改变了传统电话由单个用户独占一个信道的方式,节省了用户使用单独信道的费用。

VoIP的基本结构由网关(GW)和网守(GK)两部分构成。网关的主要功能是信令处理、H.323协议处理、语音编解码和路由协议处理等,对外分别提供与PSTN网连接的中继接口以及与IP网络连接的接口。网守的主要功能是用户认证、地址解析、带宽管理、路由管理、安全管理和区域管理。VoIP的核心与关键设备是VoIP网关。

基于嵌入式技术的VoIP功能实现框图

1、VoIP实现原理框图:(如图1)

2、嵌入式系统中VoIP的工作过程:

① 在单个独立的嵌入式系统内部进行语音通信时,该系统实现功能的过程如下:用户话音脉冲通过SLIC和CODEC电路产生PCM流,载入语音处理器 AC4880XC-C中,通过片内DSP进行语音压缩、成帧(包括地址等用户信息及语音信息),AC4880XC-C再将数据包通过HPI口传送到主系统,完成交换功能后,认定目的地是本系统的另一个用户,将处理过的话音数据包传给AC4880XC-C,AC4880XC-C进行解压缩后,以PCM流返回到CODEC部分,根据目的地址信息驱动目的用户。

② 在嵌入式系统之间进行语音通信时,过程如下:AC4880XC-C将话音数据包通过HPI口传给本系统后,本系统的交换功能认定目的地是另一个嵌入式系统的一个用户,本系统将数据包重组后,通过I/O端口传给目的系统,由目的系统自动完成解压缩,驱动目的用户的功能。

系统设计实现

硬件设计为以下六块组成

1、SLIC(用户线接口电路)部分

采用AMD公司生产的AM79R70PLCC芯片,通过该芯片产生输入、输出话音脉冲和铃音脉冲。

2、CODEC(编解码)部分

采用AMD公司生产的AM79Q021JC编解码芯片,通过该芯片产生的PCM流送到语音处理芯片处理。

3、语音处理部分

作为本系统中的核心部分,语音处理采用以色列AudioCodes公司生产的专用多通道语音处理芯片AC4880XC-C。它具有以下特点:

⊙ 支持ITU的G.711、G.723.1、G.726、G.729A等分组语音处理标准;

⊙ 支持回波抵制和抵消、静音检测和舒适噪音等提高分组语音处理性能的配套模块;

⊙ 高质量坏帧插补;

⊙ 支持2.4"14.4 kbps的T.38和FRF.11的功能传真业务;

⊙ 支持各种信令,如DTMF等;

⊙ 提供语音、传真、数据或信令等PCM高速接口;

⊙ 可选择 或o 律;

⊙ 输入输出增益控制;

⊙ 提供同步HPI、PCM、时钟、存储器以及I/O和仿真测试接口(如图2);

⊙ 144pin,TQFP封装,1.8V内核电压,3.3V芯片电压。

4、CPLD部分

AC4880XC-C采用8位并行的主处理器接口HPI接口与主系统进行数据交换。鉴于嵌入式系统中接口逻辑繁杂,选用CPLD实现接口适配功能。主 CPU可通过CPLD控制实现CODEC 和SLIC部分的功能。

[table][/table]

5、HPI接口部分

本设计中,嵌入式系统CPU与AC4880XC-C通过HPI接口进行数据通信,CPU通过AC4880XC-C片内共享的双口存储器与其片内DSP实现数据交互。HPI接口包括1根8位数据总线和11根控制总线。主系统CPU通过三个寄存器(HPIC、HPIA和HPID)控制AC4880XC-C及访问片内存储空间。HPIC为控制寄存器,用来选择AC4880XC-C的高低字节顺序。HPIA为地址寄存器,用来寻址片内的2K存储空间。HPID为数据寄存器,用来缓存每次读写的两个字节数据,外部CPU以单个Word或块数据访问HPID。以块数据方式访问时,HPIA寄存器自动累加,可减少外部 CPU写HPIA寄存器的开销。AC4880XC-C的内部寄存器和存储器为16位,外部CPU每次访问AC4880XC-C必须以两个字节为基本单位,信号线HI/LO用来选择高低字节,信号HRS1、HRS0指示当前访问的是哪个寄存器。

嵌入式 电路 DSP PLC 仿真 电压 CPLD 总线 PIC ARM 相关文章:

- 嵌入式系统的定义与发展历史(11-15)

- 嵌入式系统亲密接触(11-22)

- 嵌入式系统设计中的USB OTG方案(02-01)

- 嵌入式线控驾驶系统开发过程中设计和测试考虑(02-02)

- 一个典型的嵌入式系统设计和实现 (02-02)

- DDR SDRAM在嵌入式系统中的应用(02-07)