基于单片机控制的带锁相环三路智能同步采集卡设计

时间:07-28

来源:互联网

点击:

电力系统是数据采集系统的主要应用领域之一,随着电力系统进一步朝着“大电网、大容量、大机组”的方向发展,发、输、配电过程要求高度自动化已成为不可逆转的趋势。因此,其对应的“发、输、配”环节对相应的自动装置、继电保护装置、故障检测及诊断装置等性能提出了更新更高的要求。而数据采集子(卡)系统作为这些装置的“排头兵”,其性能直接影响着这些装置的整体性能,同时也在一定程度上影响着整个电力系统运行的“稳定性、安全性”。

电力系统中被测参数的特点:

1)大都是周期性电量;

2)实时性变量;

3)同步性变量——主要指对称三相电压、电流等;

4)变化快、随机性强——主要是指一些干扰性及故障性信号(如:电力传输线上浪涌电流、尖峰电压等),同时现场干扰信号多而复杂。

因此,对数据采集子系统不仅要求结构上应进一步小型化、灵活化、专用和通用的有机结合以适应不同现场信号采集的需要,还要求其应逐步实现“数字化、智能化、自动化”以满足采集系统实现“高精度、高速度、高可靠性、多功能、多参数测量”等高性能采集和处理的要求。基于上述要求和目标,结合电力系统继电保护装置特点,作者在“三路同步采集卡”设计过程中,在系统结构和采集技术上作了大胆的探索和尝试:在系统结构上采用了性价比较为合理的“串并行结构”充分利用单片机体积小、结构简单、现场适应能力强的优点以及其丰富的硬、软件资源及卓越的性能优势,使其实现了系统结构“微型、灵活”及测试过程自动化的要求;而在采集技术上依据被采信号的特点(三路频率相同)引入了锁相环技术实现了对采集信号频率的自动跟踪和系统采集速率的自动变换等;同时采用了软件实现抗干扰的方式——“数字滤波和设置陷阱技术”,从而提高了系统的抗干扰性能。通过测试表明:该“智能采集卡”满足了设计指标的要求,性能稳定且可靠。

1 系统结构及原理

1.1 系统结构图

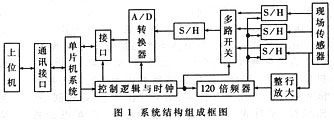

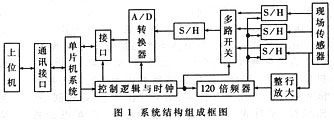

根据系统设计指标及现场测试的需要,本系统采用串并行结构(见图1),同时考虑到远程传输和数据处理的需要,本采集卡利用单片机的串行通讯口并配以相应接口可直接挂接到系统总线上以实现与上位机的实时通讯。

1.2 系统基本原理

与通常的数据采集系统相比,该系统中引入了锁相环技术以实现三路信号的同步采集和采集速率的自动调节;另通过多路开关的有机组合在实现三路分时转换的同时也实现了双极性A/D转换器量程的自动转换,从而提高了系统的灵活性和适应能力。

1.2.1 锁相环技术

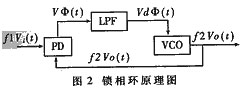

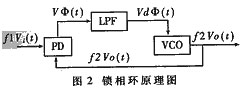

锁相环技术也称自动相位控制技术,于20世纪30年代发展起来,现已广泛应用于通信、电子、测控等领域,其结构组成见图2,主要由相位比较器(PD亦称鉴相器),低通滤波器(LPF),压控振荡器(VCO)组成。

其基本原理如下:PD将Vi(t)与Vo(t)的相位进行比较,产生一个与二者相位差成正比的误差电压VΦ(t),VΦ(t)再经由LPF滤波(滤除高频分量),得到控制电压Vd(t),并加到VCO的控制端使VCO振荡器输出频率f2向f1靠拢,直至Δf=0,即f2=f1,从而实现Vi(t)、Vo(t)两信号的频率相同而相位差保持恒定(同步),即实现频率自动跟踪和相位锁定。

1.2.2 集成锁相环CD4046

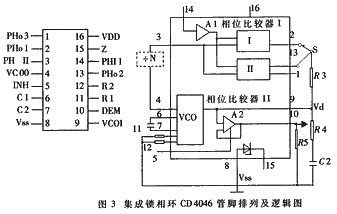

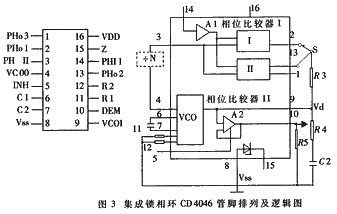

锁相环技术尽管出现于20世纪30年代,但由于组成锁相环的是一些分离元件,因此使其成本高且性能低;同时由于其它一些技术等因素的影响,极大地限制了其大范围的应用(早期主要应用于电视接收机的行扫描电路和供色度信号解调的副载波振荡电路等),直到20世纪70年代初期,随着微电子技术及相关技术的快速发展,使得制作低成本、高性能集成锁相环电路/芯片得以实现。现在,锁相环技术得到了快速发展,如今已广泛应用于工业、通信等领域。作为目前国内外最具代表性也是最常见的集成锁相环芯片CD4046,由于其集成度高、性价比高、多功能、易组合等优点而得到了广泛使用,其管角排列及逻辑图见图3。

从图3可知:VCO的输出可以经由一除法器进行N分频后,再送至相位比较器Ⅰ,并进而与VI进行相位比较,最后使f2′=f1,二者的相位差恒定,从而实现锁相。由于f2′=f2/N=f1,可推得:f2=Nf1,由此表明:尽管从局部看使用除法器完成的是分频,但就锁相环整体而言却是实现N倍频。本文作者正是利用CD4046的这一特性并配以三片可编程计数器芯片MC14522构成120倍频器(见图4),从而实现三路信号在一个周波内完成120点同步采集。

电力系统中被测参数的特点:

1)大都是周期性电量;

2)实时性变量;

3)同步性变量——主要指对称三相电压、电流等;

4)变化快、随机性强——主要是指一些干扰性及故障性信号(如:电力传输线上浪涌电流、尖峰电压等),同时现场干扰信号多而复杂。

因此,对数据采集子系统不仅要求结构上应进一步小型化、灵活化、专用和通用的有机结合以适应不同现场信号采集的需要,还要求其应逐步实现“数字化、智能化、自动化”以满足采集系统实现“高精度、高速度、高可靠性、多功能、多参数测量”等高性能采集和处理的要求。基于上述要求和目标,结合电力系统继电保护装置特点,作者在“三路同步采集卡”设计过程中,在系统结构和采集技术上作了大胆的探索和尝试:在系统结构上采用了性价比较为合理的“串并行结构”充分利用单片机体积小、结构简单、现场适应能力强的优点以及其丰富的硬、软件资源及卓越的性能优势,使其实现了系统结构“微型、灵活”及测试过程自动化的要求;而在采集技术上依据被采信号的特点(三路频率相同)引入了锁相环技术实现了对采集信号频率的自动跟踪和系统采集速率的自动变换等;同时采用了软件实现抗干扰的方式——“数字滤波和设置陷阱技术”,从而提高了系统的抗干扰性能。通过测试表明:该“智能采集卡”满足了设计指标的要求,性能稳定且可靠。

1 系统结构及原理

1.1 系统结构图

根据系统设计指标及现场测试的需要,本系统采用串并行结构(见图1),同时考虑到远程传输和数据处理的需要,本采集卡利用单片机的串行通讯口并配以相应接口可直接挂接到系统总线上以实现与上位机的实时通讯。

1.2 系统基本原理

与通常的数据采集系统相比,该系统中引入了锁相环技术以实现三路信号的同步采集和采集速率的自动调节;另通过多路开关的有机组合在实现三路分时转换的同时也实现了双极性A/D转换器量程的自动转换,从而提高了系统的灵活性和适应能力。

1.2.1 锁相环技术

锁相环技术也称自动相位控制技术,于20世纪30年代发展起来,现已广泛应用于通信、电子、测控等领域,其结构组成见图2,主要由相位比较器(PD亦称鉴相器),低通滤波器(LPF),压控振荡器(VCO)组成。

其基本原理如下:PD将Vi(t)与Vo(t)的相位进行比较,产生一个与二者相位差成正比的误差电压VΦ(t),VΦ(t)再经由LPF滤波(滤除高频分量),得到控制电压Vd(t),并加到VCO的控制端使VCO振荡器输出频率f2向f1靠拢,直至Δf=0,即f2=f1,从而实现Vi(t)、Vo(t)两信号的频率相同而相位差保持恒定(同步),即实现频率自动跟踪和相位锁定。

1.2.2 集成锁相环CD4046

锁相环技术尽管出现于20世纪30年代,但由于组成锁相环的是一些分离元件,因此使其成本高且性能低;同时由于其它一些技术等因素的影响,极大地限制了其大范围的应用(早期主要应用于电视接收机的行扫描电路和供色度信号解调的副载波振荡电路等),直到20世纪70年代初期,随着微电子技术及相关技术的快速发展,使得制作低成本、高性能集成锁相环电路/芯片得以实现。现在,锁相环技术得到了快速发展,如今已广泛应用于工业、通信等领域。作为目前国内外最具代表性也是最常见的集成锁相环芯片CD4046,由于其集成度高、性价比高、多功能、易组合等优点而得到了广泛使用,其管角排列及逻辑图见图3。

从图3可知:VCO的输出可以经由一除法器进行N分频后,再送至相位比较器Ⅰ,并进而与VI进行相位比较,最后使f2′=f1,二者的相位差恒定,从而实现锁相。由于f2′=f2/N=f1,可推得:f2=Nf1,由此表明:尽管从局部看使用除法器完成的是分频,但就锁相环整体而言却是实现N倍频。本文作者正是利用CD4046的这一特性并配以三片可编程计数器芯片MC14522构成120倍频器(见图4),从而实现三路信号在一个周波内完成120点同步采集。

自动化 电压 电流 单片机 总线 电子 比较器 滤波器 振荡器 电路 嵌入式 放大器 C语言 相关文章:

- 基于RGB三基色原理的手持式色度仪的设计(05-06)

- 城市和工业污水处理自动化解决方案(03-22)

- 基于以太网技术的太阳能光伏系统监控(11-30)

- STM32-F2系列微控制器 能够满足工厂自动化苛刻要求的高速Cortex-M3微控制器(03-18)

- 基于GPIB/VXI/IEEE1394总线的板级电路功能测试和故障诊断自动化测试系统(10-15)

- 构建可由电池供电运行数十年的楼宇自动化系统(06-20)