基于ARM核的Intel XScale嵌入式系统

时间:07-07

来源:互联网

点击:

1 简 介

Intel XScale微体系结构提供了一种全新的、高性价比、低功耗且基于ARMv5TE体系结构的解决方案,支持16位Thumb指令和DSP扩充。基于XScale技术开发的微处理器,可用于手机、便携式终端(PDA)、网络存储设备、骨干网(BackBone)路由器等。Intel PXA250微处理器芯片就是一款集成了32位Intel XScale 处理器核、多通信信道、LCD控制器、增强型存储控制器和PCMCIA/CF控制器以及通用I/O口的高度集成的应用处理器。 Intel XScale处理器的处理速度是Intel StrongARM处理速度的两倍,其内部结构也有了相应的变化:

数据Cache的容量从8KB增加到32KB;

指令Cache的容量从16KB增加到32KB;

微小数据Cache的容量从512B增加到2KB;

为了提高指令的执行速度,超级流水线结构由5级增至7级;

新增乘/加法器MAC和特定的DSP型协处理器CP0,以提高对多媒体技术的支持;

动态电源管理,使XScale处理器的时钟可达1GHz、功耗1.6W,并能达到1200MIPS。

XScale微处理器架构经过专门设计,核心采用了英特尔先进的0.18μm工艺技术制造;具备低功耗特性,适用范围从0.1mW~1.6W。同时,它的时钟工作频率将接近1GHz。 XScale与StrongARM相比,可大幅降低工作电压并且获得更高的性能。具体来讲,在目前的StrongARM中,在1.55V下可以获得133MHz的工作频率,在2.0V下可以获得206MHz的工作频率;而采用XScale后,在0.75V时工作频率达到150MHz,在1.0V时工作频率可以达到400MHz,在1.65V下工作频率则可高达800MHz。超低功率与高性能的组合使Intel XScale适用于广泛的互联网接入设备,在因特网的各个环节中,从手持互联网设备到互联网基础设施产品,Intel XScale都表现出了令人满意的处理性能。

2 PXA250的结构及特点

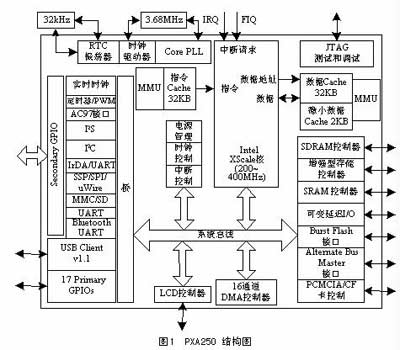

Intel XScale PXA250结构框图如图1所示。

2.1 PXA250处理器的主要特点

(1)高性能

低功耗,高性能的32位Intel XScale处理器内核,工作频率高达400MHZ;

兼容ARMv5TE架构;

采用7级超级流水线结构;

支持多媒体处理技术,采用40位累加器和16位乘法器,以增强对音频和视频的解码能力;

提供支持同步Intel StrataFlash存储器的高性能分帧和分页模式接口。

(2)低功耗

多电源管理模式;

32KB数据和32KB指令Cache;

2KB的微小数据Cache;

支持2.5V和3.3V的存储器。

(3)I/O扩展

100MHz存储器总线,6个静态存储空间(16或32位ROM(SMROM)/Flash/SRAM),4个动态存储分区(16或32位SDRAM);

支持2个PCMCIA 或 Compact Flash槽。

(4)外围控制模块

16通道可配置DMA控制器;

LCD控制器,独有的支持对快变彩屏的DMA方式;

920kbps Bluetooth接口;

串行端口(IrDA、I2C、I2S、AC97、3个UARTs、SPI 和SSP);

USB接口;

支持MMC/SD卡。

(5)时钟控制

五种时钟源:

32.768kHz振荡器;

3.6864MHz振荡器;

可编程的内核锁相环;

95.85MHz外围固定频率锁相环;

147.46MHz固定频率锁相环。

(6)电源管理

运行模式(正常处理模式)、Turbo模式(运行于400MHZ)、空闲模式(下电)、睡眠模式(下电)。

(7)封装形式

17mm×17 mm 256脚PBGA封装。

2.2 Intel XScale内核

Intel XScale CPU内核采用带有一个增强型存储器管道的超级流水线RISC处理器架构的体系结构。这款新型高性能、低功耗的微构架兼容ARMv5TE ISA指令集(不支持浮点指令集)。这种微构架在ARM核的周围提供了指令与数据存储器管理单元,指令、数据和微小数据Cache,写缓冲、全缓冲、挂起缓冲和分支目标缓冲器,电源管理,性能监控、调试和JTAG单元以及协处理器接口,MAC协处理器和内核存储总线。

超级流水线结构是由整型管道、存储器管道和MAC管道构成。整型管道包括7级流水线结构,取指令1(分支目标缓冲器)→取指令2→译码→寄存/移位→ALU实现→状态执行→回复;存储器管道除包括整型管道的前5级外,后接3个高速缓存,数据Cache1、数据Cache2和数据回复Cache,共8级流水线结构;MAC管道是6~9级的流水线结构,包括整型管道的前4级和4级MAC段,以及一个数据回复Cache,其中MAC2-4的选通由数据决定。流水线结构级数越多越能提高指令的执行速度,使用分支目标缓冲器的目的在于成功的预知分支指令的 结果。128个入口的分支目标缓冲器的每个入口都包含了分支指令的地址、与分支指令相联系的目标地址以及该分支的执行情况,它由协处理器15使能。分支目标缓冲器的使用旨在避免超级流水线结构中的分支延迟。

PXA250 CPU的MM(IMMU和DMMU)均提供了一个32项的转换旁路缓存器(ITLB和DTLB),它们的每一项均可映射存储器中的段、大页和小页。为了保证内核周期的存取指令和数据,PXA250包含了1个32KB的指令Cache和1个32KB的数据Cache。另外,为了避免数据Cache内数据流存取的频繁变化,还提供了1个2KB的微小数据Cache。指令和数据Cache都是具有32个入口和32路相联的Cache,每路均包含1个标志地址,32字节的高速缓存队列和1个有效位,采用循环方式进行刷新存储。微小数据Cache是1个具有32个入口和2路相联的Cache,同样采用循环方式进行刷新存储。

PXA250内核还提供了4个入口的全缓冲和挂起缓冲,用于提升内核性能,与数据Cache和微小数据Cache协同工作。此外,1个8入口的写缓冲,每个入口可保存16字节,它从内核、数据Cache或微小数据Cache中得到数据,在系统总线选通前,暂存数据。

2.3 系统控制功能

PXA250的系统控制模块提供了实时时钟、看门狗及间隔定时器、功率管理控制器、中断控制器、复位控制器和2个片上振荡器。该系统定时器支持源自SA-11x0处理器的定时器单元,OS定时器使用3.6864MHz振荡器,包含了4个定时匹配寄存器(OSMR)、1个定时状态寄存器(OSSR)和1个定时中断使能寄存器(OIER)。看门狗定时中断可以通过激活OS定时看门狗使能寄存器(OWER)来实现。

中断控制器处理的所有中断源,有两个中断类型:中断请求(IRQ)和快速中断请求(FIQ)。中断控制器可以根据掩码寄存器的值,允许CPU被中断或保持预中断。中断控制器中的每一个寄存器都是1比特映射,并且每一比特均被预先分配给不同的中断源。

2.4 时钟和电源管理

为了达到处理性能和能量消耗之间比例的最优化,用时钟和电源管理器来控制不同模块的时钟频率并处理不同能量管理操作模式之间的转化。时钟和电源管理器为每一个外设提供了固定的时钟,并且为LCD控制器、存储器控制器和CPU提供了可编程的频率时钟,这些时钟均来自内部锁相环时钟源。时钟管理器还可通过关闭不用设备的时钟来减少功率损耗。

电源管理提供了四种工作模式:Turbo模式、运行模式、空闲模式和睡眠模式。Turbo模式下,CPU核运行在峰值频率,为避免内核对外部存储器的等待时间,在该模式下,很少对外部存储器进行存取;运行模式下,CPU核运行于正常标准频率,可以假定内核不断地对外部存储器进行存取,运行速率的减慢对于性能与功耗的最佳平衡是有利的;在空闲模式下,暂停到CPU的时钟,但是使能到外围器件的时钟;睡眠模式下,整个系统将处于最低功耗状态,要唤醒睡眠状态必须重新启动系统。

2.5 存储器和PCMCIA/Compact Flash控制模块

PXA250处理器的外部存储器总线接口支持同步动态存储器(SDRAM)、同步和异步分页模式段、页模式闪存、同步掩码只读存储器(SMROM)、页模式ROM、SRAM、静态段支持可变等待时间的I/O设备(VLIO)、16位的PC卡扩展存储器和Compact Flash。存储器的类型可通过存储器接口配置寄存器决定。

2.6 外围控制模块

PXA250处理器定义了16个通道的DMA控制器。它可响应内部和外部设备的请求,完成数据从主存储器中读出与写入。DMAC用于外围设备与存储系统之间的数据传输。

LCD控制器提供了支持双扫描无源阵列彩显(DSTN,俗称伪彩)或有源阵列彩显(TFT,俗称真彩)屏的接口,并支持单色和多色素格式。它拥有自己独立的双通道DMA控制器,两路通道分别用于单面板和双面板显示。最大支持显示分辨率为1024×1024像素,推荐最高分辨率为800×600像素。在无源单色模式下,最高支持256级灰度。对于彩色显示,不管有源还是无源模式,最高均支持65536种颜色。LCD控制器将帧缓存中的像素编码值,对应于16位宽的256个入口的调色板RAM,根据数据宽度决定彩色的数量。

PXA250处理器支持的串口包括:基于通用串行总线1.1版本的USB客户服务模块接口,它最高支持16个端点外挂,并提供了1个48MHz的内部时钟;3个通用异步收发口(UART),最高速率230Kbps的全功能UART(完备的握手信号),最高速率921Kbps蓝牙UART和标准UART;高速红外通信口(FICP)半双工,速率4Mbps,执行4PPM标准;AC97控制器支持AC97 2.0修订版本的多媒体数字信号编解码器,AC97控制器对于立体PCM输入输出,Modem输入输出和单一的麦克风输入都提供了单独的16位通道;I2S控制器为数字立体声标准I2S多媒体数字信号编解码器提供了串行连接,复用AC97控制器引脚;I2C总线接口提供了2个引脚的通用串行通信端口,2个引脚分别用于数据地址和时钟;另外,提供了2个支持MMC或SPI协议,高达20Mbps串行数据传输的MMC卡接口和一个SSP接口。SSP逻辑接口支持National Microwire协议、Texas Instruments协议、同步串行协议(SSP)和Motorola SPI协议,所有这些协议都用于A/D转换、音频和电信多媒体数字信号编解码器和其它满足串行数据传输协议的设备。

3 研华最新推出的XScale单板计算机PCM-7210

PCM-7210是一款集成Intel XScale低功耗RISC处理器PXA250的单板计算机。它由一块支撑板和一块CPU板构成,在CPU板上集成了处理器PXA250、64MB的SDRAM和32MB的Flash存储器,其它的外围器件均置于支撑板之上,包括10Mbps以太网接口,4个全功能RS-232和1个RS-485串行接口,AC97音频接口,2个USB主机端和1个客户端,数字I/O引脚和CF/PCMCIA扩展插槽。此外,还有支持LCD/CRT显示的接口以及智能电源接口。PCM-7210功能框图如图2所示。

Intel XScale微体系结构提供了一种全新的、高性价比、低功耗且基于ARMv5TE体系结构的解决方案,支持16位Thumb指令和DSP扩充。基于XScale技术开发的微处理器,可用于手机、便携式终端(PDA)、网络存储设备、骨干网(BackBone)路由器等。Intel PXA250微处理器芯片就是一款集成了32位Intel XScale 处理器核、多通信信道、LCD控制器、增强型存储控制器和PCMCIA/CF控制器以及通用I/O口的高度集成的应用处理器。 Intel XScale处理器的处理速度是Intel StrongARM处理速度的两倍,其内部结构也有了相应的变化:

数据Cache的容量从8KB增加到32KB;

指令Cache的容量从16KB增加到32KB;

微小数据Cache的容量从512B增加到2KB;

为了提高指令的执行速度,超级流水线结构由5级增至7级;

新增乘/加法器MAC和特定的DSP型协处理器CP0,以提高对多媒体技术的支持;

动态电源管理,使XScale处理器的时钟可达1GHz、功耗1.6W,并能达到1200MIPS。

XScale微处理器架构经过专门设计,核心采用了英特尔先进的0.18μm工艺技术制造;具备低功耗特性,适用范围从0.1mW~1.6W。同时,它的时钟工作频率将接近1GHz。 XScale与StrongARM相比,可大幅降低工作电压并且获得更高的性能。具体来讲,在目前的StrongARM中,在1.55V下可以获得133MHz的工作频率,在2.0V下可以获得206MHz的工作频率;而采用XScale后,在0.75V时工作频率达到150MHz,在1.0V时工作频率可以达到400MHz,在1.65V下工作频率则可高达800MHz。超低功率与高性能的组合使Intel XScale适用于广泛的互联网接入设备,在因特网的各个环节中,从手持互联网设备到互联网基础设施产品,Intel XScale都表现出了令人满意的处理性能。

2 PXA250的结构及特点

Intel XScale PXA250结构框图如图1所示。

|

2.1 PXA250处理器的主要特点

(1)高性能

低功耗,高性能的32位Intel XScale处理器内核,工作频率高达400MHZ;

兼容ARMv5TE架构;

采用7级超级流水线结构;

支持多媒体处理技术,采用40位累加器和16位乘法器,以增强对音频和视频的解码能力;

提供支持同步Intel StrataFlash存储器的高性能分帧和分页模式接口。

(2)低功耗

多电源管理模式;

32KB数据和32KB指令Cache;

2KB的微小数据Cache;

支持2.5V和3.3V的存储器。

(3)I/O扩展

100MHz存储器总线,6个静态存储空间(16或32位ROM(SMROM)/Flash/SRAM),4个动态存储分区(16或32位SDRAM);

支持2个PCMCIA 或 Compact Flash槽。

(4)外围控制模块

16通道可配置DMA控制器;

LCD控制器,独有的支持对快变彩屏的DMA方式;

920kbps Bluetooth接口;

串行端口(IrDA、I2C、I2S、AC97、3个UARTs、SPI 和SSP);

USB接口;

支持MMC/SD卡。

(5)时钟控制

五种时钟源:

32.768kHz振荡器;

3.6864MHz振荡器;

可编程的内核锁相环;

95.85MHz外围固定频率锁相环;

147.46MHz固定频率锁相环。

(6)电源管理

运行模式(正常处理模式)、Turbo模式(运行于400MHZ)、空闲模式(下电)、睡眠模式(下电)。

(7)封装形式

17mm×17 mm 256脚PBGA封装。

2.2 Intel XScale内核

Intel XScale CPU内核采用带有一个增强型存储器管道的超级流水线RISC处理器架构的体系结构。这款新型高性能、低功耗的微构架兼容ARMv5TE ISA指令集(不支持浮点指令集)。这种微构架在ARM核的周围提供了指令与数据存储器管理单元,指令、数据和微小数据Cache,写缓冲、全缓冲、挂起缓冲和分支目标缓冲器,电源管理,性能监控、调试和JTAG单元以及协处理器接口,MAC协处理器和内核存储总线。

超级流水线结构是由整型管道、存储器管道和MAC管道构成。整型管道包括7级流水线结构,取指令1(分支目标缓冲器)→取指令2→译码→寄存/移位→ALU实现→状态执行→回复;存储器管道除包括整型管道的前5级外,后接3个高速缓存,数据Cache1、数据Cache2和数据回复Cache,共8级流水线结构;MAC管道是6~9级的流水线结构,包括整型管道的前4级和4级MAC段,以及一个数据回复Cache,其中MAC2-4的选通由数据决定。流水线结构级数越多越能提高指令的执行速度,使用分支目标缓冲器的目的在于成功的预知分支指令的 结果。128个入口的分支目标缓冲器的每个入口都包含了分支指令的地址、与分支指令相联系的目标地址以及该分支的执行情况,它由协处理器15使能。分支目标缓冲器的使用旨在避免超级流水线结构中的分支延迟。

PXA250 CPU的MM(IMMU和DMMU)均提供了一个32项的转换旁路缓存器(ITLB和DTLB),它们的每一项均可映射存储器中的段、大页和小页。为了保证内核周期的存取指令和数据,PXA250包含了1个32KB的指令Cache和1个32KB的数据Cache。另外,为了避免数据Cache内数据流存取的频繁变化,还提供了1个2KB的微小数据Cache。指令和数据Cache都是具有32个入口和32路相联的Cache,每路均包含1个标志地址,32字节的高速缓存队列和1个有效位,采用循环方式进行刷新存储。微小数据Cache是1个具有32个入口和2路相联的Cache,同样采用循环方式进行刷新存储。

PXA250内核还提供了4个入口的全缓冲和挂起缓冲,用于提升内核性能,与数据Cache和微小数据Cache协同工作。此外,1个8入口的写缓冲,每个入口可保存16字节,它从内核、数据Cache或微小数据Cache中得到数据,在系统总线选通前,暂存数据。

2.3 系统控制功能

PXA250的系统控制模块提供了实时时钟、看门狗及间隔定时器、功率管理控制器、中断控制器、复位控制器和2个片上振荡器。该系统定时器支持源自SA-11x0处理器的定时器单元,OS定时器使用3.6864MHz振荡器,包含了4个定时匹配寄存器(OSMR)、1个定时状态寄存器(OSSR)和1个定时中断使能寄存器(OIER)。看门狗定时中断可以通过激活OS定时看门狗使能寄存器(OWER)来实现。

中断控制器处理的所有中断源,有两个中断类型:中断请求(IRQ)和快速中断请求(FIQ)。中断控制器可以根据掩码寄存器的值,允许CPU被中断或保持预中断。中断控制器中的每一个寄存器都是1比特映射,并且每一比特均被预先分配给不同的中断源。

2.4 时钟和电源管理

为了达到处理性能和能量消耗之间比例的最优化,用时钟和电源管理器来控制不同模块的时钟频率并处理不同能量管理操作模式之间的转化。时钟和电源管理器为每一个外设提供了固定的时钟,并且为LCD控制器、存储器控制器和CPU提供了可编程的频率时钟,这些时钟均来自内部锁相环时钟源。时钟管理器还可通过关闭不用设备的时钟来减少功率损耗。

电源管理提供了四种工作模式:Turbo模式、运行模式、空闲模式和睡眠模式。Turbo模式下,CPU核运行在峰值频率,为避免内核对外部存储器的等待时间,在该模式下,很少对外部存储器进行存取;运行模式下,CPU核运行于正常标准频率,可以假定内核不断地对外部存储器进行存取,运行速率的减慢对于性能与功耗的最佳平衡是有利的;在空闲模式下,暂停到CPU的时钟,但是使能到外围器件的时钟;睡眠模式下,整个系统将处于最低功耗状态,要唤醒睡眠状态必须重新启动系统。

2.5 存储器和PCMCIA/Compact Flash控制模块

PXA250处理器的外部存储器总线接口支持同步动态存储器(SDRAM)、同步和异步分页模式段、页模式闪存、同步掩码只读存储器(SMROM)、页模式ROM、SRAM、静态段支持可变等待时间的I/O设备(VLIO)、16位的PC卡扩展存储器和Compact Flash。存储器的类型可通过存储器接口配置寄存器决定。

2.6 外围控制模块

PXA250处理器定义了16个通道的DMA控制器。它可响应内部和外部设备的请求,完成数据从主存储器中读出与写入。DMAC用于外围设备与存储系统之间的数据传输。

LCD控制器提供了支持双扫描无源阵列彩显(DSTN,俗称伪彩)或有源阵列彩显(TFT,俗称真彩)屏的接口,并支持单色和多色素格式。它拥有自己独立的双通道DMA控制器,两路通道分别用于单面板和双面板显示。最大支持显示分辨率为1024×1024像素,推荐最高分辨率为800×600像素。在无源单色模式下,最高支持256级灰度。对于彩色显示,不管有源还是无源模式,最高均支持65536种颜色。LCD控制器将帧缓存中的像素编码值,对应于16位宽的256个入口的调色板RAM,根据数据宽度决定彩色的数量。

PXA250处理器支持的串口包括:基于通用串行总线1.1版本的USB客户服务模块接口,它最高支持16个端点外挂,并提供了1个48MHz的内部时钟;3个通用异步收发口(UART),最高速率230Kbps的全功能UART(完备的握手信号),最高速率921Kbps蓝牙UART和标准UART;高速红外通信口(FICP)半双工,速率4Mbps,执行4PPM标准;AC97控制器支持AC97 2.0修订版本的多媒体数字信号编解码器,AC97控制器对于立体PCM输入输出,Modem输入输出和单一的麦克风输入都提供了单独的16位通道;I2S控制器为数字立体声标准I2S多媒体数字信号编解码器提供了串行连接,复用AC97控制器引脚;I2C总线接口提供了2个引脚的通用串行通信端口,2个引脚分别用于数据地址和时钟;另外,提供了2个支持MMC或SPI协议,高达20Mbps串行数据传输的MMC卡接口和一个SSP接口。SSP逻辑接口支持National Microwire协议、Texas Instruments协议、同步串行协议(SSP)和Motorola SPI协议,所有这些协议都用于A/D转换、音频和电信多媒体数字信号编解码器和其它满足串行数据传输协议的设备。

3 研华最新推出的XScale单板计算机PCM-7210

PCM-7210是一款集成Intel XScale低功耗RISC处理器PXA250的单板计算机。它由一块支撑板和一块CPU板构成,在CPU板上集成了处理器PXA250、64MB的SDRAM和32MB的Flash存储器,其它的外围器件均置于支撑板之上,包括10Mbps以太网接口,4个全功能RS-232和1个RS-485串行接口,AC97音频接口,2个USB主机端和1个客户端,数字I/O引脚和CF/PCMCIA扩展插槽。此外,还有支持LCD/CRT显示的接口以及智能电源接口。PCM-7210功能框图如图2所示。

ARM DSP LCD 电源管理 MIPS 电压 总线 USB 振荡器 看门狗 蓝牙 红外 解码器 相关文章:

- 基于ARM的除法运算优化策略(01-14)

- 基于ARM的CAN总线智能节点的设计(01-24)

- ARM基础知识教程五 (02-08)

- ARM基础知识教程六(02-08)

- ARM基础知识教程七(02-08)

- ARM基础知识教程八(02-08)