彩色液晶显示驱动控制器SSD1780及其应用

时间:06-10

来源:互联网

点击:

SSD1780是晶门科技公司新推出的一种用于点阵显示系统的单片CMOS彩色STN-LCD驱动控制器。它由393个高压驱动输出引脚可驱动最大104RGB段+80行+1行图标。

SSD1780由312×8×4位的图形显示RAM(GDDRAM)组成。数据/命令可以通过8位6800/8080并行接口或3/4线SPI接口传送。嵌入了DC-DC变换器、片内振荡器和偏压驱动器使得外接元件数量减少。先进的设计、低功耗工作方式、稳定的操作电压使得SSD1780特别适合于需要小体积和长操作时间的便携式电池供电产品的应用如移动电话、PDA等。

1. 基本特点及引脚功能

1.1 基本特点

电源1.8~3.6V,LCD驱动电压13.5V

低功耗睡眠方式,最大显示尺寸104RGB列×80列+1行图标

显示色彩256色或4096色图形显示

256色位置控制及RGB显示控制

8位6800/8080系列并行接口,3线/4线SPI

片内312×81×4=101088位图形显示RAM

通过软件选择屏幕中心、上、下屏幕及全屏滚动

可选片内电压发生器或外接LCD驱动电源

包含内部飞电容的片内偏压发生器

驱动占空比可编程为1/8─1/81

64级内部对比度控制

LCD驱动电压温度补偿系数可编程

片内振荡器

2D加速器

封装形式COG/COF

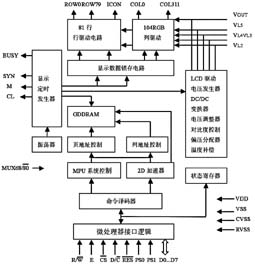

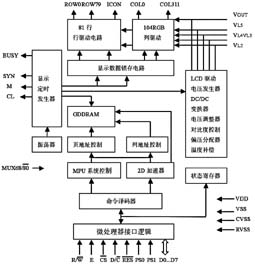

1.2 引脚功能、结构方框图如图1所示。

PS0、PS1:总线接口方式选择如表1。

RES:复位信号输入,最小复位脉宽10μs。

CS:片选信号输入,低有效。

R/W(WR):与6800系列CPU接口时用于读写选择,1=读,0=写。

与8080系列CPU接口时用于写信号,低有效。

E/RD:与6800CPU接口时,是使能信号,高有效;

与8080CPU接口时,是写信号输入,低有效。

D7-D0:并行接口方式,双向数据总线,D7是MSB,D0是LSB。D7是串行数据输入SDA,D6是串行时钟输入SCK。

D/C:数据或命令选择引脚。=1时,数据总线上的信息当作显示数据;=0时,数据总线上的信息发送到命令寄存器。

BUSY:对RAM缓冲器的读写操作和执行图形命令时,此引脚为高电平表示忙。

VDD:系统逻辑部分电源。

VCI: 内部DC-DC变换器的参考电压。产生的VCC电压等于多倍系数(3X、4X、5X、6X)乘以VCI。

VSS:逻辑地

CVSS:模拟地

VOUT:芯片最大供电电压,可由外部供给或通过内部DC-DC变换器产生。

VL5、VL4、VL3、VL2:LCD驱动电压。可由外部提供或内部偏压驱动器产生,它们具有以下关系:

VOUT>VL5>VL4>VL3>VL2>VSS。

ROW0-ROW79:提供给LCD屏的行(公共极)驱动信号。

COL0—COL311:提供给LCD屏的列(段)驱动信号。红绿蓝信息同时从段输出端发出。当处于睡眠或闲置方式时,这些引脚输出电平是VDD。

ICON:提供至图标行(公共极)的驱动信号。

MUX/80 :用于LCD驱动器的复用比率。

=VDD时,COM0-COM33映射到ROW0-ROW33

COM46-COM79映射到ROW34-ROW67

=VSS时,COM0-COM79映射到ROW0-ROW79。

2. 功能及内部结构

2.1 微处理器接口逻辑

由驱动6800系列MPU、8080系列MPU、3线和4线SPI接口的三个功能方框组成。通过PS0、PS1脚来选择不同的接口。

a) 与6800系列CPU并行接口

由8位双向数据脚 D7-D0、R/W、D/C、E、CS组成。 R/W脚输入高指示根据D/C输入的状态从图形显示RAM(GDDRAM)或状态寄存器进行读操作。当CS=0 且 E=1E脚输入作为数据锁存信号。为了使MCU和GDDRAM 的操作频率相匹配,一些管道处理在内部执行,因此第一个有效显示数据读之前需要插入虚拟读。

b) 与8080系列CPU并行接口

由8位双向数据脚 D7-D0、RD、WR、D/C、CS组成。假如CS是低电平且RD为低,RD输入作为读数据锁存信号。无论是从GDRRAM读显示数据还是从状态寄存器读状态都需要受D/C脚的控制。假如CS是低电平且WR为低,WR输入作为写数据锁存信号。无论是写显示数据到GDDRAM还是将命令写入命令寄存器都需要受D/C脚的控制。第一有效数据读之前也需要一次虚拟读。

c) 四线SPI

四线串行外设接口(SPI)由串行时钟SCK、串行数据SDA、D/C、CS组成。按照位7、位6.....位0的次序在SCK的每一个上升沿由SDA脚移入八位的移位寄存器。在第八个时钟的上沿采样D/C脚的状态以确定移位寄存器中的数据是写入显示数据RAM还是写入命令寄存器。

d) 三线SPI

三线SPI接口与四线接口类似只是不使用D/C脚。按照D/C位、D7....D0的次序在每第九个时钟时九位数据一起移进移位寄存器。D/C位(连续数据的首位)确定移位寄存器中的连续数据字节是写入显示数据RAM(D/C=1)还是写入命令寄存器(D/C=0)。

2.2 命令译码器:这个模块确定输入的数据是被解释成数据还是命令。根据D/C脚的输入电平数据被指向到这个模块中。若D/C=1,数据被写入GDDRAM。

D/C=0,数据解释为命令并译码,译码命令将写入对应的命令寄存器中。

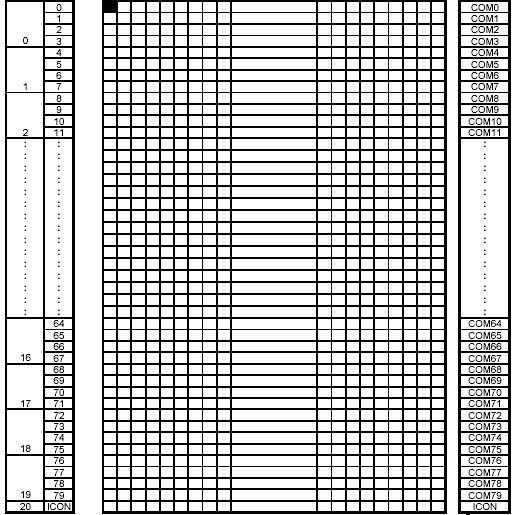

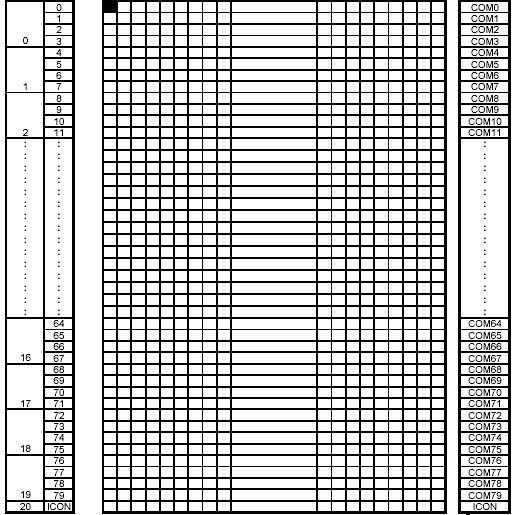

2.3 图形显示数据RAM(GDDRAM):GDDRAM是一个保持被显示位类型的位映射静态RAM、RAM的大小是101088位=104RGB×81×4,如图2所示。可以用软件重新选择映射段和公共极的输出。四页形成一个RAM地址块并存入GDDRAM中。每块形成滚动地址的基本单元。通过软件编程来实现屏幕的滚动。为了容易存取RGB数据,八位彩色数据(R 3bit、G 3bit、B 2bit)被转换为四位数据(P10、P11、P12、P13),这四位数据被存进GDDRAM。例如数据按照设置的灰度值被定位于合适的RAM位置。

2.4 LCD驱动电压发生器和调整器:这个模块产生LCD所需要的显示输出电压。接受单电源输入并产生必需的偏压。由以下部分所组成:3X、4X、5X、6X DC/DC变换器;偏压分配器;对比度控制;偏压比选择;温度补偿电路。

2.5 振荡电路:片内低功耗RC振荡电路,产生DC/DC变换器、显示定时发生器的时钟。

2.6 显示数据锁存:执行显示信息的锁存。这些锁存器保持数据,将反馈到HV缓冲器和电平选择器到输出所需的电平。

2.7 HV缓冲单元(电平转换器):这个模块嵌入在段/公共极驱动电路中。HV缓冲单元起电平转换器的作用。将低电压输出信号转化为所需的驱动电压。通过参考来自显示定时发生器的内部FRM时钟的输出被转换。电压级别通过与内部M信号同步的电平选择器给定。

2.8 电平选择器:这个模块嵌入在段/公共极驱动电路中。电平选择器是显示同步的一个控制。显示电压级别可以分离成两相且使用不同的周期。同步是重要的因为它选择需要的LCD电压级别到依次输出COM或SEG波形的HV缓冲单元。

SSD1780由312×8×4位的图形显示RAM(GDDRAM)组成。数据/命令可以通过8位6800/8080并行接口或3/4线SPI接口传送。嵌入了DC-DC变换器、片内振荡器和偏压驱动器使得外接元件数量减少。先进的设计、低功耗工作方式、稳定的操作电压使得SSD1780特别适合于需要小体积和长操作时间的便携式电池供电产品的应用如移动电话、PDA等。

1. 基本特点及引脚功能

1.1 基本特点

电源1.8~3.6V,LCD驱动电压13.5V

低功耗睡眠方式,最大显示尺寸104RGB列×80列+1行图标

显示色彩256色或4096色图形显示

256色位置控制及RGB显示控制

8位6800/8080系列并行接口,3线/4线SPI

片内312×81×4=101088位图形显示RAM

通过软件选择屏幕中心、上、下屏幕及全屏滚动

可选片内电压发生器或外接LCD驱动电源

包含内部飞电容的片内偏压发生器

驱动占空比可编程为1/8─1/81

64级内部对比度控制

LCD驱动电压温度补偿系数可编程

片内振荡器

2D加速器

封装形式COG/COF

1.2 引脚功能、结构方框图如图1所示。

PS0、PS1:总线接口方式选择如表1。

| PS1 | PS0 | MPU接口 |

| L | L | 四线串行外设接口(SPI) |

| L | H | 8位8080并行接口 |

| H | L | 三线SPI(9位SPI) |

| H | H | 8位6800并行接口 |

RES:复位信号输入,最小复位脉宽10μs。

CS:片选信号输入,低有效。

R/W(WR):与6800系列CPU接口时用于读写选择,1=读,0=写。

与8080系列CPU接口时用于写信号,低有效。

E/RD:与6800CPU接口时,是使能信号,高有效;

与8080CPU接口时,是写信号输入,低有效。

D7-D0:并行接口方式,双向数据总线,D7是MSB,D0是LSB。D7是串行数据输入SDA,D6是串行时钟输入SCK。

D/C:数据或命令选择引脚。=1时,数据总线上的信息当作显示数据;=0时,数据总线上的信息发送到命令寄存器。

BUSY:对RAM缓冲器的读写操作和执行图形命令时,此引脚为高电平表示忙。

VDD:系统逻辑部分电源。

VCI: 内部DC-DC变换器的参考电压。产生的VCC电压等于多倍系数(3X、4X、5X、6X)乘以VCI。

VSS:逻辑地

CVSS:模拟地

VOUT:芯片最大供电电压,可由外部供给或通过内部DC-DC变换器产生。

VL5、VL4、VL3、VL2:LCD驱动电压。可由外部提供或内部偏压驱动器产生,它们具有以下关系:

VOUT>VL5>VL4>VL3>VL2>VSS。

ROW0-ROW79:提供给LCD屏的行(公共极)驱动信号。

COL0—COL311:提供给LCD屏的列(段)驱动信号。红绿蓝信息同时从段输出端发出。当处于睡眠或闲置方式时,这些引脚输出电平是VDD。

ICON:提供至图标行(公共极)的驱动信号。

MUX/80 :用于LCD驱动器的复用比率。

=VDD时,COM0-COM33映射到ROW0-ROW33

COM46-COM79映射到ROW34-ROW67

=VSS时,COM0-COM79映射到ROW0-ROW79。

2. 功能及内部结构

2.1 微处理器接口逻辑

由驱动6800系列MPU、8080系列MPU、3线和4线SPI接口的三个功能方框组成。通过PS0、PS1脚来选择不同的接口。

a) 与6800系列CPU并行接口

由8位双向数据脚 D7-D0、R/W、D/C、E、CS组成。 R/W脚输入高指示根据D/C输入的状态从图形显示RAM(GDDRAM)或状态寄存器进行读操作。当CS=0 且 E=1E脚输入作为数据锁存信号。为了使MCU和GDDRAM 的操作频率相匹配,一些管道处理在内部执行,因此第一个有效显示数据读之前需要插入虚拟读。

b) 与8080系列CPU并行接口

由8位双向数据脚 D7-D0、RD、WR、D/C、CS组成。假如CS是低电平且RD为低,RD输入作为读数据锁存信号。无论是从GDRRAM读显示数据还是从状态寄存器读状态都需要受D/C脚的控制。假如CS是低电平且WR为低,WR输入作为写数据锁存信号。无论是写显示数据到GDDRAM还是将命令写入命令寄存器都需要受D/C脚的控制。第一有效数据读之前也需要一次虚拟读。

c) 四线SPI

四线串行外设接口(SPI)由串行时钟SCK、串行数据SDA、D/C、CS组成。按照位7、位6.....位0的次序在SCK的每一个上升沿由SDA脚移入八位的移位寄存器。在第八个时钟的上沿采样D/C脚的状态以确定移位寄存器中的数据是写入显示数据RAM还是写入命令寄存器。

d) 三线SPI

三线SPI接口与四线接口类似只是不使用D/C脚。按照D/C位、D7....D0的次序在每第九个时钟时九位数据一起移进移位寄存器。D/C位(连续数据的首位)确定移位寄存器中的连续数据字节是写入显示数据RAM(D/C=1)还是写入命令寄存器(D/C=0)。

2.2 命令译码器:这个模块确定输入的数据是被解释成数据还是命令。根据D/C脚的输入电平数据被指向到这个模块中。若D/C=1,数据被写入GDDRAM。

D/C=0,数据解释为命令并译码,译码命令将写入对应的命令寄存器中。

2.3 图形显示数据RAM(GDDRAM):GDDRAM是一个保持被显示位类型的位映射静态RAM、RAM的大小是101088位=104RGB×81×4,如图2所示。可以用软件重新选择映射段和公共极的输出。四页形成一个RAM地址块并存入GDDRAM中。每块形成滚动地址的基本单元。通过软件编程来实现屏幕的滚动。为了容易存取RGB数据,八位彩色数据(R 3bit、G 3bit、B 2bit)被转换为四位数据(P10、P11、P12、P13),这四位数据被存进GDDRAM。例如数据按照设置的灰度值被定位于合适的RAM位置。

2.4 LCD驱动电压发生器和调整器:这个模块产生LCD所需要的显示输出电压。接受单电源输入并产生必需的偏压。由以下部分所组成:3X、4X、5X、6X DC/DC变换器;偏压分配器;对比度控制;偏压比选择;温度补偿电路。

2.5 振荡电路:片内低功耗RC振荡电路,产生DC/DC变换器、显示定时发生器的时钟。

2.6 显示数据锁存:执行显示信息的锁存。这些锁存器保持数据,将反馈到HV缓冲器和电平选择器到输出所需的电平。

2.7 HV缓冲单元(电平转换器):这个模块嵌入在段/公共极驱动电路中。HV缓冲单元起电平转换器的作用。将低电压输出信号转化为所需的驱动电压。通过参考来自显示定时发生器的内部FRM时钟的输出被转换。电压级别通过与内部M信号同步的电平选择器给定。

2.8 电平选择器:这个模块嵌入在段/公共极驱动电路中。电平选择器是显示同步的一个控制。显示电压级别可以分离成两相且使用不同的周期。同步是重要的因为它选择需要的LCD电压级别到依次输出COM或SEG波形的HV缓冲单元。

CMOS LCD 振荡器 电压 电容 总线 MCU 电路 单片机 显示器 相关文章:

- 一种易于集成的200万像素手机相机完整解决方案 (02-01)

- 通过高级驾驶员辅助系统提高汽车安全性能 (03-10)

- 嵌入式CMOS成像器用于全息数据检索(05-12)

- Virtex-II 和 Virtex-II Pro 器件的热插拔(08-03)

- 六大特点助CMOS图像传感器席卷医疗电子应用(11-13)

- AD1672单片12位模数转换器的原理及其应用(10-18)