让微控制器性能发挥极限

时间:03-24

来源:互联网

点击:

今天的微控制器需要执行广大范围的任务,包括管理实时控制算法、解码高速通信协定,以及处理高频传感器发出的信号。轮询方法(如检查端口以确定新数据是否经已到达)会消耗过多的CPU周期,而且对可靠服务I/O与外设的最大响应时间也往往太长。对于大多数嵌入式应用而言,开发人员以中断来满足对外设管理的实时要求。但中断只能够确定实时事件何时发生,开发人员仍然必须在数据丢失之前让CPU直接参与读取I/O和外设。处理一个中断可能需要同时中断其它对延时敏感的任务,带来任务转换支出,并引发一系列棘手问题,诸如如何管理多个中断同时发生时的延时,所有这些都会降低系统可预测性和处理器的效率。

微控制器要想处理实时I/O和外设的高数据速率和频率,便必须拥有更高的处理效率。但这个效率不能通过提高时钟频率来获得(因为需要更大功耗),而是要通过微控制器架构的内部改进来实现。实际上,微控制器已经开始集成用来卸载特殊任务模块的协处理器、可加快无惩罚型(penalty-free)内存访问速度的多信道DMA控制器,以及能在内部子系统之间发送信号以卸载I/O和外设管理任务的集成式事件系统。

卸载CPU任务还有很多方法

集成式协处理器在嵌入式微控制器中已获得相当广泛的应用,其中比较常见的协处理器是加密和TCP/IP卸载引擎。协处理器可高效卸载整个任务,或帮助执行复杂算法中的密集计算部分。例如,一个加密引擎可以把CPU上的AES计算任务从每次运算数千个周期缩减为数百个周期,而一个TCP/IP卸载引擎可以极小的CPU运行支出来终止一个以太网连接。此外,卸载引擎还能简化这些任务的实现过程,使开发人员无需编写扩充代码,便可以通过使用简单的API来加入先进的功能。

DMA和事件系统技术对开发人员来说是比较陌生的,因此并不常使用。DMA控制器通过执行数据访问(如在后台执行外设寄存器到内部或外部SRAM的数据访问),从CPU卸载数据移动管理任务。例如,开发人员可以配置DMA控制器,把一个数据块预载入片上RAM中,这样在CPU需要它之前就可以快速访问,从而消除了等待状态和相关延时。另外,DMA控制器还能够承担通信外设管理的大部分工作(见表1)。

表1 DMA控制器能够承担通信外设管理的大部分工作

利用DMA控制器所节省的周期数可以十分可观:许多嵌入式开发人员都已发现自己无法以有限的微控制器资源来满足应用的需求,直到认识了DMA,才突然明白原来还有大量额外的周期可用,数目有时甚至多达整个系统的30%到50%左右。许多开发人员都是在遇到处理方面的困难时,才首次发现这种未开发的潜力,尽管实际上这种潜力从一开始就可以使用。

熟知事件系统(event system)的开发人员就更少了。事件系统与DMA制器协同工作,可进一步减少CPU周期的负担,并降低总体功耗。事件系统是一条总线,能够将从微控制器上的一个外设发出的内部信号连接到另一个外设。当有事件在外设上发生时,它就可以在一个双周期的延时内触发其它外设采取行动,整个过程无需CPU参与,就和人体在手碰到火时无需大脑命令就自然做出反射动作的把手抽出来一样。

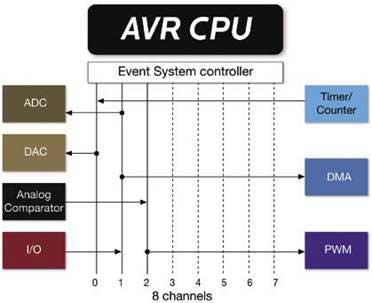

更确切地说,事件系统利用一个连接了CPU、数据总线和DMA控制器的专用网络在整个微控制器上进行信号路由(见图1)。在正常情况下,外设必须中断CPU来激活某个行动,包括读取外设本身。而事件系统通过直接在外设之间发送相关事件,便可有效地使CPU摆脱这些中断所带来的负担。开发人员可以灵活配置外设来使用不同的事件通道,从而定义特定的事件路由,以满足应用的某些需求。

图1 一个事件系统

灵活的卸载

DMA和事件系统配合工作,就可让开发人员卸载整个任务,这与协处理器的作用很类似,但两者间的关键区别是协处理器不是可编程的。协处理器采用硬件来执行一个已详细定义的任务,有时甚至是可配置的;而DMA控制器配合事件系统的可编程性使其适用于从最简单的到极复杂的各类任务。在采用DMA和事件系统的情况下,DMA负责管理整个微处理器架构上的数据传输;至于事件系统则控制这些低延时、高精度传输发生的时间。换言之,事件系统负责确保由DMA管理的数值在正确的时间/频率下被采样或输出。

图2所示为事件系统与DMA共同工作的原理模块示意图。ADC连接一个传感器,并会采集信号样本。内部计数器被设置为与采样频率相匹配,用以提供规律且精确的时间间隔。事件系统可以直接激活ADC的采样,而无需中断CPU,使采样频率比利用微控制器的时钟更为精确。当ADC停止并完成转换时,ADC便会触发DMA通过事件系统存储这些转换值。

图2 DMA控制器配合事件系统

事件管理可扩展为包含多个事件、连接多个外设的更复杂的配置。例如一个输入信号(事件1)可触发ADC采样(事件2),并把数值存储到DMA中(事件3),直到DMA缓冲器溢满(事件 4)。在这种配置中,CPU只有在缓冲器数据溢满需要处理时才会被中断。

DMA控制器和事件系统还支持多通道,使开发人员能够配置一个与主CPU并行工作的互连结构,因此,可采用一种固定性方式来对多个并行实时任务进行协调。

微控制器要想处理实时I/O和外设的高数据速率和频率,便必须拥有更高的处理效率。但这个效率不能通过提高时钟频率来获得(因为需要更大功耗),而是要通过微控制器架构的内部改进来实现。实际上,微控制器已经开始集成用来卸载特殊任务模块的协处理器、可加快无惩罚型(penalty-free)内存访问速度的多信道DMA控制器,以及能在内部子系统之间发送信号以卸载I/O和外设管理任务的集成式事件系统。

卸载CPU任务还有很多方法

集成式协处理器在嵌入式微控制器中已获得相当广泛的应用,其中比较常见的协处理器是加密和TCP/IP卸载引擎。协处理器可高效卸载整个任务,或帮助执行复杂算法中的密集计算部分。例如,一个加密引擎可以把CPU上的AES计算任务从每次运算数千个周期缩减为数百个周期,而一个TCP/IP卸载引擎可以极小的CPU运行支出来终止一个以太网连接。此外,卸载引擎还能简化这些任务的实现过程,使开发人员无需编写扩充代码,便可以通过使用简单的API来加入先进的功能。

DMA和事件系统技术对开发人员来说是比较陌生的,因此并不常使用。DMA控制器通过执行数据访问(如在后台执行外设寄存器到内部或外部SRAM的数据访问),从CPU卸载数据移动管理任务。例如,开发人员可以配置DMA控制器,把一个数据块预载入片上RAM中,这样在CPU需要它之前就可以快速访问,从而消除了等待状态和相关延时。另外,DMA控制器还能够承担通信外设管理的大部分工作(见表1)。

表1 DMA控制器能够承担通信外设管理的大部分工作

利用DMA控制器所节省的周期数可以十分可观:许多嵌入式开发人员都已发现自己无法以有限的微控制器资源来满足应用的需求,直到认识了DMA,才突然明白原来还有大量额外的周期可用,数目有时甚至多达整个系统的30%到50%左右。许多开发人员都是在遇到处理方面的困难时,才首次发现这种未开发的潜力,尽管实际上这种潜力从一开始就可以使用。

熟知事件系统(event system)的开发人员就更少了。事件系统与DMA制器协同工作,可进一步减少CPU周期的负担,并降低总体功耗。事件系统是一条总线,能够将从微控制器上的一个外设发出的内部信号连接到另一个外设。当有事件在外设上发生时,它就可以在一个双周期的延时内触发其它外设采取行动,整个过程无需CPU参与,就和人体在手碰到火时无需大脑命令就自然做出反射动作的把手抽出来一样。

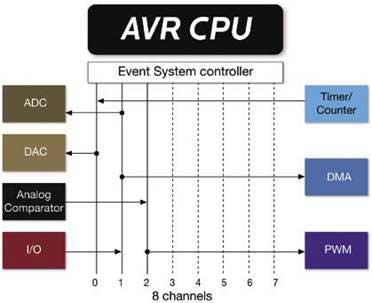

更确切地说,事件系统利用一个连接了CPU、数据总线和DMA控制器的专用网络在整个微控制器上进行信号路由(见图1)。在正常情况下,外设必须中断CPU来激活某个行动,包括读取外设本身。而事件系统通过直接在外设之间发送相关事件,便可有效地使CPU摆脱这些中断所带来的负担。开发人员可以灵活配置外设来使用不同的事件通道,从而定义特定的事件路由,以满足应用的某些需求。

图1 一个事件系统

灵活的卸载

DMA和事件系统配合工作,就可让开发人员卸载整个任务,这与协处理器的作用很类似,但两者间的关键区别是协处理器不是可编程的。协处理器采用硬件来执行一个已详细定义的任务,有时甚至是可配置的;而DMA控制器配合事件系统的可编程性使其适用于从最简单的到极复杂的各类任务。在采用DMA和事件系统的情况下,DMA负责管理整个微处理器架构上的数据传输;至于事件系统则控制这些低延时、高精度传输发生的时间。换言之,事件系统负责确保由DMA管理的数值在正确的时间/频率下被采样或输出。

图2所示为事件系统与DMA共同工作的原理模块示意图。ADC连接一个传感器,并会采集信号样本。内部计数器被设置为与采样频率相匹配,用以提供规律且精确的时间间隔。事件系统可以直接激活ADC的采样,而无需中断CPU,使采样频率比利用微控制器的时钟更为精确。当ADC停止并完成转换时,ADC便会触发DMA通过事件系统存储这些转换值。

图2 DMA控制器配合事件系统

事件管理可扩展为包含多个事件、连接多个外设的更复杂的配置。例如一个输入信号(事件1)可触发ADC采样(事件2),并把数值存储到DMA中(事件3),直到DMA缓冲器溢满(事件 4)。在这种配置中,CPU只有在缓冲器数据溢满需要处理时才会被中断。

DMA控制器和事件系统还支持多通道,使开发人员能够配置一个与主CPU并行工作的互连结构,因此,可采用一种固定性方式来对多个并行实时任务进行协调。

传感器 嵌入式 总线 ADC 电源管理 电压 电流 电容 比较器 爱特梅尔 AVR 电子 相关文章:

- 基于单片机的倾角测量系统设计 (06-27)

- 由MSP430和CC1100构成的无线传感器网络(08-01)

- 无线传感器网络自组网协议的实现方法(08-01)

- 基于SOC/IP的智能传感器设计研究(09-08)

- 单开关实现小型微处理器系统的双功能(08-10)

- 六大特点助CMOS图像传感器席卷医疗电子应用(11-13)