MOS芯片的ESD保护电路设计

随着CMOS集成电路产业的高速发展,越来越多的CMOS芯片应用在各种电子产品中,但在电子产品系统的设计过程中,随着CMOS工艺尺寸越求越小,单位面积上集成的晶体管越来越多,极大地降低了芯片的成本,提高了芯片的运算速度。

但是,随着工艺的进步和尺寸的减小,静电释放(ESD),Elecyro Static Discharge)问题变得日益严峻。据统计,在集成电路设计中大约40%的失效电路是ESD问题造成的。

MOS晶体管是绝缘栅器件,栅极通过薄氧化层和其他电极之间绝缘。如果栅氧化层有较大的电压,会造成氧化层击穿,使器件永久破坏。

随着器件尺寸减少,栅氧化层不断减薄,氧化层能承受的电压也不断下降,引起氧化层本征击穿的电场强度约为1 X 107V/cm。如栅氧化层厚度是50 nm 则可承受的最大电压约50 V,当栅氧化层厚度减少到5 nm,则所能承受的最大电压约为5 V。因此外界的噪声电压容易引起栅击穿。

特别是外界各种杂散电荷会在栅极上积累,由于MOS 晶体管的栅电容很小,只要少量的电荷就能形成很大的等效栅压,引起器件和电路失效,这就是ESD问题。例如,人体所带的静电荷可产生高达几kV的电压,在80%的湿度情况下,人走过化纤地毯可能产生1.5 kV静电压。ESD对CMOS集成电路的损伤,不仅会引起MOS器件栅击穿,还可能诱发电路内部发生闩锁效畸应。

另外,静电释放产生的瞬时大电流可能造成芯片局部发热,损害器件和电路。在一般的条件下,ESD不会导致器件即时失效,它往往潜伏在集成电路器件中,这种存在有潜在缺陷的器件在使用时容易失效。

特别是在深亚微米CMOS工艺中,由于溥栅氧化层的击穿电压较低,必须加入有效的在片ESD保护电路以箝位加到内部电路栅氧化层上的过充电压。

1 ESD放电模式与设计方案

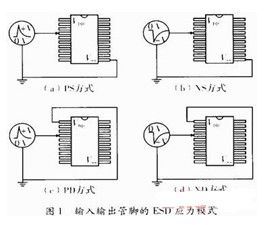

电路的输入或输出端与电源和地之间的ESD应力有4种模式

在集成电路中和外界相连的输入、输出端子比内部器什更容易受到ESD损伤。一般电路的输入或输出端与电源和地之间的ESD应力有4种模式:

(1)某一输入(或输出)端对地的正脉冲电压(PS模式):VSS接地,ESD正电压加到该输入输出端,对VSS放电,VDD与其他管脚悬空。

(2)某一输入(或输出)端对地的负脉冲电压(NS模式):VSS接地,ESD负电压加到该输入输出端,对VSS放电,VDD与其他管脚脚悬空。

(3)某一个输入或输出端相对VDD端的正脉冲电压(PD模式):VDD接地,ESD正电压加到该输入输出端,对VDD放电,VSS与其他管脚悬空。

(4)某一个输入或输出端相对VDD端的负脉冲电压(ND模式):VDD接地,ESD负电压加在该输入输出端,对VDD放电,VSS与其他管脚悬空。

防止集成电路芯片输入、输出端受到ESD应力损伤的方法是在芯片的输入和输出端增加ESD保护电路。保护电路的作用主要有两方面:一是提供ESD电流的释放通路;二是电压钳位,防止过大的电压加到MOS器件上。

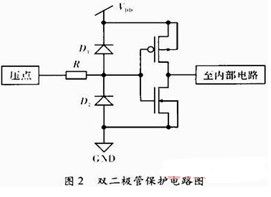

对CMOS集成电路连接到压点的输入端常采用双二极管保护电镀,图2所示为常见的ESD保护电路的结构:双二极管保护电路。

二极管D1是和PMOS源、漏区同时形成的,是p+n-结构,二极管D2是和NMOS源、漏区同时形成的,是n+p-结构。当压点相对地出现负脉冲应力,则二极管D2导通,导通的二极管和电阻形成ESD电流的泄放通路。

当压点相对地出现正脉冲应力,使二极管D2击穿,只要二极管D2击穿电压低于栅氧化层的击穿电压,就可以起到保护作用。类似的,当压点相对电源出现正脉冲或负脉冲应力,二极管D1起保护作用,提供静电荷的泄放通路。

这两个二极管把加到输入级MOS晶体管栅极的电压范围如式(1)所示:-0.7<Vin<VDD+0.7 (1)

假设二极管的正向导通电压是0.7 V。电阻的作用是限制流过二极管的电流。由于ESD应力电压都是短暂的脉冲信号,只要电流不是非常大,二极管不会被烧坏,可以持续起保护作用。

图2中使用二极管作为I/O端的ESD保护电路,主要提供PD和NS模式下的电流泄放通路,但对于ND模式和PS模式,二极管处于反偏状态,反偏箝位电压过高,电流泄放能力较弱,导通电阻较高,使箝位能力不够,且产生的热量较大。

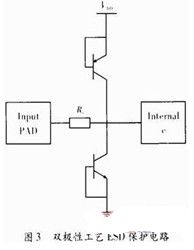

图3中电路主要用于双极工艺,采用一个基极接VDD地PNP三极管和一个基极接地的NPN三极管共同构成ESD保护电路。采用这种保护电路,相对于二极管,在ND和PS模式下,可以工作在Snapback状态,具有较强的电流泄放能力和较低的维持电压。

2 ESD保护电路

对深亚微米CMOS集成电路,栅氧化层的击穿电压很小,常规二极管的击穿电压较大,不能起到很好的保护作用。因此可以增加离子注入提高二极管的衬底浓度,形成p+n+和n+p+结构来降低二极管的击穿电压。

考虑到准备流片的多功能数字芯片要采用CSMC2P2M 0.

- TI高精度毫米波传感器制胜绝技 - CMOS技术详解(06-13)

- RFID 测试技术分析(02-09)

- 高增益高线性度混频器设计(01-25)

- 基于噪声消除技术的CMOS超宽带LNA设计(02-01)

- 基于CMOS工艺的RF集成电路设计(02-17)

- 3GHz~5GHz CMOS超宽带低噪声放大器设计(10-16)