嵌入式Flash Memory Cell技术

时间:01-20

来源:互联网

点击:

5 干扰与可靠性

5.1 存储单元与电路设计的可靠性问题

存储单元的阈值电压是擦写及读出过程的函数,因此要优化擦写过程的工作条件,提高工艺质量,特别是隧道氧化层、双多晶内氧化层在高场强下的质量与寿命,降低氧化层中陷阱(trap)的产生。图10是0.5μm单元在擦写循环后的阈值电压的变化。

5.2 超擦(Overerase)

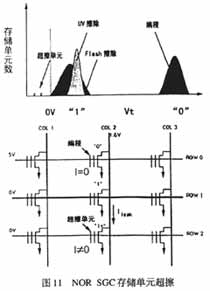

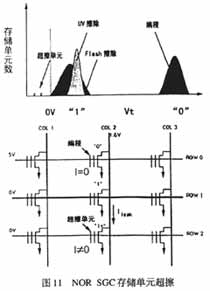

超擦NORSGC存储单元存在的主要问题,由于NOR阵列中的存储单元没有选择管,在字线上所有的存储单元漏端连在一起,如果在擦除后,某些单元的阈值电压特别低,在读出过程中,在非选择栅压下(通常为0V),几个单元有漏电,则字线上读不出正确的数据(见图11),特别是多次擦写循环后,增加了阈值电压的不确定性,因此需要在电路中设计验证电路。改进型SSI存储单元由于存在选择管,未选中的单元选择管关闭,因此基本上不受超擦漏电的影响。

5.3 软写(Soft-Write)

在电路正常工作时,读在浮栅上存储有正电荷(“1”电平)的单元,由于有沟道电流,以及在浮栅上有正电压存在,因此有少量的热电子发射,产生软写效应,长时间会使工作存储的信息丢失,为保证电路存储的信息保存时间超过十年,要对单元正常工作电压进行优化,改进型SSI存储单元的软写结果见图12,在电路设计中选择了2V漏源工作电压,可保证数据保存超过十年。

5.4 擦除干扰(Erase Disturb)

当电路中存在Sector擦除,并且不同Sector的单元漏端连接到同一条数据线(Bit Line)上时,要考虑到对选定的Sector擦除时,对非选择Sector的擦除干扰。

擦除干扰有二种形式:一是对选定的Sector擦除时,由于不同Sector的单元漏端连接到同一条数据线,非选择Sector的单元漏源上加有5V电压,如果单元存在漏电,就会有不希望的热电子发射;其二在已擦除的单元的浮栅上存在负电压,而非选择Sector的单元漏端上加有5V电压,因此在隧道氧化层有一定的电场强度,可能引起寄生隧道效应。

我们设计的0.51xm的Cell擦除时间为lsec,擦写次数100000次,要考虑的干扰时间为:

Erase Disturb Time=1×100000次=100000秒

解决的方法有:不同的Sector分开设计,不要把单元漏端连接到同一条数据线上;在连接到同一条数据线上的情况下,要合理设计单元,改进工艺,防止单元漏电,在擦除时将全部的源接5V电平。

5.5 编程干扰(Program Disturb)

由于在同一控制栅或编程栅下单元的控制栅或编程栅是连接在一起的,因此在字节编程时,会对非选择的字节产生编程干扰。在编程时,改进型SSI结构的存储单元的高压加在编程栅,编程干扰主要考虑寄生隧道效应,通过合理设计存储单元与电路来解决。

我们设计的0.5μm的Cell编程时间为300ns,假如同一编程栅下的字节为X,要考虑的干扰时间为:

Write Disturb Time:250ns×X

6 结束语

我们研究开发了一个0.5μm的改进型SSI结构的存储单元,对其性能与可靠性进行了研究,并用该技术设计了64k Flash Memory IP核,达到了满意的结果。

5.1 存储单元与电路设计的可靠性问题

存储单元的阈值电压是擦写及读出过程的函数,因此要优化擦写过程的工作条件,提高工艺质量,特别是隧道氧化层、双多晶内氧化层在高场强下的质量与寿命,降低氧化层中陷阱(trap)的产生。图10是0.5μm单元在擦写循环后的阈值电压的变化。

5.2 超擦(Overerase)

超擦NORSGC存储单元存在的主要问题,由于NOR阵列中的存储单元没有选择管,在字线上所有的存储单元漏端连在一起,如果在擦除后,某些单元的阈值电压特别低,在读出过程中,在非选择栅压下(通常为0V),几个单元有漏电,则字线上读不出正确的数据(见图11),特别是多次擦写循环后,增加了阈值电压的不确定性,因此需要在电路中设计验证电路。改进型SSI存储单元由于存在选择管,未选中的单元选择管关闭,因此基本上不受超擦漏电的影响。

5.3 软写(Soft-Write)

在电路正常工作时,读在浮栅上存储有正电荷(“1”电平)的单元,由于有沟道电流,以及在浮栅上有正电压存在,因此有少量的热电子发射,产生软写效应,长时间会使工作存储的信息丢失,为保证电路存储的信息保存时间超过十年,要对单元正常工作电压进行优化,改进型SSI存储单元的软写结果见图12,在电路设计中选择了2V漏源工作电压,可保证数据保存超过十年。

5.4 擦除干扰(Erase Disturb)

当电路中存在Sector擦除,并且不同Sector的单元漏端连接到同一条数据线(Bit Line)上时,要考虑到对选定的Sector擦除时,对非选择Sector的擦除干扰。

擦除干扰有二种形式:一是对选定的Sector擦除时,由于不同Sector的单元漏端连接到同一条数据线,非选择Sector的单元漏源上加有5V电压,如果单元存在漏电,就会有不希望的热电子发射;其二在已擦除的单元的浮栅上存在负电压,而非选择Sector的单元漏端上加有5V电压,因此在隧道氧化层有一定的电场强度,可能引起寄生隧道效应。

我们设计的0.51xm的Cell擦除时间为lsec,擦写次数100000次,要考虑的干扰时间为:

Erase Disturb Time=1×100000次=100000秒

解决的方法有:不同的Sector分开设计,不要把单元漏端连接到同一条数据线上;在连接到同一条数据线上的情况下,要合理设计单元,改进工艺,防止单元漏电,在擦除时将全部的源接5V电平。

5.5 编程干扰(Program Disturb)

由于在同一控制栅或编程栅下单元的控制栅或编程栅是连接在一起的,因此在字节编程时,会对非选择的字节产生编程干扰。在编程时,改进型SSI结构的存储单元的高压加在编程栅,编程干扰主要考虑寄生隧道效应,通过合理设计存储单元与电路来解决。

我们设计的0.5μm的Cell编程时间为300ns,假如同一编程栅下的字节为X,要考虑的干扰时间为:

Write Disturb Time:250ns×X

6 结束语

我们研究开发了一个0.5μm的改进型SSI结构的存储单元,对其性能与可靠性进行了研究,并用该技术设计了64k Flash Memory IP核,达到了满意的结果。

GPS 集成电路 DSP 电路 Microchip MCU 电子 电压 电流 CMOS 放大器 电阻 相关文章:

- 移动数字电视相关技术研究(三)(09-24)

- 天线设计面临小尺寸和多天线要求的挑战(11-06)

- GPS产品设计中的几个常见问题及应对之策(02-16)

- GPS产业蕴藏巨大商机 产值将突破100亿大关(10-22)

- GPS接收器架构与设计挑战(02-11)

- 移动GPS:果实终于成熟了(01-22)