机载电视制导VGA/TV转换器的设计与实现

时间:09-13

来源:互联网

点击:

3 系统软件设计

3.1 I2C协议实现

I2C总线是一种简单、双向二线制同步串行总线.它具备多主机系统所需的包括总线裁决和高低速设备同步功能的高性能串行总线。I2C总线上的器件之间通过串行数据线SDA和串行时钟线SCL相连接.传送信息。

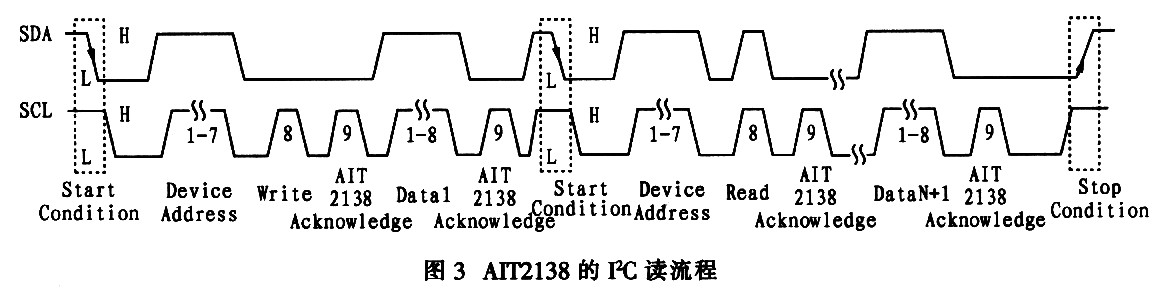

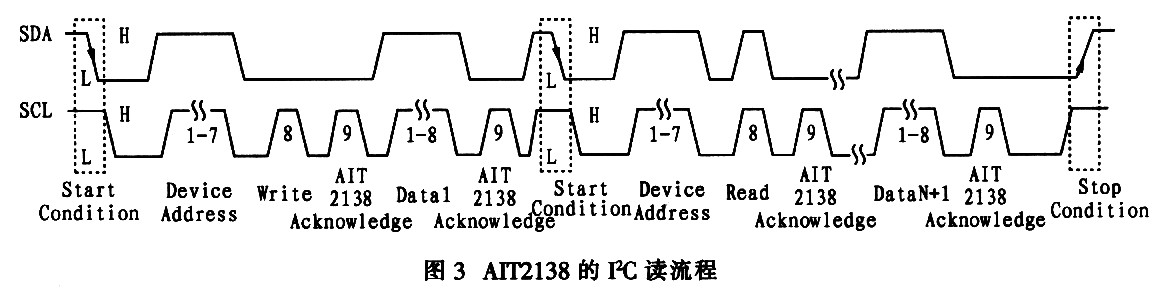

本系统中用AT89C51的P4口的I/0引脚1和2分别模拟12C总线的SCL和SDA引脚。AT89C51作为主控器在总线上发送命令.AIT2138作为接收器接收总线上的命令。作为总线裁决的重要信息.发送命令中必须包括AIT2138的地址信息,其地址为88H。AIT2138的F2C读流程如图3所示。

AIT2138的写流程相对简单.不需要在写入器件地址后进行读写转换.也就是上面时序中强制加入的第二个Start Condition(启动条件)。需要注意的是在I2C总线上每传输一位数据都有一个时钟脉冲相对应。这里的时钟脉冲不像一般的时钟必须是周期性的,它的时钟间隔可以不同。总线备用时(即“非忙”状态),SDA和SCL必须保持高电平,关闭I2C总线时才使SCL箝位在低电平。只有当总线处于“非忙”状态时,数据传输才能被初始化。在数据传输期间.只要时钟线为高电平,数据线都必须保持稳定.只有在时钟线为低电平时才允许数据线上的电平改变。在时钟线保持高电平期间,数据线上的下降沿为启动信号,上升沿为停止信号,启动和停止信号都由主机产生。AIT2138容易监测这些信号。

3.2 系统软件流程

软件设计是该系统设计中的一个难点,在系统第一版设计中.采用了AIT2138自动检测输入端的VGA视频信号对行、场同步频率进行设定,同步内部视频A/D转换和外部视频缓存内部的分场、视频转换过程。在使用过程中,发现机载多功能显示器上图像抖动.而且显示图像位置相对多功能显示器的视场有一定偏移,严重影响了视频效果。

研究发现.问题出在AIT2138的自适应调整功能上.其内部对VGA信号的行、场同步信号规定了几个挡位.以场同步为例,分为63 Hz一69 Hz,69 Hz一73Hz.73 Hz一79Hz,79Hz~85Hz4个挡位,由于其内部自动监测功能不完善.因此容易把刷新频率为75 Hz的视频信号归到69 Hz"73 Hz的挡位中,容易造成后端模拟视频输出抖动。后端视频视场的偏移与AIT2138内部的.HPR和VPR有关。所以笔者提出如下优化控制方案。软件的流程如图4所示。

AT89C2051首先对转换器输入端口进行有无行同步信号的检测。若有,则继续检测有无场同步信号.若无则判断为5线制视频信号,输入5线制视频信号时。信号的行、场同步信号直接接人AIT2138。然后通过设定AT89C2051内的2个16位定时器取值来设置行、场频率计数的时间阈值。在规定的时间间隔内对接人AT89C2051的2个I/O引脚的行、场同步信号线上出现的脉冲进行计数.通过计算脉冲个数与时间间隔的比值可得到确切的行、场频率。在得到行、场频率后,对AIT12138转换过程中要处理的5线制视频信号的具体参数进行优化计算,包括逐行视频图像的截取位置、面积和隔行电视图像显示的位置等.然后通过FC接口对AT12138进行编程控制。

4 系统抗干扰设计

在设计过程中.考虑到设备对外部的适应性,主要采取了以下措施:机壳采用金属铝件,机壳的金属部分良好接地,具有防护电磁干扰的作用;为了保证各个组件地线的接线端之间能长期、可靠地连接.采用了镀锡的铜接线片,同时,将接线片用螺钉固定在机座上,保证长期接地良好,并对整个组件进行防潮处理:按键面板通过铜质导线与机壳接触良好.防止外界电磁波干扰设备的正常工作;在电源输出端并接高、低频滤波电容器,防止电源高、低频噪声对元器件的影响。在PCB设计中需要注意:数字地与模拟地分离,应用EMI滤波装置以减少VDDA的电源噪声;LPF到AITl2138的整体电路引脚长度应当小于0.5英寸;VDDA和VSSA端应接O.1μF的旁路电容器以减少噪音。

5 结束语

这种VGA/TV转换器的特点是对采用逐行扫描方式微机输出的视频信号进行转换.并且可以得到广播电视级的PAL制式电视视频信号。经过在某型战机上试飞,获得效果很好的PAL制式标准电视视频信号,具有较高的应用价值。

3.1 I2C协议实现

I2C总线是一种简单、双向二线制同步串行总线.它具备多主机系统所需的包括总线裁决和高低速设备同步功能的高性能串行总线。I2C总线上的器件之间通过串行数据线SDA和串行时钟线SCL相连接.传送信息。

本系统中用AT89C51的P4口的I/0引脚1和2分别模拟12C总线的SCL和SDA引脚。AT89C51作为主控器在总线上发送命令.AIT2138作为接收器接收总线上的命令。作为总线裁决的重要信息.发送命令中必须包括AIT2138的地址信息,其地址为88H。AIT2138的F2C读流程如图3所示。

AIT2138的写流程相对简单.不需要在写入器件地址后进行读写转换.也就是上面时序中强制加入的第二个Start Condition(启动条件)。需要注意的是在I2C总线上每传输一位数据都有一个时钟脉冲相对应。这里的时钟脉冲不像一般的时钟必须是周期性的,它的时钟间隔可以不同。总线备用时(即“非忙”状态),SDA和SCL必须保持高电平,关闭I2C总线时才使SCL箝位在低电平。只有当总线处于“非忙”状态时,数据传输才能被初始化。在数据传输期间.只要时钟线为高电平,数据线都必须保持稳定.只有在时钟线为低电平时才允许数据线上的电平改变。在时钟线保持高电平期间,数据线上的下降沿为启动信号,上升沿为停止信号,启动和停止信号都由主机产生。AIT2138容易监测这些信号。

3.2 系统软件流程

软件设计是该系统设计中的一个难点,在系统第一版设计中.采用了AIT2138自动检测输入端的VGA视频信号对行、场同步频率进行设定,同步内部视频A/D转换和外部视频缓存内部的分场、视频转换过程。在使用过程中,发现机载多功能显示器上图像抖动.而且显示图像位置相对多功能显示器的视场有一定偏移,严重影响了视频效果。

研究发现.问题出在AIT2138的自适应调整功能上.其内部对VGA信号的行、场同步信号规定了几个挡位.以场同步为例,分为63 Hz一69 Hz,69 Hz一73Hz.73 Hz一79Hz,79Hz~85Hz4个挡位,由于其内部自动监测功能不完善.因此容易把刷新频率为75 Hz的视频信号归到69 Hz"73 Hz的挡位中,容易造成后端模拟视频输出抖动。后端视频视场的偏移与AIT2138内部的.HPR和VPR有关。所以笔者提出如下优化控制方案。软件的流程如图4所示。

AT89C2051首先对转换器输入端口进行有无行同步信号的检测。若有,则继续检测有无场同步信号.若无则判断为5线制视频信号,输入5线制视频信号时。信号的行、场同步信号直接接人AIT2138。然后通过设定AT89C2051内的2个16位定时器取值来设置行、场频率计数的时间阈值。在规定的时间间隔内对接人AT89C2051的2个I/O引脚的行、场同步信号线上出现的脉冲进行计数.通过计算脉冲个数与时间间隔的比值可得到确切的行、场频率。在得到行、场频率后,对AIT12138转换过程中要处理的5线制视频信号的具体参数进行优化计算,包括逐行视频图像的截取位置、面积和隔行电视图像显示的位置等.然后通过FC接口对AT12138进行编程控制。

4 系统抗干扰设计

在设计过程中.考虑到设备对外部的适应性,主要采取了以下措施:机壳采用金属铝件,机壳的金属部分良好接地,具有防护电磁干扰的作用;为了保证各个组件地线的接线端之间能长期、可靠地连接.采用了镀锡的铜接线片,同时,将接线片用螺钉固定在机座上,保证长期接地良好,并对整个组件进行防潮处理:按键面板通过铜质导线与机壳接触良好.防止外界电磁波干扰设备的正常工作;在电源输出端并接高、低频滤波电容器,防止电源高、低频噪声对元器件的影响。在PCB设计中需要注意:数字地与模拟地分离,应用EMI滤波装置以减少VDDA的电源噪声;LPF到AITl2138的整体电路引脚长度应当小于0.5英寸;VDDA和VSSA端应接O.1μF的旁路电容器以减少噪音。

5 结束语

这种VGA/TV转换器的特点是对采用逐行扫描方式微机输出的视频信号进行转换.并且可以得到广播电视级的PAL制式电视视频信号。经过在某型战机上试飞,获得效果很好的PAL制式标准电视视频信号,具有较高的应用价值。

视频监控 显示器 单片机 总线 电路 滤波器 电源模块 电压 电容 PCB 电容器 相关文章:

- 基于CH374的USB摄像头驱动设计 (04-10)

- 智能家居中的数字视频监控、门禁和灯光控制(06-05)

- 视频监视领域的视频压缩与数据流(06-18)

- 基于DM642嵌入式无线视频监控硬件设计 (10-15)

- 基于FIC8120和PoE的IP-Camera设计(03-11)

- 智能家居:数字视频监控 门禁和灯光控制(05-01)