用于超便携式设备和消费电子USB 2.0高速设计的模拟开关

时间:08-27

来源:互联网

点击:

由于PC主机与便携式设备如手机之间所需的数据吞吐量不断增大,USB 2.0高速I/O (480Mbps) 在便携式应用领域的使用日益增多。在功能性的需求带动下,外设设备控制器或基带处理器需要接入USB端口,以便与外部PC主机进行通信。在这类应用中,高速USB开关需要用来满足市场对于更快速的上载和下载需求。本文将举例说明如何使用高速USB开关减低整体应用的设计复杂性。此外,本文会提供一些设计建议,以解决高速设计的带宽限制和眼开难题。还会描述详细的设计方案,说明如何利用沿着数据路径的开关将附加抖动减至最小,并且符合高速USB眼罩要求。

新兴应用示例

由于3G手机的功能聚合增多,MP3播放器或数字相机等功能现需要系统存储器之外的附加存储器。市场现行一般的解决方案是使用可移除存储器,如SD卡或更小型的MMC卡。随着更多的视频流功能在市场上出现,如TV节目录制,未来高端手机设计的嵌入式硬盘功能需要具备更高的存储量和更低的成本。硬盘手机的一项独到功能是USB 2.0的高速能力,可在PC主机和手机之间达到480Mbps数据吞吐量,而且USB 1.1全速模式提供更快的上载和下载档案速度。然而,传统的全速USB模式仍然存在于基带处理器中,用以满足其它功能需求如地址本同步等。

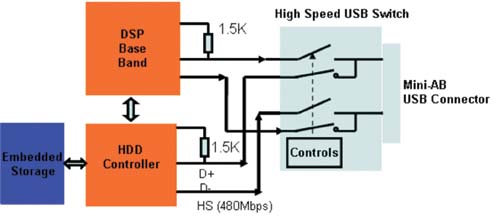

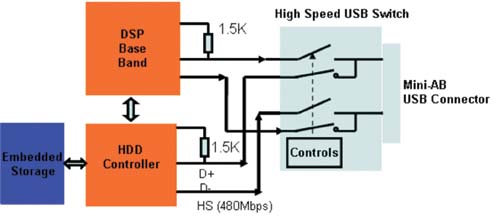

现有的架构是硬盘控制器在基带处理器的外面。但不幸地,USB串行数据线路不能直接扎在一起共享通用的微型USB连接器,因为两条D+ 线路都具有1.5KΩ上拉电阻。即使其中一个USB输出停用,悬挂在数据总线上的迹线也会因为USB高速信号具有高摆率 (上升/下降时间快至500ps) 而引起信号反射,结果会带来高速眼罩方面的风险。本文稍后将讨论如何将高速USB信号的DC和AC眼开拓至最大。图1所示为这类应用的多个解决方案。在这个图中,高速USB开关位于两个USB输出之间,共享同一个D+/D- 连接器,这样当其中一个USB口不在通信状态时,对应的多余迹线可以被有效地切断。当然,图1的架构还适用于纤细型手机设计,需要在高速USB端口和基带处理器的UART输出之间共享USB连接器。

图1 高速低功率(<1uA) USB开关允许全速和高速USB信号共享单个USB连接端口

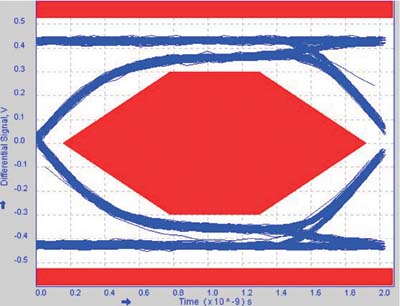

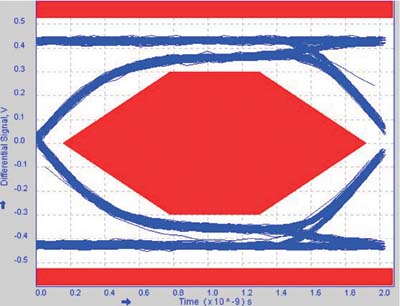

图2是飞兆半导体USB开关 (FSUSB20) 的输出眼开,采用高速硬盘输出测试,并通过了眼开的合格测试。这种开关具有小型封装选项 (MicroPakTM: 1.6mm x 2.1mm) 和低静态功耗 (<1uA),非常适合电池供电应用所采用,如手机、笔记本电脑和PDA。此外,MicroPak等无引线封装可将引脚电感减至最小,有助于提升数据路径带宽,从而提升眼开性能。

图2 飞兆半导体FSUSB20符合高速USB眼开要求

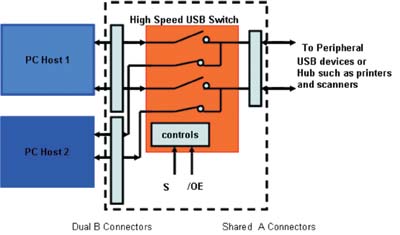

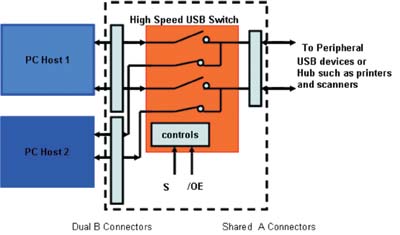

图3是USB开关盒应用,允许两个计算机共享同一个USB器件,例如在家居或办公室的打印机或扫描仪应用。只需通过面板上的手动开关或软件指令即可进行控制。在这类应用中,具有750MHz -3db带宽的双极双通高带宽开关 (如FSUSB20) 便可完全满足要求,轻易通过USB 2.0高速 (480Mbps) 吞吐量的第三阶谐波频率(720MHz)。

图3 高速USB开关盒应用中的高速USB开关

设计挑战和解决方案

如前所述,为了将USB高速眼图的眼开拓至最大,AC和DC因素都需要加以考虑。DC因素主要指USB开关的DC插入损耗,要求开关具有低导通阻抗。当终端为45Ω时,导通阻抗为10Ω的开关为400mV高速USB输入提供327mV输出信号摆幅。推荐使用低导通阻抗的开关来提高噪声裕量。但如果过于强调最小插入损耗或低导通阻抗,可能会误导设计人员作出错误的开关选择。相位抖动和相位降级等AC效应会带来更高不符眼开要求的风险。相位抖动的主因之一是沿着数据路径的带宽较低,造成信号的确定性抖动。此外,开关的较高带宽会容许高阶谐波成分 (高速USB数据的三次谐波为720MHz) 通过,从而加速信号边沿的上升/下降时间。这些高频成分使得信号逻辑变换远离于所需的掩膜。

便携式设计应用讲求卓越的ESD保护性能,通常使用外部ESD保护二极管以满足系统的ESD需求 (一般 >15KV)。这些保护二极管需要小心选择。它们的寄生电容由1pf 至 10pf不等。ESD电容通常会给开关带来很重的负担,导致带宽曲线快速变化。在这些应用中,低电容ESD抑制器很受欢迎。但是,如果模拟开关本身具有较大的带宽,将可为外部ESD保护器件带来更多的电容性负载预算和更多的选择。如果降低ESD寄生电容,数据路径将会获得更高的带宽。为了将反射降至最低,理想情况下USB开关应很靠近USB控制器从而被视为输出的直接负载。这是基于USB控制器输出相对于USB眼罩有足够的裕量的假设。在有些设计中,USB控制器输出具有相对较慢的上升或下降沿以及较小的输出幅度,将USB开关放在距离USB控制器相对远一点的位置会有利于降低开关寄生电容对输出的影响。这样会降低上升下降沿的失真,但是要付出信号反射的代价。所以这里在信号反射和上升及下降沿低垂之间存在一个权衡。建议将ESD保护器件尽量靠近连接器置放。当然,沿着数据路径的迹线和线头长度越短,越能提高信号的带宽,从而改善相位抖动性能。

便携式USB设计的另一个难题是电源。许多手机的电路管理单元具有3.3V 和2.7V输出,但建议使用3.3V电源为图1所示应用的模拟开关供电,以达到全速模式下的2.8V最小VOH 输出要求。这是因为如果主机只有全速能力,高速外设便需要在全速模式下工作。此外,模拟开关的功耗很少 (静态电流 <1uA),建议即使在待机模式下也应将电源置于开启状态。

新兴应用示例

由于3G手机的功能聚合增多,MP3播放器或数字相机等功能现需要系统存储器之外的附加存储器。市场现行一般的解决方案是使用可移除存储器,如SD卡或更小型的MMC卡。随着更多的视频流功能在市场上出现,如TV节目录制,未来高端手机设计的嵌入式硬盘功能需要具备更高的存储量和更低的成本。硬盘手机的一项独到功能是USB 2.0的高速能力,可在PC主机和手机之间达到480Mbps数据吞吐量,而且USB 1.1全速模式提供更快的上载和下载档案速度。然而,传统的全速USB模式仍然存在于基带处理器中,用以满足其它功能需求如地址本同步等。

现有的架构是硬盘控制器在基带处理器的外面。但不幸地,USB串行数据线路不能直接扎在一起共享通用的微型USB连接器,因为两条D+ 线路都具有1.5KΩ上拉电阻。即使其中一个USB输出停用,悬挂在数据总线上的迹线也会因为USB高速信号具有高摆率 (上升/下降时间快至500ps) 而引起信号反射,结果会带来高速眼罩方面的风险。本文稍后将讨论如何将高速USB信号的DC和AC眼开拓至最大。图1所示为这类应用的多个解决方案。在这个图中,高速USB开关位于两个USB输出之间,共享同一个D+/D- 连接器,这样当其中一个USB口不在通信状态时,对应的多余迹线可以被有效地切断。当然,图1的架构还适用于纤细型手机设计,需要在高速USB端口和基带处理器的UART输出之间共享USB连接器。

图1 高速低功率(<1uA) USB开关允许全速和高速USB信号共享单个USB连接端口

图2是飞兆半导体USB开关 (FSUSB20) 的输出眼开,采用高速硬盘输出测试,并通过了眼开的合格测试。这种开关具有小型封装选项 (MicroPakTM: 1.6mm x 2.1mm) 和低静态功耗 (<1uA),非常适合电池供电应用所采用,如手机、笔记本电脑和PDA。此外,MicroPak等无引线封装可将引脚电感减至最小,有助于提升数据路径带宽,从而提升眼开性能。

图2 飞兆半导体FSUSB20符合高速USB眼开要求

图3是USB开关盒应用,允许两个计算机共享同一个USB器件,例如在家居或办公室的打印机或扫描仪应用。只需通过面板上的手动开关或软件指令即可进行控制。在这类应用中,具有750MHz -3db带宽的双极双通高带宽开关 (如FSUSB20) 便可完全满足要求,轻易通过USB 2.0高速 (480Mbps) 吞吐量的第三阶谐波频率(720MHz)。

图3 高速USB开关盒应用中的高速USB开关

设计挑战和解决方案

如前所述,为了将USB高速眼图的眼开拓至最大,AC和DC因素都需要加以考虑。DC因素主要指USB开关的DC插入损耗,要求开关具有低导通阻抗。当终端为45Ω时,导通阻抗为10Ω的开关为400mV高速USB输入提供327mV输出信号摆幅。推荐使用低导通阻抗的开关来提高噪声裕量。但如果过于强调最小插入损耗或低导通阻抗,可能会误导设计人员作出错误的开关选择。相位抖动和相位降级等AC效应会带来更高不符眼开要求的风险。相位抖动的主因之一是沿着数据路径的带宽较低,造成信号的确定性抖动。此外,开关的较高带宽会容许高阶谐波成分 (高速USB数据的三次谐波为720MHz) 通过,从而加速信号边沿的上升/下降时间。这些高频成分使得信号逻辑变换远离于所需的掩膜。

便携式设计应用讲求卓越的ESD保护性能,通常使用外部ESD保护二极管以满足系统的ESD需求 (一般 >15KV)。这些保护二极管需要小心选择。它们的寄生电容由1pf 至 10pf不等。ESD电容通常会给开关带来很重的负担,导致带宽曲线快速变化。在这些应用中,低电容ESD抑制器很受欢迎。但是,如果模拟开关本身具有较大的带宽,将可为外部ESD保护器件带来更多的电容性负载预算和更多的选择。如果降低ESD寄生电容,数据路径将会获得更高的带宽。为了将反射降至最低,理想情况下USB开关应很靠近USB控制器从而被视为输出的直接负载。这是基于USB控制器输出相对于USB眼罩有足够的裕量的假设。在有些设计中,USB控制器输出具有相对较慢的上升或下降沿以及较小的输出幅度,将USB开关放在距离USB控制器相对远一点的位置会有利于降低开关寄生电容对输出的影响。这样会降低上升下降沿的失真,但是要付出信号反射的代价。所以这里在信号反射和上升及下降沿低垂之间存在一个权衡。建议将ESD保护器件尽量靠近连接器置放。当然,沿着数据路径的迹线和线头长度越短,越能提高信号的带宽,从而改善相位抖动性能。

便携式USB设计的另一个难题是电源。许多手机的电路管理单元具有3.3V 和2.7V输出,但建议使用3.3V电源为图1所示应用的模拟开关供电,以达到全速模式下的2.8V最小VOH 输出要求。这是因为如果主机只有全速能力,高速外设便需要在全速模式下工作。此外,模拟开关的功耗很少 (静态电流 <1uA),建议即使在待机模式下也应将电源置于开启状态。

USB 嵌入式 连接器 电阻 总线 飞兆 半导体 电感 二极管 电容 电路 电流 相关文章:

- 基于USB的通用无线传输接口设计(09-20)

- 索尼VRD-MC1 DVD刻录机解析(09-24)

- USB On-The-Go 技术概述(09-16)

- 谈关于非编网络的管理及其维护(下)(10-02)

- 打破瓶颈,以技术驱动液晶电视升级换代(11-26)

- 高速USB OTG--便携设备绝佳的互连解决方案(11-18)