一种针对多媒体手机设计中改进高速USB的设备

时间:08-02

来源:互联网

点击:

西桥架构

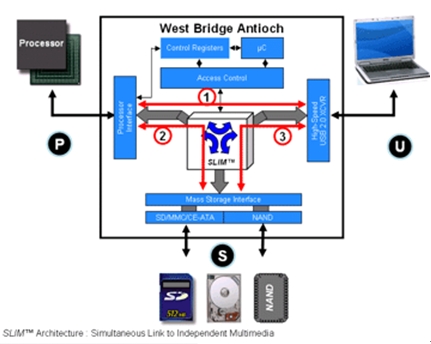

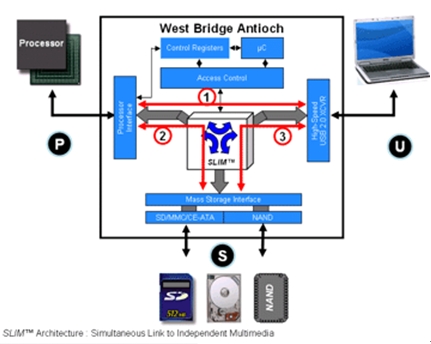

为迎接多任务处理的挑战,系统设计师需要新的设计架构选择,例如西桥,它消除了几代处理器的处理瓶颈。就像在PC架构中引入北桥和南桥一样,在嵌入式系统中,西桥将负责主处理器与外设的连接。图4为采用西桥的架构。

图4:西桥架构方框图

在这个图例中,西桥有三个端口:一个处理器“P”端口,一个HSUSB“U”端口及一个海量存储器“S”端口。其中“P”端口连接嵌入式处理器,同时支持硬件DMA通道。在手机设计中,“P”端口连接到基带处理器的标准外部存储接口;“U”端口提供USB2.0连接,“S”端口支持各种海量存储技术,例如8位/16位NAND闪存,SD/miniSD/T-F Flash,MMC/MMC+,甚至新的硬盘驱动(HDD)标准CE-ATA。

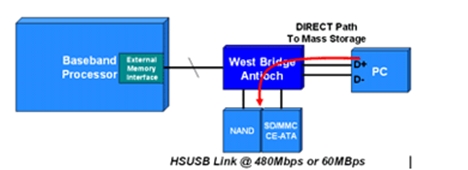

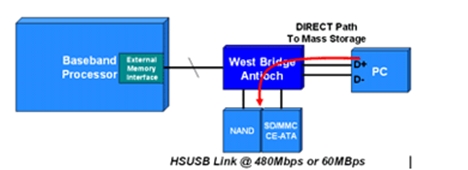

图4中的红箭头表示这3个端口中可能的数据通路。注意当这些箭头都通过西桥时,为了避免堵塞,它们同时而又彼此独立地被标出。箭头“1”,即“P”端口和“U”端口间的通路,通过HSUSB接口实现基带处理器与外部的连接。这个数据通路可实现像前面提到的无线上网这类的新应用模型。箭头“2”,即“P”端口和“S”端口间的通路,将基带处理器连到海量存储器,就像二者直接连接一样。箭头“3”,即“U”端口与“S”端口之间的通路,支持将PC与海量存储器中的数据上传和下载到手机上。这个通路尤其适用于传输多媒体文件:从PC下载MP3/WMA/Video到手机,或者从手机上传图片到PC。与图3中的手机架构相比,海量存储器现在直接连接到西桥和不是处理器本身。这样,基带处理器完全摆脱了数据传输的负担,因为它不再作为PC与海量存储器间的数据通路。这为更多重要的任务释放出了处理器的工作带宽。图5将解释这种新的架构。注意PC与海量存储间的数据通路与图2和图3中的不同。

图5:采用Antioch西桥时从PC到海量存储器的直接通路。

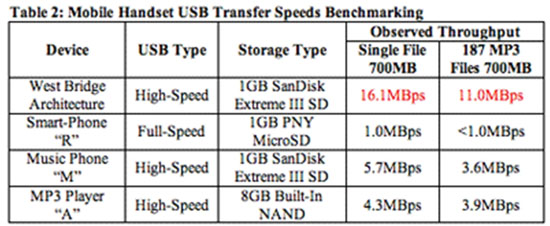

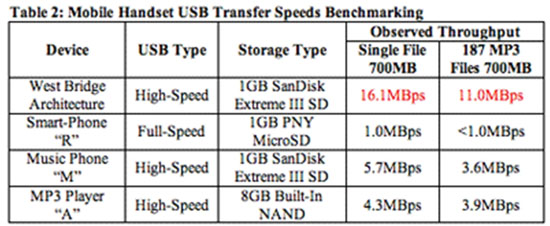

总而言之,PC与海量存储器间的直接通路极大的提高了吞吐效率。塞普拉斯为当今市场上不同移动设备的USB连接吞吐量设定了标杆。在可控环境下对该标杆进行了测试试验,表2中列出了测试结果。这些设备的名字因需保密而省略。

如表2所示,PC与海量存储器间的直接通路极大地提高了吞吐效率。这使得西桥对一些性能关键系统十分有吸引力,因为它能大大提升用户的HSUSB体验。

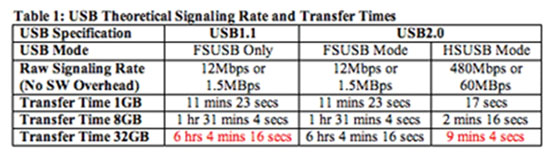

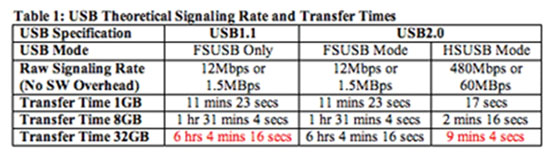

表1:USB的理论传输速率和传输时间。

表2:手机USB传输速率标杆测试结果。

重点是,这种架构允许三条数据通路同时开通。这使得任何移动手机设计都可以应用西桥。一款典型的处理器从设计到大规模生产需要大约2年的时间,而海量存储器接口标准的更新远快于处理器设计周期,所以市场上的处理器往往很难支持最新的存储设备。但通过使用西桥,就能够完美地连接到现今大多数处理器都还无法支持的最新海量存储设备,例如SD2.0和CE-ATA。

桥架构解决了PC中的很多难题。类似地,在移动手机设计中引入西桥将设计者从平衡其功能与灵活性中解放出来。西桥并不只通过PC与存储设备间的直接通路带来最佳HSUSB体验,它还能实现同时支持不同应用模型的多任务,并满足当前以及未来的多媒体手机设计中不断增长的吞吐率需求。

为迎接多任务处理的挑战,系统设计师需要新的设计架构选择,例如西桥,它消除了几代处理器的处理瓶颈。就像在PC架构中引入北桥和南桥一样,在嵌入式系统中,西桥将负责主处理器与外设的连接。图4为采用西桥的架构。

图4:西桥架构方框图

在这个图例中,西桥有三个端口:一个处理器“P”端口,一个HSUSB“U”端口及一个海量存储器“S”端口。其中“P”端口连接嵌入式处理器,同时支持硬件DMA通道。在手机设计中,“P”端口连接到基带处理器的标准外部存储接口;“U”端口提供USB2.0连接,“S”端口支持各种海量存储技术,例如8位/16位NAND闪存,SD/miniSD/T-F Flash,MMC/MMC+,甚至新的硬盘驱动(HDD)标准CE-ATA。

图4中的红箭头表示这3个端口中可能的数据通路。注意当这些箭头都通过西桥时,为了避免堵塞,它们同时而又彼此独立地被标出。箭头“1”,即“P”端口和“U”端口间的通路,通过HSUSB接口实现基带处理器与外部的连接。这个数据通路可实现像前面提到的无线上网这类的新应用模型。箭头“2”,即“P”端口和“S”端口间的通路,将基带处理器连到海量存储器,就像二者直接连接一样。箭头“3”,即“U”端口与“S”端口之间的通路,支持将PC与海量存储器中的数据上传和下载到手机上。这个通路尤其适用于传输多媒体文件:从PC下载MP3/WMA/Video到手机,或者从手机上传图片到PC。与图3中的手机架构相比,海量存储器现在直接连接到西桥和不是处理器本身。这样,基带处理器完全摆脱了数据传输的负担,因为它不再作为PC与海量存储器间的数据通路。这为更多重要的任务释放出了处理器的工作带宽。图5将解释这种新的架构。注意PC与海量存储间的数据通路与图2和图3中的不同。

图5:采用Antioch西桥时从PC到海量存储器的直接通路。

总而言之,PC与海量存储器间的直接通路极大的提高了吞吐效率。塞普拉斯为当今市场上不同移动设备的USB连接吞吐量设定了标杆。在可控环境下对该标杆进行了测试试验,表2中列出了测试结果。这些设备的名字因需保密而省略。

如表2所示,PC与海量存储器间的直接通路极大地提高了吞吐效率。这使得西桥对一些性能关键系统十分有吸引力,因为它能大大提升用户的HSUSB体验。

表1:USB的理论传输速率和传输时间。

表2:手机USB传输速率标杆测试结果。

重点是,这种架构允许三条数据通路同时开通。这使得任何移动手机设计都可以应用西桥。一款典型的处理器从设计到大规模生产需要大约2年的时间,而海量存储器接口标准的更新远快于处理器设计周期,所以市场上的处理器往往很难支持最新的存储设备。但通过使用西桥,就能够完美地连接到现今大多数处理器都还无法支持的最新海量存储设备,例如SD2.0和CE-ATA。

桥架构解决了PC中的很多难题。类似地,在移动手机设计中引入西桥将设计者从平衡其功能与灵活性中解放出来。西桥并不只通过PC与存储设备间的直接通路带来最佳HSUSB体验,它还能实现同时支持不同应用模型的多任务,并满足当前以及未来的多媒体手机设计中不断增长的吞吐率需求。

- LCD TV整体电源解决方案-“GreenEngine?”技术(02-23)

- 在消费电子应用中考虑使用OTP存储器(04-13)

- 晶体元件在电子器件中不可缺(05-12)

- 用于移动电子设备的电路保护方案(11-08)

- 耳机设计:品质VS效率(01-07)

- SMARTCAR软件平台实现汽车电子系统软件的整体设计(03-30)