基于SPCA751A的MP3播放器的设计

时间:08-03

来源:互联网

点击:

MP3压缩音乐的方式是通过一个运算法则,去掉声音中高频与低频的部分,大幅删减不必要的容量浪费,同时保留了人类所能感受到的音频部分。因此,它的好处在于大幅降低了数字声音文件的容量,而不会破坏原来的音质。在MP3的运算法则下,音质越低的声音可以得到越高的压缩比例。以CD音质的Wave文件来说,如抽样分辨率为16bit,抽样频率为44.1kHz,声音模式为立体声,那么存储1秒钟CD音质的Wave文件,必须要用掉16bit×44100×2=1411200bit,也就是相当于1411.2kbit的存储容量,存储介质的负担很大。而通过MP3格式压缩后,文件便可以压缩为原来的1/10到1/12,每一秒钟的MP3只需大约U2-128kbit就可以了。

MP3播放系统分为便携式和非便携式两种。对于非便携式,要考虑和其他CD音乐格式的共容性。对于便携式系统,主要考虑的是其体积小巧、低功耗、高容量、低价格。

系统简介

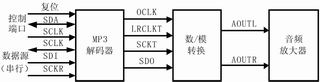

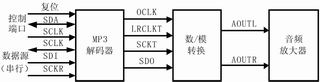

便携式MP3播放器的系统框图如图1所示,各部分的功能说明如下:

图1 便携式MP3播放器系统框图

1. 解码部分:这是MP3播放器的核心部件,采用硬件解码技术。

2. 存储部分:目前一般采用32MB的FLASH存储器,32MB的存储器能够存储36分钟128kbps(达到CD音质)的音乐,如果是播放16kbps的压缩话音,可以存储4个小时的内容。

3. 接口部分:一般通过PC的并口或USB口进行MP3文件的下载,并口的传输速率较低,USB口的传输速率可以高达12Mbps。

4.电源管理:便携式MP3的体积小,只用1到2只AAA电池供电,因此采用低电压以及进行有效的功率管理是非常必要的。

音频解码芯片内部结构

SPCA751A是凌阳科技公司生产的单片信号处理芯片,是一个MPEG Layer2.5音频专用解码芯片,已经广泛应用于一些便携式的MP3播放器设计中。它可支持对8—320Kbps基本数据流的解码,支持的取样频率范围为8KHz—48KHz,非常适合于MPEG的音频解码,并带有数字语音录音的MPEG播放模块,具有很高的性能/价格比。解码后的信号是可以直接输出到DAC的立体声、单声道或双声道的数字信号,SPCA751A与DAC的接口是可编程的。只要通过通用的串行I/O口和控制接口就能对MPEG比特流进行输入/输出和回放控制,系统控制器能很轻易的对MPEG音频信号进行解码。通过一个通用的可编程I2S接口,就能把一解码的音频PCM数据输出到外部的DAC中,因此,大多数常用的音频DAC都能和SPCA751A兼容。

对于嵌入式的语音录音,SPCA751A具有高品质的10位8KHz采样频率的ADC。基于SACM_S480或者SACM_S3200的运算法则,语音可以分别被压缩到4.8Kbps和32Kbps,而保持原始的语音效果。

SPCA751A使用的电源为3.0V"3.6V,它可以从其本身使用的16.934MHz晶振通过锁相环与系统时钟同步。SPCA751A信号处理器的工作频率可以达到34MHz而功耗很少,这就使得SPCA751A特别适合于便携式系统。

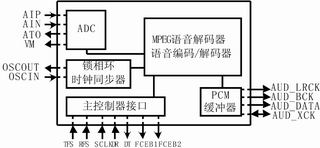

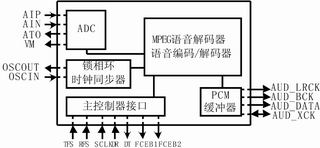

SPCA751A芯片的内部功能如图2所示,其主控制器只要具有足够的I/O口、能访问闪存和驱动LCD即可。

图2 SPCA751A内部功能图

为了适合数字录音应用的需要,SPCA751A有一个适合于语音波段的Σ-ΔADC,转换器的电路包括两个主要模块:ADC模块和内部参考偏置电压模块,后者为一个带有10位谐和音的15位数据格式。

ADC模块包括麦克风放大器、一个可编程增益放大器(PGA)、一个模拟过采样调节器和十进制数据滤波器。PGA增益可以从-12dB到12dB(-12,-6,0,6,12dB),当过采样信号频率为1.024MHz时,调节器是一个Σ-Δ反馈回路, 它完成微分模拟信号输入到脉冲密度调整单比特数字信号输出的转换。

图3 MPEG音频播放器系统框图

CEI表示主控制器是否可以接收数据 设置初始化参数:IDF+512字节数据 设置比特流:ID6+512字节比特流 设置命令:ID(低位字节)+命令(高位字节)

硬件设计

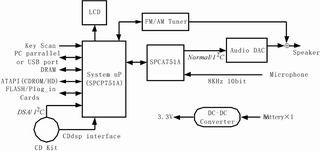

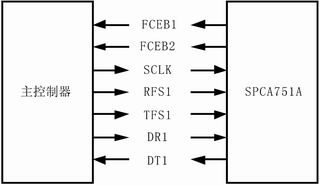

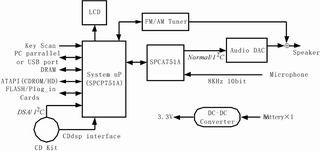

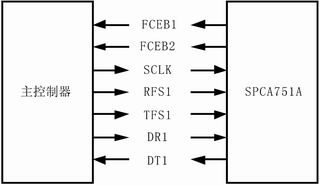

SPCA751A是单片的CMOS微处理器,是实时的MPEG音频解码和语音录音的专用芯片。主处理器通过串行控制口/I/O接口的命令控制SPCA751A对MPEG语音数据进行解码,主处理器也可以根据该接口检测解码过程。MPEG音频播放器系统框图如图3所示。SPCA751A与主控制器的连接如图4所示。

图4 SPCA751A与主控制器的连接

软件设计

SPCA751A工作于两种模式,MP3模式和数字语音录音(DVR)模式。在MP3模式,SPCA751A解码输入的比特流,发送到SPCA751A的数据作为输入数据。当FCEB1为高电平(缺省)时,主处理器发送比特流到SPCA751A;当FCEB1为低电平时,表明SPCA751A处于忙碌状态,这时,主处理器不能发任何数据到SPCA751A。在DVR模式,SPCA751A编/解码录入的数字比特流,如果FCEB1为高电平,主处理器能从SPCA751A接收数据;当FCEB1为低电平时,主处理器不能从SPCA751A获得比特流。对SPCA751A进行编程的流程图如图5所示。

图5 对SPCA751A编程流程图

MP3播放系统分为便携式和非便携式两种。对于非便携式,要考虑和其他CD音乐格式的共容性。对于便携式系统,主要考虑的是其体积小巧、低功耗、高容量、低价格。

系统简介

便携式MP3播放器的系统框图如图1所示,各部分的功能说明如下:

图1 便携式MP3播放器系统框图

1. 解码部分:这是MP3播放器的核心部件,采用硬件解码技术。

2. 存储部分:目前一般采用32MB的FLASH存储器,32MB的存储器能够存储36分钟128kbps(达到CD音质)的音乐,如果是播放16kbps的压缩话音,可以存储4个小时的内容。

3. 接口部分:一般通过PC的并口或USB口进行MP3文件的下载,并口的传输速率较低,USB口的传输速率可以高达12Mbps。

4.电源管理:便携式MP3的体积小,只用1到2只AAA电池供电,因此采用低电压以及进行有效的功率管理是非常必要的。

音频解码芯片内部结构

SPCA751A是凌阳科技公司生产的单片信号处理芯片,是一个MPEG Layer2.5音频专用解码芯片,已经广泛应用于一些便携式的MP3播放器设计中。它可支持对8—320Kbps基本数据流的解码,支持的取样频率范围为8KHz—48KHz,非常适合于MPEG的音频解码,并带有数字语音录音的MPEG播放模块,具有很高的性能/价格比。解码后的信号是可以直接输出到DAC的立体声、单声道或双声道的数字信号,SPCA751A与DAC的接口是可编程的。只要通过通用的串行I/O口和控制接口就能对MPEG比特流进行输入/输出和回放控制,系统控制器能很轻易的对MPEG音频信号进行解码。通过一个通用的可编程I2S接口,就能把一解码的音频PCM数据输出到外部的DAC中,因此,大多数常用的音频DAC都能和SPCA751A兼容。

对于嵌入式的语音录音,SPCA751A具有高品质的10位8KHz采样频率的ADC。基于SACM_S480或者SACM_S3200的运算法则,语音可以分别被压缩到4.8Kbps和32Kbps,而保持原始的语音效果。

SPCA751A使用的电源为3.0V"3.6V,它可以从其本身使用的16.934MHz晶振通过锁相环与系统时钟同步。SPCA751A信号处理器的工作频率可以达到34MHz而功耗很少,这就使得SPCA751A特别适合于便携式系统。

SPCA751A芯片的内部功能如图2所示,其主控制器只要具有足够的I/O口、能访问闪存和驱动LCD即可。

图2 SPCA751A内部功能图

为了适合数字录音应用的需要,SPCA751A有一个适合于语音波段的Σ-ΔADC,转换器的电路包括两个主要模块:ADC模块和内部参考偏置电压模块,后者为一个带有10位谐和音的15位数据格式。

ADC模块包括麦克风放大器、一个可编程增益放大器(PGA)、一个模拟过采样调节器和十进制数据滤波器。PGA增益可以从-12dB到12dB(-12,-6,0,6,12dB),当过采样信号频率为1.024MHz时,调节器是一个Σ-Δ反馈回路, 它完成微分模拟信号输入到脉冲密度调整单比特数字信号输出的转换。

图3 MPEG音频播放器系统框图

CEI表示主控制器是否可以接收数据 设置初始化参数:IDF+512字节数据 设置比特流:ID6+512字节比特流 设置命令:ID(低位字节)+命令(高位字节)

硬件设计

SPCA751A是单片的CMOS微处理器,是实时的MPEG音频解码和语音录音的专用芯片。主处理器通过串行控制口/I/O接口的命令控制SPCA751A对MPEG语音数据进行解码,主处理器也可以根据该接口检测解码过程。MPEG音频播放器系统框图如图3所示。SPCA751A与主控制器的连接如图4所示。

图4 SPCA751A与主控制器的连接

软件设计

SPCA751A工作于两种模式,MP3模式和数字语音录音(DVR)模式。在MP3模式,SPCA751A解码输入的比特流,发送到SPCA751A的数据作为输入数据。当FCEB1为高电平(缺省)时,主处理器发送比特流到SPCA751A;当FCEB1为低电平时,表明SPCA751A处于忙碌状态,这时,主处理器不能发任何数据到SPCA751A。在DVR模式,SPCA751A编/解码录入的数字比特流,如果FCEB1为高电平,主处理器能从SPCA751A接收数据;当FCEB1为低电平时,主处理器不能从SPCA751A获得比特流。对SPCA751A进行编程的流程图如图5所示。

图5 对SPCA751A编程流程图

USB 电源管理 电压 DAC 嵌入式 ADC LCD 电路 放大器 滤波器 CMOS DSP 编码器 相关文章:

- 基于USB的通用无线传输接口设计(09-20)

- 索尼VRD-MC1 DVD刻录机解析(09-24)

- USB On-The-Go 技术概述(09-16)

- 谈关于非编网络的管理及其维护(下)(10-02)

- 打破瓶颈,以技术驱动液晶电视升级换代(11-26)

- 高速USB OTG--便携设备绝佳的互连解决方案(11-18)