CMOS图像传感器用像素级双采样存储技术

时间:07-25

来源:互联网

点击:

1 前言

近些年来,随着CMOS技术的飞速发展,以及持续增加的应用需求,CMOS图像传感器技术得以迅速发展。CMOS图像传感器具有高度集成化、功耗低、单一工作电压、局部像素可编程随机读取等优点。但随着应用的需要,CMOS图像传感器的动态范围有待进一步提高,如典型的CMOSAPS(ActivePixelSensor)图像传感器动态范围为65~75dB,难于满足更宽照度范围摄像场景要求。一般来说,具有较高动态范围的传感器可以探测更宽的场景照度范围,从而可以产生更多细节的图像,可以说,动态范围在一定意义上,决定着CMOS图像传感器的质量。CMOSAPS图像传感器动态范围的扩展可采用各种方法,其中多次曝光技术是一种较为有效的方法,其在获得高动态范围的同时,有较高的信噪比SNR。采用多次曝光方法,一幅场景以不同的曝光时间被摄像几次,所捕获图像用于组合成更高动态范围的图像,曝光次数愈多,信号变化范围愈均匀,但多于两次的曝光,一般需要在片上或片外存储器支持,信号处理复杂,使传感器的帧频受到限制,如果在像素内应用两次曝光采样存储的方法,可在扩展动态范围基础上,适合于高速应用场合。

2 像素级采样存储技术的工作原理

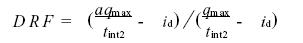

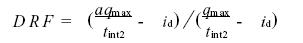

为了扩展CMOS图像传感器的动态范围,可应用两次曝光方法,即一幅场景用长积分时间曝光和短积分时间曝光摄像两次,两幅图像组合成一幅高动态范围的图像。从理论上说,短的积分时间图像捕获了场景高照度区域,长积分时间图像在足够的积分时间后,捕获了场景低照度区域,若短曝光时间为Tint2和长曝光时间为Tint1,则传感器的动态范围增强因子DRF为:

其中,qmax是传感器的最大阱容,a=Tint1/Tint2,id是暗电流。可见,当暗电流较小时,动态范围增强因子为a,同时理论分析表明双采样技术也可获得较高信噪比SNR。在CMOSAPS图像传感器中,采用传统的PD(PhotoDiode)APS像素结构,应用两次曝光方法,采用两个并行列信号处理路径实现双采样,可以同时读出两幅图像,虽然可获得宽动态范围的图像,但图像组合处理在片外执行,使得图像的实时处理速度受到一定的限制,难于满足高速应用场合的要求。

为了能够在扩展动态范围同时,且适合于高速应用场合,一种可行的方法是应用像素级采样存储技术,将曝光采样及图像组合处理在像素内实现,这样可有效提高图像的实时处理速度。为此,人们对像素级的采样存储技术进行了广泛的研究,几种可能的像素单元结构如图1所示。图1(a)中,采样保持电路中只采用MOS开关,这种结构虽然可获得较小的面积,但读出数据时,与CMOSPPS(PassivePixelSensor)像素结构类似,容易受噪声的干扰,因而SNR较差,并且读取一次数据后,像素内存储器C1上数据信息被毁坏,而实际应用中往往希望能够对像素数据多次读取,这需要存储电容上的电压值在读取期间保持不变,因此这种结构难于获得可接受的效果。

图1像素级的采样存储技术:(a)只用MOS开关;(b)采用单级缓冲器;(c)采用两级缓冲器

为了改善读出噪声,并且适合于多次读取的应用,可在存储电容C1和读出选通开关之间增加缓冲器A2,如图1(b)所示,缓冲器一般采用简单的源极跟随器配置结构,和典型的CMOSAPS像素结构相似,这可以有效改善像素的性能,但增加了像素面积。所报道的应用像素存储技术的CMOS图像传感器大多采用了这种结构,在这种结构中,在对光敏二极管上像素信息采样期间,二极管中光生电荷与存储电容C1共享,当采样开关打开时,由于MOS开关的非理想特性,导致电荷注入效应,引起采样误差,为了减小这种效应,在像素设计时,需要使光电二极管电容与存储电容的比值最佳化,通常使两者近似相等。为了提高光生电荷的收集效率,改善SNR,一般光敏二极管有较大的电容,这使得存储电容也应当具有差不多同样的量值,而源极跟随器A2栅极节点处的寄生电容相对较小,难于满足存储电容的需要,所以通常采用CMOS工艺中可行的具有良好性能的MOS电容来增加存储电容,由于版图设计规则的要求,使像素面积有较大的增加。

为了实现像素级的双采样和图像组合处理,可采用图1(b)类似的像素结构,首先进行长时间积分曝光,采样时,长积分时间的光生电荷在光敏二极管电容与存储电容间共享,然后进行短积分时间曝光,使长短两次积分时间曝光的光生电荷在光敏二极管内直接组合,从而获得动态范围的改善。在这种像素结构中曝光模式采用了传统的滚动曝光,而在一些工业和科学应用中,常需要对快速运动的目标或脉冲光照摄像,若采用滚动曝光模式将导致严重的运动失真,此时应采用具有同步曝光模式,即所有像素同时积分曝光,随后将信号电荷存储到像素内的采样保持电容,一直到读出。如果使这种结构像素工作于同步曝光模式,由于图像直接组合处理在光敏二极管内进行,若在像素数据读出的同时进行曝光采样将毁坏当前帧的数据,所以数据的读出和曝光不能同时进行,这将极大限制了传感器的数据处理速度。因此,这种像素双采样方法虽然可以获得动态范围的改善,但是难于应用于需要同步曝光的高速应用。

可见要适合于同步曝光的高速应用,双采样图像的组合处理不能在光敏二极管内直接进行,而只能在像素内的存储器内进行,一种方法是在图1(b)结构的基础上在像素内增加另一路采样保持电路,如文献[14]提出的可以直接帧差读出的像素结构。但是,在这种像素结构中,需要两个较大的存储电容,使像素面积较大,这对于巨大像素阵列传感器将是难于接受的。为了能够减小存储电容所占面积,可采用图1(c)所示的结构,在光敏二极管和存储电容间增加一级缓冲器A1,这样在良好SNR和允许多次读取的基础上,如果存储能力能够满足应用需求,则可以采用较小的存储电容。一般,电容的存储能力与漏电流导致的电容漏电和光导致电容的放电有关,随着CMOS工艺技术的不断改善、有效光掩蔽方法应用及其它工艺技术如将PD置于阱中、采用保护环隔离PD等,使电容的存储能力得到了极大改善,使得源随器栅节点处较小寄生电容可以满足存储电容的需要。这样虽然在像素内增加了一级缓冲器,但不再需要面积较大的额外MOS电容,从而可能使像素面积减少。

近些年来,随着CMOS技术的飞速发展,以及持续增加的应用需求,CMOS图像传感器技术得以迅速发展。CMOS图像传感器具有高度集成化、功耗低、单一工作电压、局部像素可编程随机读取等优点。但随着应用的需要,CMOS图像传感器的动态范围有待进一步提高,如典型的CMOSAPS(ActivePixelSensor)图像传感器动态范围为65~75dB,难于满足更宽照度范围摄像场景要求。一般来说,具有较高动态范围的传感器可以探测更宽的场景照度范围,从而可以产生更多细节的图像,可以说,动态范围在一定意义上,决定着CMOS图像传感器的质量。CMOSAPS图像传感器动态范围的扩展可采用各种方法,其中多次曝光技术是一种较为有效的方法,其在获得高动态范围的同时,有较高的信噪比SNR。采用多次曝光方法,一幅场景以不同的曝光时间被摄像几次,所捕获图像用于组合成更高动态范围的图像,曝光次数愈多,信号变化范围愈均匀,但多于两次的曝光,一般需要在片上或片外存储器支持,信号处理复杂,使传感器的帧频受到限制,如果在像素内应用两次曝光采样存储的方法,可在扩展动态范围基础上,适合于高速应用场合。

2 像素级采样存储技术的工作原理

为了扩展CMOS图像传感器的动态范围,可应用两次曝光方法,即一幅场景用长积分时间曝光和短积分时间曝光摄像两次,两幅图像组合成一幅高动态范围的图像。从理论上说,短的积分时间图像捕获了场景高照度区域,长积分时间图像在足够的积分时间后,捕获了场景低照度区域,若短曝光时间为Tint2和长曝光时间为Tint1,则传感器的动态范围增强因子DRF为:

其中,qmax是传感器的最大阱容,a=Tint1/Tint2,id是暗电流。可见,当暗电流较小时,动态范围增强因子为a,同时理论分析表明双采样技术也可获得较高信噪比SNR。在CMOSAPS图像传感器中,采用传统的PD(PhotoDiode)APS像素结构,应用两次曝光方法,采用两个并行列信号处理路径实现双采样,可以同时读出两幅图像,虽然可获得宽动态范围的图像,但图像组合处理在片外执行,使得图像的实时处理速度受到一定的限制,难于满足高速应用场合的要求。

为了能够在扩展动态范围同时,且适合于高速应用场合,一种可行的方法是应用像素级采样存储技术,将曝光采样及图像组合处理在像素内实现,这样可有效提高图像的实时处理速度。为此,人们对像素级的采样存储技术进行了广泛的研究,几种可能的像素单元结构如图1所示。图1(a)中,采样保持电路中只采用MOS开关,这种结构虽然可获得较小的面积,但读出数据时,与CMOSPPS(PassivePixelSensor)像素结构类似,容易受噪声的干扰,因而SNR较差,并且读取一次数据后,像素内存储器C1上数据信息被毁坏,而实际应用中往往希望能够对像素数据多次读取,这需要存储电容上的电压值在读取期间保持不变,因此这种结构难于获得可接受的效果。

图1像素级的采样存储技术:(a)只用MOS开关;(b)采用单级缓冲器;(c)采用两级缓冲器

为了改善读出噪声,并且适合于多次读取的应用,可在存储电容C1和读出选通开关之间增加缓冲器A2,如图1(b)所示,缓冲器一般采用简单的源极跟随器配置结构,和典型的CMOSAPS像素结构相似,这可以有效改善像素的性能,但增加了像素面积。所报道的应用像素存储技术的CMOS图像传感器大多采用了这种结构,在这种结构中,在对光敏二极管上像素信息采样期间,二极管中光生电荷与存储电容C1共享,当采样开关打开时,由于MOS开关的非理想特性,导致电荷注入效应,引起采样误差,为了减小这种效应,在像素设计时,需要使光电二极管电容与存储电容的比值最佳化,通常使两者近似相等。为了提高光生电荷的收集效率,改善SNR,一般光敏二极管有较大的电容,这使得存储电容也应当具有差不多同样的量值,而源极跟随器A2栅极节点处的寄生电容相对较小,难于满足存储电容的需要,所以通常采用CMOS工艺中可行的具有良好性能的MOS电容来增加存储电容,由于版图设计规则的要求,使像素面积有较大的增加。

为了实现像素级的双采样和图像组合处理,可采用图1(b)类似的像素结构,首先进行长时间积分曝光,采样时,长积分时间的光生电荷在光敏二极管电容与存储电容间共享,然后进行短积分时间曝光,使长短两次积分时间曝光的光生电荷在光敏二极管内直接组合,从而获得动态范围的改善。在这种像素结构中曝光模式采用了传统的滚动曝光,而在一些工业和科学应用中,常需要对快速运动的目标或脉冲光照摄像,若采用滚动曝光模式将导致严重的运动失真,此时应采用具有同步曝光模式,即所有像素同时积分曝光,随后将信号电荷存储到像素内的采样保持电容,一直到读出。如果使这种结构像素工作于同步曝光模式,由于图像直接组合处理在光敏二极管内进行,若在像素数据读出的同时进行曝光采样将毁坏当前帧的数据,所以数据的读出和曝光不能同时进行,这将极大限制了传感器的数据处理速度。因此,这种像素双采样方法虽然可以获得动态范围的改善,但是难于应用于需要同步曝光的高速应用。

可见要适合于同步曝光的高速应用,双采样图像的组合处理不能在光敏二极管内直接进行,而只能在像素内的存储器内进行,一种方法是在图1(b)结构的基础上在像素内增加另一路采样保持电路,如文献[14]提出的可以直接帧差读出的像素结构。但是,在这种像素结构中,需要两个较大的存储电容,使像素面积较大,这对于巨大像素阵列传感器将是难于接受的。为了能够减小存储电容所占面积,可采用图1(c)所示的结构,在光敏二极管和存储电容间增加一级缓冲器A1,这样在良好SNR和允许多次读取的基础上,如果存储能力能够满足应用需求,则可以采用较小的存储电容。一般,电容的存储能力与漏电流导致的电容漏电和光导致电容的放电有关,随着CMOS工艺技术的不断改善、有效光掩蔽方法应用及其它工艺技术如将PD置于阱中、采用保护环隔离PD等,使电容的存储能力得到了极大改善,使得源随器栅节点处较小寄生电容可以满足存储电容的需要。这样虽然在像素内增加了一级缓冲器,但不再需要面积较大的额外MOS电容,从而可能使像素面积减少。

CMOS 传感器 电压 电流 电路 电容 二极管 电子 相关文章:

- 数字电视条件接收卡SoC SM1658的硬件结构及实现方法(下)(09-07)

- 谈关于非编网络的管理及其维护(下)(10-02)

- 基于DSP与双目CMOS摄像头的数字图像处理系统(10-06)

- MS6335+MS6863 : 面向便携式设备的低成本立体声切换方案(10-13)

- TI产品技术分析锦集(11-09)

- 四种新型高清显示技术优劣对比 (11-30)