基于ISPl362 U盘MP3播放器设计

时间:07-24

来源:互联网

点击:

播放器与存储器的一体化设计对。MP3播放器的便携性起了关键性的作用,但与此同时,它又带来了很多新的问题。比如存储容量固定,如果想装下更多的歌曲只能去购买新的产品,造成了巨大的浪费。另一方面,一体化又限制了MP3播放器在其它领域的应用,比如汽车电子等。于是,将存储器与播放器分离,成为MP3的另一发展方向,也是开发这款U盘MP3播放器的意义所在。

主要芯片简介

AT89C5lSNDl是ATMEL推出的基于8位C5l MCU内核的MP3解码器芯片。它内置MP3硬件解码器,支持48kHz、44.1kHz、32kHz、24kHz、22.05kHz及l 6kHz采样频率,具有重低音、中音、高音均衡控制和重低环绕声效果。它可以适应市场上不同DAC的可编程音频输出接口,兼容PCM和12S格式。内置2304B RAM和64KB Flash程序空间,方便用户增加复杂的功能。并通过内置锁相环提供MP3和音频时钟以及USB时钟。

要想读取U盘,USB主机控制器必不可少。为了将来进一步升级系统,本文选用了功能强大的LISB一OTG芯片ISPl362。ISPl362在单芯片上集成了0TG控制器、高级主机控制器和外设控制器。ISPl362的OTG控制器完全兼容LISB2.0以及On-The-Go Supplement 1.0协议,主机和设备控制器兼容USB 2.0协议,并支持l2Mbps的全速传输和1.5Mbps的低速传输。

系统硬件结构

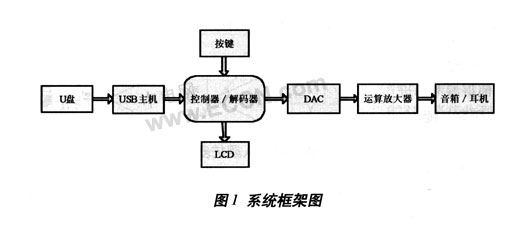

整个系统的搭建围绕AT89C51SNDl进行,如图1所示。由于其内部具有硬件解码器,因此电路构成并不复杂。首先由单片机控制ISPl362,将U盘中的MP3文件读取出来,送到硬件解码器进行解码。解码之后由数字音频接口将数字信号传送至音频DAC CS4330,转换之后产生音频信号。由于DAC输出的信号功率有限,在后端又加入了运算放大器,经过放大之后的信号就可以直接输出给音箱或耳机等设备了。

除了这些基本的总线连接,ISPl362还需要连接一些特殊的控制引脚:

AO:用于决定控制器处于命令状态还是数据状态:O表示数据状态,l表示命令状态;

Al:用于决定控制器工作于主机还是设备控制模式:O表示处于主机控制(HC)模式;1表示处于设备控制(DC)模式。

OTG-MODE接至MCU的P1.5。P1.5=O时表示处于OTG工作状态,P1.5=1贝U表示处于非OTG状态。

INTl_USB、INT2_USB分别接至MCU的INTO和INTl引脚,用以产生中断。

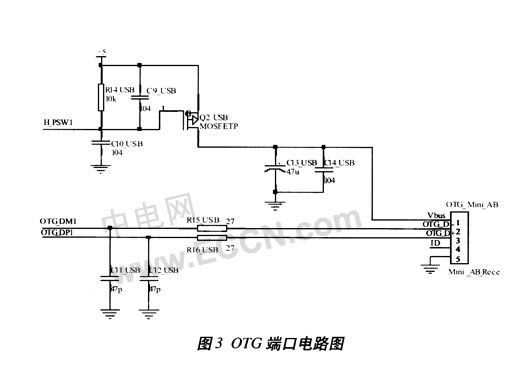

ISPl362有两个USB端口,分别是OTG端口和主机端口。因为OTG端口包含了主机功能,所以系统中使用0TG端口来连接U盘。根据USB2.O协议,USB主机需要2个15k的下拉电阻,但OTG端口同时又可作为设备端口使用,而设备是没有下拉电阻的。因此ISPl362提供了"软连接"机制,通过内部的寄存器来控制电阻的连接与否。所以在硬件设计时并不需要在外部加下拉电阻。而H-PSW1为开漏输出,因此加入了一个10kΩ的上拉电阻R14_USB。如图3所示。

在开始播放。MP3文件之前,需要一系列初始化操作。这些操作是通过设置AT89C51SNDlC及ISPl362内部的相关寄存器来完成的。

AT89C51SNDlC的初始化

为了正常播放:MP3文件,首先要对主控制器AT89C5lSNDlc进行以下几方面的设置。

锁相环初始化

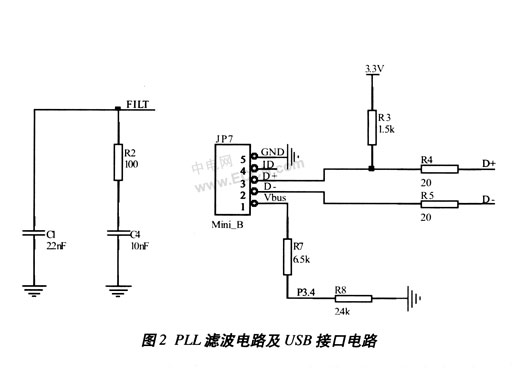

MP3解码器和音频输出接口使用的都是内部锁相环提供的时钟。锁相环的初始化是通过设置PLLCON、PLLNdiv和PLLNdiv来完成的。其输出频率的计算公式为:PLLclk=OSCclk×(R+1)/(N+1)。

MP3解码器初始化

MP3解码器的初始化需要对MP3CON和MP3CLK进行设置。MP3解码器分缺少数据中断和校验中断两类中断,在MP3CON中可以对其进行设置。简单处理可以采用查询标志位方式,避免使用中断。MP3解码器对时钟有一定的要求,MPEGI格式的MP3数据要求最低时钟为21MHz,MPEG II格式为10.5MHz。该时钟计算公式为:MP3clk=PLLclk/(MPSD4:0+1)。

音频输出接口初始化

得到两个声道串行数据前需先对音频输出接口的AuDCON0和AIJDCONl中的相关部分进行正确的设置。配合DAC芯片CS4330,其设置如下:输出3 2位数据格式(DSIZ=1),声道选择信号中的高电平为左声道(POL=1),选择256·Fs的数据速率(HLR=O),选择MP3解码器的输出为数据源(SRC=0),18位数据右对齐(JUST4:0=14)。为了听到正常的声音,还需根据MP3的采样率设置MP3CLK来得到正确的音频输出接口的时钟,该时钟的计算公式为:AUDclk=PLLclk/(AUCD4:0+1)。

主要芯片简介

AT89C5lSNDl是ATMEL推出的基于8位C5l MCU内核的MP3解码器芯片。它内置MP3硬件解码器,支持48kHz、44.1kHz、32kHz、24kHz、22.05kHz及l 6kHz采样频率,具有重低音、中音、高音均衡控制和重低环绕声效果。它可以适应市场上不同DAC的可编程音频输出接口,兼容PCM和12S格式。内置2304B RAM和64KB Flash程序空间,方便用户增加复杂的功能。并通过内置锁相环提供MP3和音频时钟以及USB时钟。

要想读取U盘,USB主机控制器必不可少。为了将来进一步升级系统,本文选用了功能强大的LISB一OTG芯片ISPl362。ISPl362在单芯片上集成了0TG控制器、高级主机控制器和外设控制器。ISPl362的OTG控制器完全兼容LISB2.0以及On-The-Go Supplement 1.0协议,主机和设备控制器兼容USB 2.0协议,并支持l2Mbps的全速传输和1.5Mbps的低速传输。

系统硬件结构

整个系统的搭建围绕AT89C51SNDl进行,如图1所示。由于其内部具有硬件解码器,因此电路构成并不复杂。首先由单片机控制ISPl362,将U盘中的MP3文件读取出来,送到硬件解码器进行解码。解码之后由数字音频接口将数字信号传送至音频DAC CS4330,转换之后产生音频信号。由于DAC输出的信号功率有限,在后端又加入了运算放大器,经过放大之后的信号就可以直接输出给音箱或耳机等设备了。

除了这些基本的总线连接,ISPl362还需要连接一些特殊的控制引脚:

AO:用于决定控制器处于命令状态还是数据状态:O表示数据状态,l表示命令状态;

Al:用于决定控制器工作于主机还是设备控制模式:O表示处于主机控制(HC)模式;1表示处于设备控制(DC)模式。

OTG-MODE接至MCU的P1.5。P1.5=O时表示处于OTG工作状态,P1.5=1贝U表示处于非OTG状态。

INTl_USB、INT2_USB分别接至MCU的INTO和INTl引脚,用以产生中断。

ISPl362有两个USB端口,分别是OTG端口和主机端口。因为OTG端口包含了主机功能,所以系统中使用0TG端口来连接U盘。根据USB2.O协议,USB主机需要2个15k的下拉电阻,但OTG端口同时又可作为设备端口使用,而设备是没有下拉电阻的。因此ISPl362提供了"软连接"机制,通过内部的寄存器来控制电阻的连接与否。所以在硬件设计时并不需要在外部加下拉电阻。而H-PSW1为开漏输出,因此加入了一个10kΩ的上拉电阻R14_USB。如图3所示。

在开始播放。MP3文件之前,需要一系列初始化操作。这些操作是通过设置AT89C51SNDlC及ISPl362内部的相关寄存器来完成的。

AT89C51SNDlC的初始化

为了正常播放:MP3文件,首先要对主控制器AT89C5lSNDlc进行以下几方面的设置。

锁相环初始化

MP3解码器和音频输出接口使用的都是内部锁相环提供的时钟。锁相环的初始化是通过设置PLLCON、PLLNdiv和PLLNdiv来完成的。其输出频率的计算公式为:PLLclk=OSCclk×(R+1)/(N+1)。

MP3解码器初始化

MP3解码器的初始化需要对MP3CON和MP3CLK进行设置。MP3解码器分缺少数据中断和校验中断两类中断,在MP3CON中可以对其进行设置。简单处理可以采用查询标志位方式,避免使用中断。MP3解码器对时钟有一定的要求,MPEGI格式的MP3数据要求最低时钟为21MHz,MPEG II格式为10.5MHz。该时钟计算公式为:MP3clk=PLLclk/(MPSD4:0+1)。

音频输出接口初始化

得到两个声道串行数据前需先对音频输出接口的AuDCON0和AIJDCONl中的相关部分进行正确的设置。配合DAC芯片CS4330,其设置如下:输出3 2位数据格式(DSIZ=1),声道选择信号中的高电平为左声道(POL=1),选择256·Fs的数据速率(HLR=O),选择MP3解码器的输出为数据源(SRC=0),18位数据右对齐(JUST4:0=14)。为了听到正常的声音,还需根据MP3的采样率设置MP3CLK来得到正确的音频输出接口的时钟,该时钟的计算公式为:AUDclk=PLLclk/(AUCD4:0+1)。

汽车电子 MCU 解码器 DAC USB 电路 单片机 放大器 总线 仿真 电阻 电子 相关文章:

- SMARTCAR软件平台实现汽车电子系统软件的整体设计(03-30)

- 汽车电子须知 汽车网线与CAN总线的标准(04-17)

- 导致汽车电子电路故障的主要原因(04-17)

- IEEE 1394的汽车电子版IDB-1394(08-18)

- 汽车电子测试系统解决方案综述(01-08)

- 基于Cortex-M3的MP3播放器设计(04-13)