基于DSP的MP3解码系统设计

时间:07-24

来源:互联网

点击:

基于DSP实现MP3解码系统的设计,采用高性能的立体声音频Codec芯片TLV320A IC23 作为音频信号数模转换,DSP的两个McBSP与其连接,分别作为配置接口和音频数字接口,配置接口设置为SP I模式。USB与DSP接口实现MP3数据流与PC机之间的上传与下载,存取MP3文件方便,存储MP3文件的媒介选取大容量的存储设备CF卡,系统选用可编程逻辑器件CPLD控制USB及CF卡的读写和片选。实验证明该系统可以高质量完成MP3解码、播放。

随着数字视频和图像处理的发展,数字音频技术也正在提高,尤其是以ISO / IEC 为基础的MPEG技术。MP3是MPEG Audio LayerⅢ的缩写,它是Hi - Fi级音频压缩的国际标准。目前,市场上的MP3解码基本上都是采用专用芯片解码,采用专用芯片解码体积大,支持的音频格式有限。我们采用在DSP芯片上用C语言进行软解码,软解码比较灵活,可移植性好,易于升级,解码质量可通过软件参数设定,通用性好。

硬件系统结构

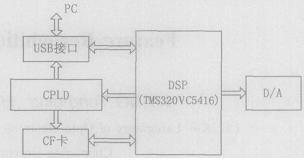

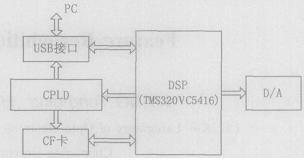

DSP的MP3解码系统硬件框图如图1所示,我们采用了低功耗的DSP芯片TMS32VC5416进行软件解码,32M的CF卡作为存储MP3文件的媒介,USB接口作为与PC机进行通讯接口,传输数据速度快,可以在PC机下载、上传MP3,可编程逻辑器件CPLD (选用EPM7128SL84)用于产生CF卡与USB 接口芯片的片选以及控制其读写。

TMS320VC5416定点DSP

TI公司的TMS320VC5416 定点运算数字信号处理器(DSP) ,其功耗低,性能高,内部采用一种改进型的哈佛总线结构:一条程序总线,3条数据总线,数据总线宽度为16位。分开的数据和指令空间使该芯片具有高度的并行操作能力,在单周期内允许指令和数据同时存取,再加上其高度优化的指令集,使得该芯片具有很高的运算速度,最高可达160MIPS。

图1 系统的硬件框图

音频传输、播放系统

TLV320A IC23介绍

D /A采用TLV320A IC23 芯片,TLV320AIC23 (以下简称AIC23)是一款高性能的立体声音频Codec芯片,内置耳机输出放大器,支持MIC和LINE IN两种输入方式(二选一) ,且对输入和输出都具有可编程增益调节。AIC23 的模数转换(ADCs) 和数模转换(DACs)部件高度集成在芯片内部,采用了先进的Sigma-delta过采样技术,可以在8K到96K的频率范围内20、24 bit和32 bit的采样,ADC和DAC的输出信噪比分别可以达到90dB 和100dB。与此同时,AIC23还具有很低的能耗,回放模式下功率仅为23 mW,省电模式下更是小于15uW。由于具有上述优点,使得AIC23是一款非常理想的音频模拟I/O器件。

AIC23与DSP的数字音频接口设计

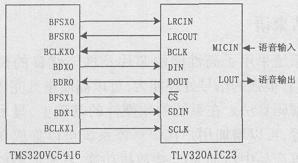

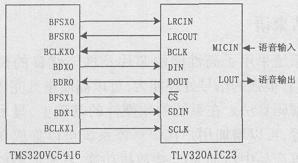

DSP与AIC23连接如图2 所示,利用USB1. 1接口器件PDIUSBD12可编程的时钟频率输出12M作为立体声音频Codec芯片AIC23的时钟输入CLK12M。AIC23的配置接口支持IαC模式,也支持SPI模式,系统采用DSP的一个McBSP用SPI模式跟AIC23连接。

图2 TLV320A IC23与DSP连接图

DSP配置为主模式,AIC23 配置为从模式。AIC23 输出串行数据,DSP的MCBSP串口6个引脚使数据通路和控制通路与AIC23 相连。数据由BDX0、BDR0 传输,同步信号的控制由BFSX0、BFSR0、BCLKX0 来实现。数字音频接口采用DSP模式,该模式与TI公司DSP的MCBSP串口兼容,该模式时序如图3。由图知,在LRCIN /LRCOUT信号的下降沿开始进行数据的传输,先左声道数据传输,然后右声道数据传输。

图3 A IC23的DSP模式时序

DSP需要处理来自和发向AIC23的数据,从而达到采集和播放声音。McBSP与CPU 通信用DMA 方式,通过DMA 收到或发送完一组单元,再给CPU 中断。采用DMA的方式,即串口每发送或接收到一个单元,都会自动触发DMA将其搬送到一个内部的Buffer,等Buffer满了再通过中断方式告诉CPU处理。在DMA的中断服务程序中为了可靠可以把这个Buffer的数据再拷贝到另一个待处理的空间,即两级Buffer,然后置标志位,CPU在主程序中查询标志位然后作出相应的处理。DMA 操作的Buffer可以通过寄存器配置。

USB接口实现

USB接口采用高性能、并行总线的USB接口器件PD IUSBD12 (以下简称D12) ,D12符合通用串行总线USB 1. 1 版规范,可与DSP微控制器实现高速并行接口[ 5 - 6 ] ,D12与DSP连接如图4所示。

图4 D12与DSP连接图

由CPLD产生D12的片选、以及控制对D12的读写; ALE接低电平,表示一个独立的地址和数据总线配置; D12 的A0 脚与DSP的A0相连,控制D12 的命令和数据状态。

CF卡接口设计

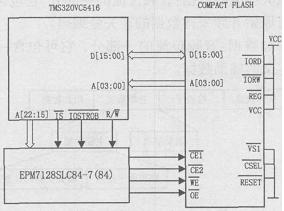

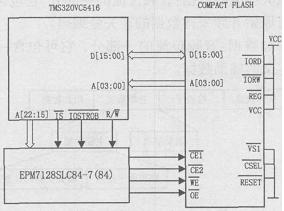

CF卡是一种小型化、大容量、低功耗、智能型的存储媒体,在便携式设备中应用广泛。以Flash Memory(闪存)为主要载体,内部用微处理器进行时序控制和存储管理。CF卡与DSP连接如下图5 所示。

图5 CF卡与DSP连接

CF卡的A3~A0为数据、命令、或状态寄存器地址线,D15~D0为数据总线,可16位或8位访问,当片选信号CE1#和CE2#同时为低电平时,为16位访问格式;当CE1#置高,CE2#为低电平时,为8位访问格式。CF的存取方式有三种:Memory方式、I/O 方式、True IDE方式,该系统中CF卡工作模式选取上电默认方式,即:Memory方式,片选CE1 #、CE2 #由可编程逻辑器件EPM7128SL84对DSP的8位地址A15~A22译码产生。CF卡工作电压为5 V或3. 3 V,设计选用3. 3 V工作电压,便于数据输出与地址可直接与DSP相接。

随着数字视频和图像处理的发展,数字音频技术也正在提高,尤其是以ISO / IEC 为基础的MPEG技术。MP3是MPEG Audio LayerⅢ的缩写,它是Hi - Fi级音频压缩的国际标准。目前,市场上的MP3解码基本上都是采用专用芯片解码,采用专用芯片解码体积大,支持的音频格式有限。我们采用在DSP芯片上用C语言进行软解码,软解码比较灵活,可移植性好,易于升级,解码质量可通过软件参数设定,通用性好。

硬件系统结构

DSP的MP3解码系统硬件框图如图1所示,我们采用了低功耗的DSP芯片TMS32VC5416进行软件解码,32M的CF卡作为存储MP3文件的媒介,USB接口作为与PC机进行通讯接口,传输数据速度快,可以在PC机下载、上传MP3,可编程逻辑器件CPLD (选用EPM7128SL84)用于产生CF卡与USB 接口芯片的片选以及控制其读写。

TMS320VC5416定点DSP

TI公司的TMS320VC5416 定点运算数字信号处理器(DSP) ,其功耗低,性能高,内部采用一种改进型的哈佛总线结构:一条程序总线,3条数据总线,数据总线宽度为16位。分开的数据和指令空间使该芯片具有高度的并行操作能力,在单周期内允许指令和数据同时存取,再加上其高度优化的指令集,使得该芯片具有很高的运算速度,最高可达160MIPS。

图1 系统的硬件框图

音频传输、播放系统

TLV320A IC23介绍

D /A采用TLV320A IC23 芯片,TLV320AIC23 (以下简称AIC23)是一款高性能的立体声音频Codec芯片,内置耳机输出放大器,支持MIC和LINE IN两种输入方式(二选一) ,且对输入和输出都具有可编程增益调节。AIC23 的模数转换(ADCs) 和数模转换(DACs)部件高度集成在芯片内部,采用了先进的Sigma-delta过采样技术,可以在8K到96K的频率范围内20、24 bit和32 bit的采样,ADC和DAC的输出信噪比分别可以达到90dB 和100dB。与此同时,AIC23还具有很低的能耗,回放模式下功率仅为23 mW,省电模式下更是小于15uW。由于具有上述优点,使得AIC23是一款非常理想的音频模拟I/O器件。

AIC23与DSP的数字音频接口设计

DSP与AIC23连接如图2 所示,利用USB1. 1接口器件PDIUSBD12可编程的时钟频率输出12M作为立体声音频Codec芯片AIC23的时钟输入CLK12M。AIC23的配置接口支持IαC模式,也支持SPI模式,系统采用DSP的一个McBSP用SPI模式跟AIC23连接。

图2 TLV320A IC23与DSP连接图

DSP配置为主模式,AIC23 配置为从模式。AIC23 输出串行数据,DSP的MCBSP串口6个引脚使数据通路和控制通路与AIC23 相连。数据由BDX0、BDR0 传输,同步信号的控制由BFSX0、BFSR0、BCLKX0 来实现。数字音频接口采用DSP模式,该模式与TI公司DSP的MCBSP串口兼容,该模式时序如图3。由图知,在LRCIN /LRCOUT信号的下降沿开始进行数据的传输,先左声道数据传输,然后右声道数据传输。

图3 A IC23的DSP模式时序

DSP需要处理来自和发向AIC23的数据,从而达到采集和播放声音。McBSP与CPU 通信用DMA 方式,通过DMA 收到或发送完一组单元,再给CPU 中断。采用DMA的方式,即串口每发送或接收到一个单元,都会自动触发DMA将其搬送到一个内部的Buffer,等Buffer满了再通过中断方式告诉CPU处理。在DMA的中断服务程序中为了可靠可以把这个Buffer的数据再拷贝到另一个待处理的空间,即两级Buffer,然后置标志位,CPU在主程序中查询标志位然后作出相应的处理。DMA 操作的Buffer可以通过寄存器配置。

USB接口实现

USB接口采用高性能、并行总线的USB接口器件PD IUSBD12 (以下简称D12) ,D12符合通用串行总线USB 1. 1 版规范,可与DSP微控制器实现高速并行接口[ 5 - 6 ] ,D12与DSP连接如图4所示。

图4 D12与DSP连接图

由CPLD产生D12的片选、以及控制对D12的读写; ALE接低电平,表示一个独立的地址和数据总线配置; D12 的A0 脚与DSP的A0相连,控制D12 的命令和数据状态。

CF卡接口设计

CF卡是一种小型化、大容量、低功耗、智能型的存储媒体,在便携式设备中应用广泛。以Flash Memory(闪存)为主要载体,内部用微处理器进行时序控制和存储管理。CF卡与DSP连接如下图5 所示。

图5 CF卡与DSP连接

CF卡的A3~A0为数据、命令、或状态寄存器地址线,D15~D0为数据总线,可16位或8位访问,当片选信号CE1#和CE2#同时为低电平时,为16位访问格式;当CE1#置高,CE2#为低电平时,为8位访问格式。CF的存取方式有三种:Memory方式、I/O 方式、True IDE方式,该系统中CF卡工作模式选取上电默认方式,即:Memory方式,片选CE1 #、CE2 #由可编程逻辑器件EPM7128SL84对DSP的8位地址A15~A22译码产生。CF卡工作电压为5 V或3. 3 V,设计选用3. 3 V工作电压,便于数据输出与地址可直接与DSP相接。

DSP USB CPLD C语言 总线 MIPS 放大器 ADC DAC 电压 滤波器 显示器 相关文章:

- 全面解读 嵌入式DSP上的视频编解码(08-19)

- 基于ADSP-TS201S的图像采集处理系统(08-12)

- 基于Blackfin533的H.264编码(08-18)

- 图形液晶显示模块在嵌入式系统中的应用(09-02)

- 基于DSP和FPGA的电视观瞄系统设计(09-02)

- TI手提多媒体设备解决方案(09-23)