基于MPEG-2算法的列车语音记录设备

时间:07-24

来源:互联网

点击:

前言

列车运行监控记录装置在铁路的安全运输过程中发挥了巨大的作用,但不足的是没有语音记录功能。为了解决这个问题,按照铁道部的技术要求,本文研究开发了一种新型列车语音记录设备。该设备主要用于对乘务员机车联控进行录音,并可协同监控装置分析行车事故,为机务部门和运输部门的科学管理提供新的技术手段。鉴于常见设备的技术指标及标准,对于语音的数字化,以16KHz的采样频率、16位量化精度进行采样,在编码方面,采用MPEG-2压缩编码方式。

硬件系统组成

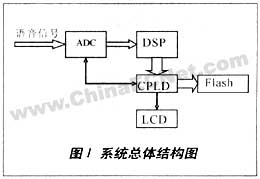

该语音记录设备如图1所示,整个系统由ADC、DSP、CPLD控制器,Flash大容量存储器及LCD显示屏等组成。

在本系统中,ADC用来完成信号的转换,数据格式在16、18、20位之间可选,DSP为系统的核心数字处理器,功能强大,完成数字信号的压缩编码,CPLD用于数据传送的控制以及对ADC、Flash和LCD显示屏等器件的初始化检测设置,Flash用来存储数据,LCD显示屏用来显示当前系统的状态,如运行等待和数据处理等。系统上电后,若有语音信号,则输入ADC,得到一串数字信号送入DSP进行数据压缩编码,经过压缩编码的数据由CPLD存储到Flash中,整个系统以流水线的方式工作,数据的采集、压缩编码和存储同时进行。

A/D转换器UDA1341TS

UDA1341TS是由Philips公司生产的一款单片立体声A/D、D/A转换器,工作电压为3.0V,信噪比为97dB,具有双通道输入功能,采样频率在16,32和44.1KHz之间可选。

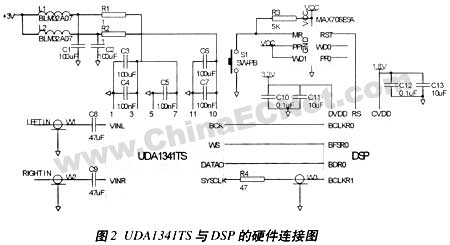

UDA1341TS与DSP构成语音信号采集系统,主要涉及到位采样时钟(BCK)、字同步时钟(WS)、采样数据输出(DATAO),系统时钟输入(SYSCLK)这几个对时序有要求的引脚。系统中,DATAO作为输出引脚,与DSP的BDR0引脚相连;BCK、WS、SYSCLK作为输入引脚,其时序由DSP供给。UDA1341TS的系统时钟只能是256Fs、384Fs、512Fs,通过对状态寄存器的SC0位和SC1位编程可实现系统时钟的选择设置。这里Fs是语音信号的采样频率。在采样数据时,WS用来指明UDA1341TS的DATAO输出的有效数据。当系统对VINL(左声道)端口进行采样时,WS的上升沿表明一帧数据的起始,下降沿表明一帧数据的结束;当系统对VINR(右声道)端口进行采样时,WS的下降沿表明一帧数据的起始,上升沿表明一帧数据的结束。

UDA1341TS提供了一个L3端口,利用CPLD控制器对L3的L3DATA、L3MODE和L3CLOCK三个引脚进行编程,可以设置其内部的寄存器。当L3MODE引脚为低电平时,通过L3DATA引脚输入寄存器地址信息;当L3DATA引脚为高电平时,通过L3DATA引脚输入有关寄存器设置的数据信息(如设置芯片系统时钟频率、数据输入格式、芯片工作模式等)。UDA1341TS与DSP的McBSP(多通道缓冲同步串口)相连,各种同步信号由DSP产生,这样就保证了新数据的正常接收以及已接收数据的正常处理。UDA1341TS与DSP的硬件连接如图2所示。

语音编码器TMS320VC5402

数字语音信号的压缩需要大量的数字信号处理,一般单片机是无法完成的,所以本系统选用TI公司的DSP芯片TMS320VC5402(以下简称C5402)对语音信号进行压缩处理。

C5402通过它的MsBSP与语音采样转换器UDA1341TS通信。McBSP提供了全双工的通信机制,以及双缓存的发送寄存器和三缓存的接收寄存器,允许连续的数据流传输,数据宽度的8、12、16、20、24、32位之间可选;McBSP与ADC的通信通过BDR0引脚实现,通信过程的控制则由BCLKR0、BCLKR1、BFSR0等三条引脚实现。

CPLD低速控制

DSP作为高速的运算处理器不合适低速的控制应用。对UDA1341TS检测、初始化,对LCD的控制以及对Flash的存储控制都是低速的控制。本系统选用CPLD来完成这些工作。CPLD为Altera公司的EPM7128S,开发仿真环境为Altera公司的MAX-PLUSII。因为DSP的地址线A0、A1、A2要被某些芯片使用,所以选取A3-A7、A15共6根地址线和I/O空间选择信号IS的反共同产生系统中各芯片的选通信号。CPLD中的控制电路负责产生各种读写信号,如Flash的读信号MEM_RD和写信号MEM_WR等。

在该系统中,C5402要产生许多控制信号(如Flash程序页的选择信号PPG2-PPGO等),同时也要监视和读取外部的状态。因为C5402只有两个通用I/O引脚,所以用CPLD来对其进行I/O端口扩展。CPLD内部通过一个8位DFF触发器实现对数据的输出。另外,通过8个三态门,将8位输入状态放到C5402数据总线的低8位上。C5402有4个中断输入INTR3反—INTR0的反。CPLD的中断选择模块可以从最多8个外部中断信号中选择4个作为C5402的中断输入,提高了系统的灵活性。

软件设计

软件设计主要包括ADC的程序设计,语音数据的压缩编码等。

列车运行监控记录装置在铁路的安全运输过程中发挥了巨大的作用,但不足的是没有语音记录功能。为了解决这个问题,按照铁道部的技术要求,本文研究开发了一种新型列车语音记录设备。该设备主要用于对乘务员机车联控进行录音,并可协同监控装置分析行车事故,为机务部门和运输部门的科学管理提供新的技术手段。鉴于常见设备的技术指标及标准,对于语音的数字化,以16KHz的采样频率、16位量化精度进行采样,在编码方面,采用MPEG-2压缩编码方式。

硬件系统组成

该语音记录设备如图1所示,整个系统由ADC、DSP、CPLD控制器,Flash大容量存储器及LCD显示屏等组成。

在本系统中,ADC用来完成信号的转换,数据格式在16、18、20位之间可选,DSP为系统的核心数字处理器,功能强大,完成数字信号的压缩编码,CPLD用于数据传送的控制以及对ADC、Flash和LCD显示屏等器件的初始化检测设置,Flash用来存储数据,LCD显示屏用来显示当前系统的状态,如运行等待和数据处理等。系统上电后,若有语音信号,则输入ADC,得到一串数字信号送入DSP进行数据压缩编码,经过压缩编码的数据由CPLD存储到Flash中,整个系统以流水线的方式工作,数据的采集、压缩编码和存储同时进行。

A/D转换器UDA1341TS

UDA1341TS是由Philips公司生产的一款单片立体声A/D、D/A转换器,工作电压为3.0V,信噪比为97dB,具有双通道输入功能,采样频率在16,32和44.1KHz之间可选。

UDA1341TS与DSP构成语音信号采集系统,主要涉及到位采样时钟(BCK)、字同步时钟(WS)、采样数据输出(DATAO),系统时钟输入(SYSCLK)这几个对时序有要求的引脚。系统中,DATAO作为输出引脚,与DSP的BDR0引脚相连;BCK、WS、SYSCLK作为输入引脚,其时序由DSP供给。UDA1341TS的系统时钟只能是256Fs、384Fs、512Fs,通过对状态寄存器的SC0位和SC1位编程可实现系统时钟的选择设置。这里Fs是语音信号的采样频率。在采样数据时,WS用来指明UDA1341TS的DATAO输出的有效数据。当系统对VINL(左声道)端口进行采样时,WS的上升沿表明一帧数据的起始,下降沿表明一帧数据的结束;当系统对VINR(右声道)端口进行采样时,WS的下降沿表明一帧数据的起始,上升沿表明一帧数据的结束。

UDA1341TS提供了一个L3端口,利用CPLD控制器对L3的L3DATA、L3MODE和L3CLOCK三个引脚进行编程,可以设置其内部的寄存器。当L3MODE引脚为低电平时,通过L3DATA引脚输入寄存器地址信息;当L3DATA引脚为高电平时,通过L3DATA引脚输入有关寄存器设置的数据信息(如设置芯片系统时钟频率、数据输入格式、芯片工作模式等)。UDA1341TS与DSP的McBSP(多通道缓冲同步串口)相连,各种同步信号由DSP产生,这样就保证了新数据的正常接收以及已接收数据的正常处理。UDA1341TS与DSP的硬件连接如图2所示。

语音编码器TMS320VC5402

数字语音信号的压缩需要大量的数字信号处理,一般单片机是无法完成的,所以本系统选用TI公司的DSP芯片TMS320VC5402(以下简称C5402)对语音信号进行压缩处理。

C5402通过它的MsBSP与语音采样转换器UDA1341TS通信。McBSP提供了全双工的通信机制,以及双缓存的发送寄存器和三缓存的接收寄存器,允许连续的数据流传输,数据宽度的8、12、16、20、24、32位之间可选;McBSP与ADC的通信通过BDR0引脚实现,通信过程的控制则由BCLKR0、BCLKR1、BFSR0等三条引脚实现。

CPLD低速控制

DSP作为高速的运算处理器不合适低速的控制应用。对UDA1341TS检测、初始化,对LCD的控制以及对Flash的存储控制都是低速的控制。本系统选用CPLD来完成这些工作。CPLD为Altera公司的EPM7128S,开发仿真环境为Altera公司的MAX-PLUSII。因为DSP的地址线A0、A1、A2要被某些芯片使用,所以选取A3-A7、A15共6根地址线和I/O空间选择信号IS的反共同产生系统中各芯片的选通信号。CPLD中的控制电路负责产生各种读写信号,如Flash的读信号MEM_RD和写信号MEM_WR等。

在该系统中,C5402要产生许多控制信号(如Flash程序页的选择信号PPG2-PPGO等),同时也要监视和读取外部的状态。因为C5402只有两个通用I/O引脚,所以用CPLD来对其进行I/O端口扩展。CPLD内部通过一个8位DFF触发器实现对数据的输出。另外,通过8个三态门,将8位输入状态放到C5402数据总线的低8位上。C5402有4个中断输入INTR3反—INTR0的反。CPLD的中断选择模块可以从最多8个外部中断信号中选择4个作为C5402的中断输入,提高了系统的灵活性。

软件设计

软件设计主要包括ADC的程序设计,语音数据的压缩编码等。

ADC DSP CPLD LCD 电压 编码器 单片机 Altera 仿真 电路 总线 滤波器 相关文章:

- 节能的双线、4×4按键键盘接口 (10-06)

- 点阵液晶显示器在便携式频率特性测试仪中的应用(11-26)

- 随时可编程的增益控制(02-14)

- 基于NXP UOCIII芯片的LCD TV方案 (04-17)

- 基于PC的数字电视方案(08-10)

- 面向便携应用的智能电池管理考虑事项(02-14)