基于FPGA 的高阶全数字锁相环的设计与实现

时间:07-18

来源:互联网

点击:

4 锁相系统的设计实现与仿真

依据图1 锁相环系统的结构,利用Xilinx 公司的ISE 设计软件,采用自顶向下的模块化设计方法,用VHDL 对全数字锁相环的各个部件分别进行编程设计,然后对该系统做综合设计和仿真。最后,采用Xilinx 公司的sparnⅡ系列的FPGA 器件实现了锁相系统的硬件功能。

本锁相系统的设计参数如下:鉴相器中D 触发器的位长为16;DLF 内二个积分环节中累加器的位长均为16;DCO 中累加器的位长为24,累加器的时钟频率fclk 为8MHz,比例积分控制码组的字长G=14,自由振荡频率 f0 控制码组的字长C=10。

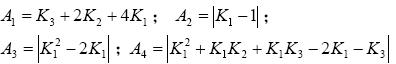

选择不同的比例系数Ka 和积分系数Kb 、Kc ,可以改变K1 、K2 、K3 的参数值,进而可根据本锁相系统的稳定条件式(5),判断系统是否稳定。表2 列出了几种典型参数所对应的锁相系统稳定性分析结果。

根据本系统在Z 域的传递函数和表2 中的设计参数K1 、K2 、K3 ,应用MATLAB 软件进行分析,得到三阶全数字锁相环在单位阶跃信号作用下的系统仿真曲线如图3 所示。

从图3 中系统仿真曲线可以看出,仿真实验与理论分析的结果是一致的。调节比例和积分系数不仅能够控制锁相系统的稳定性,还可以控制系统的锁相速度。显然,在保持系统稳定的条件下,图3(d)设计参数所对应的系统锁相速度较快。

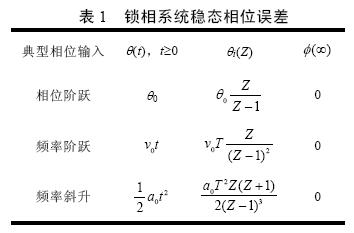

根据本系统在Z 域的误差传递函数和实际设计参数,可以分别得到系统在相位阶跃、频率阶跃和频率斜升信号作用下的响应曲线如图4 所示。从图4 中可以看到,系统对于上述信号的稳态跟踪误差均为零。这与理论分析所得出的结论也是一致的。综合考虑锁相系统的稳定性、稳态相差和锁相速度等性能指标, 最终选择设计参数K1 = 2-3 , K2 = 2-6, K3 = 2-11。

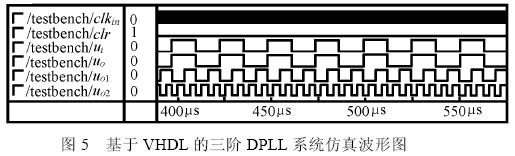

图5 给出了采用EDA 技术设计的三阶全数字锁相环的系统仿真波形,图中clkin 为系统时钟信号,clr 为系统复位信号, ui 为输入信号, uo 为输出信号, uo1 为二倍频输出信号, uo2 为四倍频输出信号。从图5 中可见,本锁相系统可以同时得到倍频输出信号。

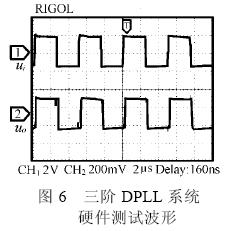

图6 给出了用FPGA 实现的三阶全数字锁相环的硬件电路测试波形。系统仿真与硬件测试结果都表明,该系统能够实现锁相功能。

4 结论

本文提出了一种基于PI 控制算法的三阶全数字锁相环,采用EDA 技术进行系统设计,并用可编程逻辑器件予以实现。该锁相环具有电路结构简单、控制灵活、跟踪精度高、环路性能好、易于集成的特点。在锁相速度和稳定性方面优于已有的采用脉冲序列低通滤波计数方法实现的数字锁相系统。理论分析和仿真实验表明,改变比例积分控制参数,可以很方便地调节锁相系统的锁相速度和稳定性,因而简化了设计过程。硬件测试结果证实,应用EDA 技术设计的高阶全数字锁相环能够实现其锁相功能。该锁相环可作为功能模块嵌入SoC 内,为各种控制系统提供快速、稳定和高精度的同步信号。

自动化 电子 滤波器 DSP 电路 集成电路 振荡器 仿真 EDA FPGA Xilinx VHDL SoC 相关文章:

- 科技改变iPhone 实现家庭自动化控制(06-16)

- 基于CPLD的空调控制系统(10-23)

- 面对小米难题针对智能家居的三种解法(08-03)

- 是时候重新考虑DisplayPort了吗(05-10)

- 飞思卡尔触摸传感器实现新的应用(08-17)

- RF技术取代红外遥控的梦想正在变为现实(08-05)