内嵌ARM核FPGA芯片EPXAl0及其在图像驱动应用

时间:07-10

来源:互联网

点击:

|

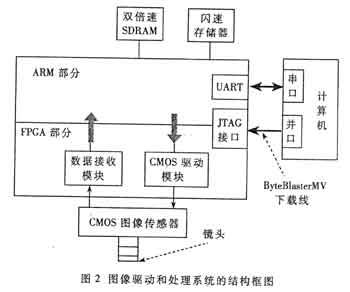

3.1图像的驱动

3.1.1 CMOS图像传感器的驱动

要使CMOS图像传感器成像,必须设计正确。的驱动时序,包括行同步、列同步、场同步及曝光时间设定等时序。利用FPGA逻辑编程简单的特点,用硬件描述语言Verilog HDL编程,可在FPGA中实现CMOS图像传感器的驱动时序,该驱动时序的仿真结果如图3所示。图中,ld_y为行选通信号;ld_x为列选通信号;cal为场选通信号;clk_adc为内部A/D转换器所需的时钟;addr为行列地址线;sys_reset为曝光时间设定信号;s和r为内部放大器选通信号。

|

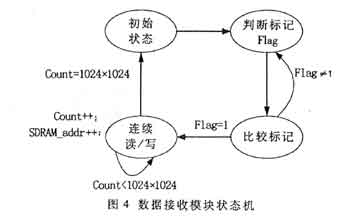

3.1.2图像的采集

CMOS图像传感器输出的信号为数字信号(即数字图像数据),所以图像的采集要通过FPGA中的数据接收模块将图像数据保存到片外SDRAM中。数据接收模块状态机如图4所示。标志Flag为1,开始采集数据。因为CMOS图像传感器在每个A/D转换时钟周期输出一个数据(如图3所示),接收模块也相应地设计成一个时钟接收周期接收一个数据(Burst状态),这样也就发挥了FPGA对大量数据处理速度快的优势。

|

3.1.3图像的显示

ARM将SDRAM中的图像数据经串口传给计算机,在计算机中用VC++语言编写串口协议和图像显示程序,将CMOS图像传感器采集到的图像显示在屏幕上,以便于监测验证。

3.2图像的处理

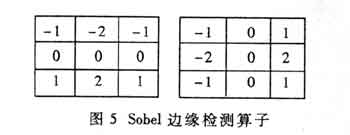

本系统采用的图像处理算法基于Sobel边缘检测算子。图像的边缘是由灰度不连续性所反映的,是图像的最基本信息。边缘检测算子检查每个像素的邻域并对灰度变化率进行量化,也包括方向的确定,大多数使用基于方向导数掩模求卷积的方法。就sobel算子而言,如图5所示,采用了两个3×3卷积核形成边缘算子模板,紧邻中心像素的像素有4个,和中心像素成斜对角的像素也有4个,距离中心像素近的模板值的系数为2,成斜对角的比较远,所以其系数为1,该系数反映了这样一点:邻域对当前像素的灰度梯度的影响程度越近影响越大,越远影响越小。图像中的每个点都用这两个核做卷积,一个核对垂直边缘响应最大,而另一个核对水平边缘响应最大,两个卷积的最大值作为该点的输出位,反映了当前位置灰度梯度(图像边缘)的主要方向和大小。运算结果反映了一幅边缘幅度图像。

|

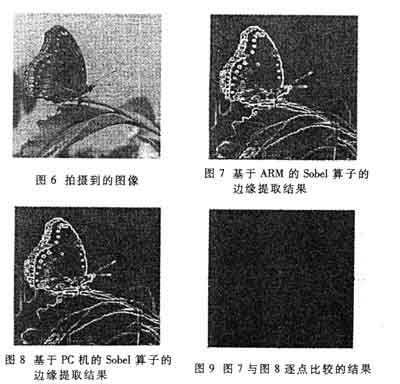

因为拍摄的图像为1024×1024,采用的Sobel算子为3x3模板,所以图像周边的一圈像素(第1行、第1024行、第1列、第1024列)保持原灰度值。在图像的第2行2列到1023行1023列的范围内,用图5所示的算子模板进行扫描计算,即当前像素和与当前像素相邻的8个像素,分别与模板中位置相应的9个系数相乘,累加这9个乘积结果,就得到针对某一方向的灰度梯度。比较两个方向的计算结果,取最大者作为当前位置的灰度梯度。图7为图6经过Sobel算子进行边缘提取后得到的图像。该算法在ARM中是基于C语言实现的,体现了ARM软件编程灵活的特点。

3.3试验结果

图6是成功驱动CMOS图像传感器后拍摄的景物图像,可见图像非常清晰。本文分别针对Soble算子进行了基于PC机和基于ARM的实现,图7为图6经过ARM中的Sobel算子的边缘提取结果,图8为图6经过PC机中Sobel算子的边缘提取结果,图9为图7和图8逐像素的比较结果。可见两种实现方法得到的结果完全一致,说明了基于ARM的Sobel算子的实现是正确的。

|

上述图像驱动和处理系统如果仅用FPGA来实现,算法部分的实现会比较复杂;如果仅用ARM来实现,驱动时序的设计也会非常困难。而采用内嵌ARM核的FPGA芯片EPXAl0,单片就实现了上述系统,大大减小了设计的难度和电路的复杂性,同时也减小了硬件电路的体积和功耗,在系统小型化方面有着独特的优势。由于EPXAl0集成了先进的ARM922T处理器器以及高密度的FPGA,所以在不增加体积和改进硬件电路的情况下,可以实现更加复杂的图像处理算法和硬件控制逻辑设计,具有很强的系统扩展潜力。这种嵌入式方案必将成为集成电路的发展趋势,将会在未来较短的时间里得到快速的发展。

FPGA 电路 EDA Altera 嵌入式 ARM C语言 USB Quartus 总线 CMOS 传感器 Verilog 仿真 放大器 集成电路 相关文章:

- 利用FPGA和新技术,使LCD进入HDTV市场(08-27)

- 基于DSP和FPGA的电视观瞄系统设计(09-02)

- FPGA与SRAM相结合完成大容量数据存储(09-03)

- HDTV接收机中Viterbi译码器的FPGA实现(09-09)

- 基于FPGA的液晶显示接口设计 (09-26)

- 解决硬盘驱动器能耗难题(10-13)