何降低蓝牙装置的功耗

时间:03-12

来源:互联网

点击:

功耗是决定可携式装置发展成败的关键因素。由于这类装置的趋势朝向功能汇整的方向演进,最明显的迹象就是百万像素数字相机整合至照相手机中,新型的多功能装置必须持续迎合消费者的需求,尤其是在功耗方面。

虽然蓝牙本身就已是低功耗技术,但为了进一步延长电池续航力,蓝牙技术联盟(Bluetooth SIG)仍持续整合许多新方法,以降低新版本蓝牙规格的功耗。在2004年11月,Bluetooth SIG修订了 2.0+ Enhanced Data Rate (EDR)规格,结合一种革命性的技术,创造出更有效率的无线连结一与资料封包传送机制。

蓝牙规格

Bluetooth SIG降低蓝牙装置功耗最重要的方法,就是发展出EDR Bluetooth。蓝牙无线电元件消耗的电力,取决于运作时间的长短。v2.0+EDR 蓝牙规格让资料传输速度达到传统蓝牙的3倍(3Mbps 比 1Mbps),这代表无线电波的运作时间减少到三分之一,因此消耗的电量也减少至三分之一。提高的资料传输率归功于彻底改变资料封包的传输方式。

标准传输率(1Mbps – 例如像 v1.2 以前的蓝牙版本 ) 封包中含有四个部分 :

1. 存取码 (Access Code) – 接收装置利用这个存取码来辨识输入端的传输作业

2. 封包表头 (Header) – 描述封包的种类与长度

3. 封包内容 (Payload) – 实际传送的资料内容

4. 跨封包的 Guard Band (Inter-packet Guard Band)–将无线电波转至下个频带

所有三个传送部份都采用高斯频率偏移调变机制 (Gaussian Frequency Shift Keying, GFSK)来处理射频讯号: 载波频率偏移范围为正负160 kHz,来代表零或一,每个符元(symbol)编码出一个位元。符元传输率为 1 Msps (Mega Symbol Per Second)。存取码、表头、以及Guard Band保护频带等三个部份所需的资源,让最高负载资料率达到723 kbps。

Bluetooth EDR 封包仍对存取码与表头采用GFSK调变机制,但对Payload资料则使用以下二种其中之一不同的调变机制: 一种是强制性,提供2倍的资料传输率,能容许较高的噪音; 另一种是选择性调变机制,提供3倍的资料传输率。

2倍资料传输率采用 π/4 Differential Quadrature Phase Shift 键移或 π/4-DQPSK技术。这种调变机制会改变载波的相位而不是频率。“Quadrature” 代表每个符元有四个可能的相位,让每个符元中有两个资料位元能进行编码。符元率维持不变; 因此资料传输率提高两倍。

3倍资料传输率采用的是 8-DPSK (8-Phase Differential Phase Shift Keying),这种机制类似π/4-DQPSK,但能移至任何8个可能的相位。邻近位置之间缩小的相位差,加上使用 ±π 相位跳变,意谓着8-DPSK较容易受到干扰,但每个符元能编码3个位元的资料。

在EDR规格的成功迈入实际产品阶段后,通过检验的产品于2005年问市,SIG仍继续研究各种新方法来降低耗电量。

CSR BlueCore以低功耗模式及内部时脉进一步降低耗电量

CSR的BlueCore芯片内建的硬件时脉,能将数字元件与无线电加以区隔;关闭无线电;以及将芯片切换至浅层或深层睡眠模式。藉此提供甚至可超越 Bluetooth SIG官方标准的低耗电效能。

低功耗模式以及内部时脉

BlueCore芯片内的硬件时脉能将数位元件与无线电加以区隔; 关闭无线电; 以及将芯片切换至浅层或深层睡眠模式。

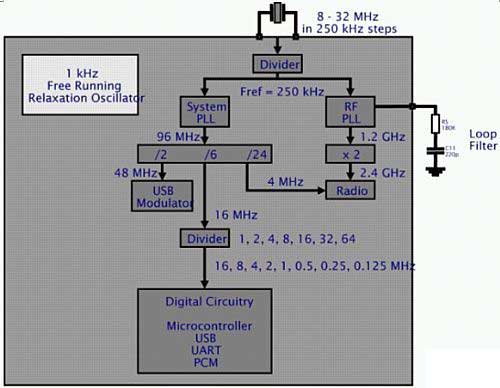

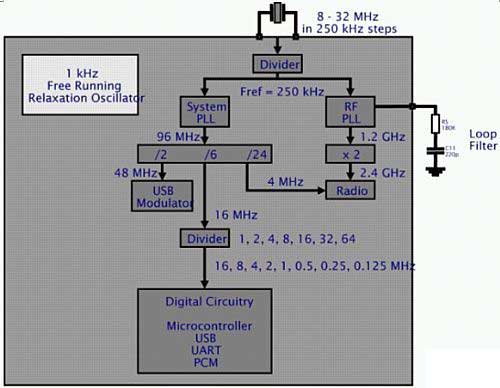

图 1 浅层睡眠模式的耗电量

在浅层睡眠模式时中,时脉速度从16MHz降低至0.125MHz ,电流从 10mA降低至 2mA (如图1所示)

图 2 深层睡眠模式的时脉结构

在深层睡眠模式中,主要的晶体加上所有其他时脉元件都被关闭,只留下1kHz给振荡器 (Oscillator) 使用(如图2所示)

在切换至深层睡眠模式时,BlueCore需要 20milliseconds (ms)的无作业空闲时间。在唤醒方面,芯体需要 5ms的时间来重新启动,元件需要约20ms的无作业时间(预测)。BlueCore能透过排程警报,在下一次排定的作业之前唤醒元件,或是由PIO、 UART、或USB连结埠传送器的中断,藉以离开深层睡眠模式。

芯片架构

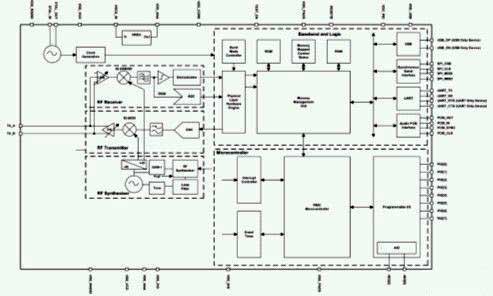

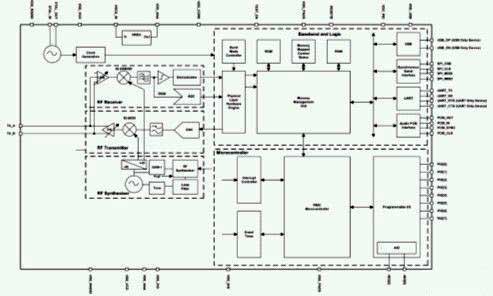

图3 BlueCore3-ROM CSP 芯片封装

BlueCore 芯片架构本身扮演一个重要角色,确保功耗的效率以及降低耗电量。图3列出一个BlueCore3-ROM CSP芯片级封装设计,显示BlueCore芯片的典型配置。

CSR从0.18微米转移至0.13微米制程,发展CSR的第五代BlueCore5元件,对耗电量方面产生显着的影响。随着硅元件尺寸越来越小,芯片中不同元件之间的通信变得更有效率,相同的功能如今仅须小量的电力就能完成。

虽然蓝牙本身就已是低功耗技术,但为了进一步延长电池续航力,蓝牙技术联盟(Bluetooth SIG)仍持续整合许多新方法,以降低新版本蓝牙规格的功耗。在2004年11月,Bluetooth SIG修订了 2.0+ Enhanced Data Rate (EDR)规格,结合一种革命性的技术,创造出更有效率的无线连结一与资料封包传送机制。

蓝牙规格

Bluetooth SIG降低蓝牙装置功耗最重要的方法,就是发展出EDR Bluetooth。蓝牙无线电元件消耗的电力,取决于运作时间的长短。v2.0+EDR 蓝牙规格让资料传输速度达到传统蓝牙的3倍(3Mbps 比 1Mbps),这代表无线电波的运作时间减少到三分之一,因此消耗的电量也减少至三分之一。提高的资料传输率归功于彻底改变资料封包的传输方式。

标准传输率(1Mbps – 例如像 v1.2 以前的蓝牙版本 ) 封包中含有四个部分 :

1. 存取码 (Access Code) – 接收装置利用这个存取码来辨识输入端的传输作业

2. 封包表头 (Header) – 描述封包的种类与长度

3. 封包内容 (Payload) – 实际传送的资料内容

4. 跨封包的 Guard Band (Inter-packet Guard Band)–将无线电波转至下个频带

所有三个传送部份都采用高斯频率偏移调变机制 (Gaussian Frequency Shift Keying, GFSK)来处理射频讯号: 载波频率偏移范围为正负160 kHz,来代表零或一,每个符元(symbol)编码出一个位元。符元传输率为 1 Msps (Mega Symbol Per Second)。存取码、表头、以及Guard Band保护频带等三个部份所需的资源,让最高负载资料率达到723 kbps。

Bluetooth EDR 封包仍对存取码与表头采用GFSK调变机制,但对Payload资料则使用以下二种其中之一不同的调变机制: 一种是强制性,提供2倍的资料传输率,能容许较高的噪音; 另一种是选择性调变机制,提供3倍的资料传输率。

2倍资料传输率采用 π/4 Differential Quadrature Phase Shift 键移或 π/4-DQPSK技术。这种调变机制会改变载波的相位而不是频率。“Quadrature” 代表每个符元有四个可能的相位,让每个符元中有两个资料位元能进行编码。符元率维持不变; 因此资料传输率提高两倍。

3倍资料传输率采用的是 8-DPSK (8-Phase Differential Phase Shift Keying),这种机制类似π/4-DQPSK,但能移至任何8个可能的相位。邻近位置之间缩小的相位差,加上使用 ±π 相位跳变,意谓着8-DPSK较容易受到干扰,但每个符元能编码3个位元的资料。

在EDR规格的成功迈入实际产品阶段后,通过检验的产品于2005年问市,SIG仍继续研究各种新方法来降低耗电量。

CSR BlueCore以低功耗模式及内部时脉进一步降低耗电量

CSR的BlueCore芯片内建的硬件时脉,能将数字元件与无线电加以区隔;关闭无线电;以及将芯片切换至浅层或深层睡眠模式。藉此提供甚至可超越 Bluetooth SIG官方标准的低耗电效能。

低功耗模式以及内部时脉

BlueCore芯片内的硬件时脉能将数位元件与无线电加以区隔; 关闭无线电; 以及将芯片切换至浅层或深层睡眠模式。

图 1 浅层睡眠模式的耗电量

在浅层睡眠模式时中,时脉速度从16MHz降低至0.125MHz ,电流从 10mA降低至 2mA (如图1所示)

图 2 深层睡眠模式的时脉结构

在深层睡眠模式中,主要的晶体加上所有其他时脉元件都被关闭,只留下1kHz给振荡器 (Oscillator) 使用(如图2所示)

在切换至深层睡眠模式时,BlueCore需要 20milliseconds (ms)的无作业空闲时间。在唤醒方面,芯体需要 5ms的时间来重新启动,元件需要约20ms的无作业时间(预测)。BlueCore能透过排程警报,在下一次排定的作业之前唤醒元件,或是由PIO、 UART、或USB连结埠传送器的中断,藉以离开深层睡眠模式。

芯片架构

图3 BlueCore3-ROM CSP 芯片封装

BlueCore 芯片架构本身扮演一个重要角色,确保功耗的效率以及降低耗电量。图3列出一个BlueCore3-ROM CSP芯片级封装设计,显示BlueCore芯片的典型配置。

CSR从0.18微米转移至0.13微米制程,发展CSR的第五代BlueCore5元件,对耗电量方面产生显着的影响。随着硅元件尺寸越来越小,芯片中不同元件之间的通信变得更有效率,相同的功能如今仅须小量的电力就能完成。

蓝牙 无线电 射频 CSR 电流 振荡器 USB DSP ARM 解码器 电子 相关文章:

- 迎接移动多媒体高清视频挑战(10-07)

- 为 PDA 应用设计用户界面 (10-07)

- 天线设计面临小尺寸和多天线要求的挑战(11-06)

- 高集成度蓝牙耳机电源管理方案 (01-12)

- 设计剖析:面向音乐手机的蓝牙耳机套件(02-05)

- 如何在单个蓝牙设备上集成语音和立体声音乐功能(02-09)