高速自动测试设备的未来

时间:08-30

来源:互联网

点击:

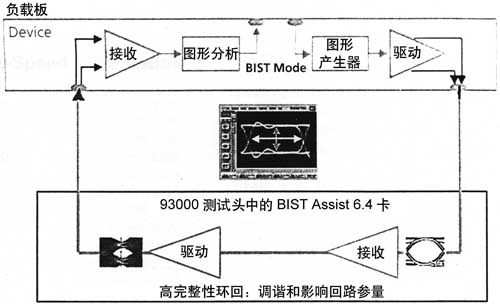

图2 BIST环回测试方法与专用ATE环回卡结合

尽管DFT或其他低成本技术对于高速器件的很多高频I/O特性是最经济的测试方案,但仍然对ATE有较强的要求,希望它能提供全速度激励和捕获,特别是在产品定型前更是这样。

当DFT完全取代全速度功能测试时,可达到的故障覆盖率趋于折衷。这可能是一种潜在的风险,特别是对于把工艺技术推至极限的新I/O技术而言。另外,DFT仍然是一种成熟的技术,而不同的硅供应商遵循不同的DFT开发战略。基于此原因,全速度DFT不是一贯的跨业界实现。甚至在生产中,在可预测的将来,整个业界将不希望用全速度DFT完全替代全速度功能测试。

高速ATE通道的关键要求

对于设计特征,ATE高速驱动和捕获能力必须配合高定时的精度。同等重要的是,必须提供的ATE功能是经济的,因为半导体厂家面对巨大的成本压力。

高速ATE要求如下:

·高度灵活性:其能力包括各种不同的I/O类型。

·完全可量测性:其能力包括所需速度的整个范围和所需的引脚资源。数据率范围从几百兆赫到几千兆赫,所需引脚数高达2000引脚。

·高性能:高精度和快速吞吐量。

·多时钟域支持。

·负担得起的成本。

结语

不管现在的进展如何,全速度结构和BIST基环回测试不大可能解决与纳米制造缺陷相关定时的所有问题。随着大多数产品寿命周期变得越来越短,而检验和最佳化DFT电路达到必须的水平变得更加困难。很多情况下,DFT基技术将与有限数的功能全速度图形共存,这可填充仅DFT技术的漏失测试范围。因此,可提供高速、高密度和高度通用的ATE将仍然是获得成功半导体制造的关键。

半导体 CMOS 电压 电流 电容 仿真 总线 嵌入式 EDA 电路 相关文章:

- 半导体C-V测量基础(06-28)

- 基于PSoC的防高压电容测量设计与实现(03-27)

- 新材料对测量技术的挑战(05-24)

- 通过LabVIEW图形化开发平台有效优化多核处理器环境下的信号处理性能(06-21)

- 视频压缩系统中大容量存储器的应用设计 (10-12)

- 半导体功能测试基础术语(10-25)