基于AD9850的信号发生器的设计与实现

时间:03-24

来源:互联网

点击:

直接数字频率合成技术(DDS)是20世纪末迅速发展起来的一种新的频率合成技术,它将先进的数字处理技术与方法引入信号合成领域,表现出优越的性能和突出的特点。由于DDS器件采用高速数字电路和高速D/A转换技术,具有频率转换速度快、频率分辨率高、相位噪声低、频率稳定度高等优点,此外,DDS器件很容易实现对信号的全数字式调制。因此,直接数字频率合成器以其独有的优势成为当今电子设备和系统频率源的首选器件。本文介绍了ADI公司出品的 AD9850芯片,以单片机AT89S52为控制核心完成正弦信号发生器的可行性设计方案,并给出了调试通过的源程序以供参考。

1 AD9850芯片性能及管脚功能

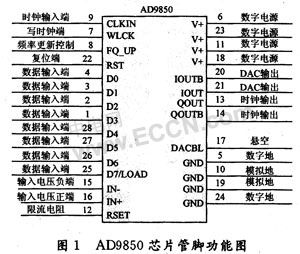

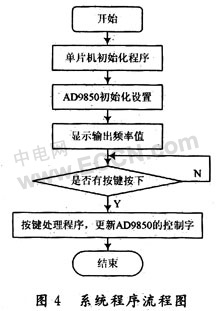

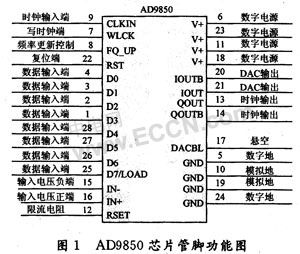

AD9850采用了先进的CMOS工艺,支持5 V和3.3 V两种供电电压,在3.3 V供电时功耗仅为155 mW,扩展工业级温度为-40~+80℃。支持并行或串行输入控制接口形式,最大支持时钟频率为125MHz,此时输出的频率分辨率达0.029 1 Hz。采用28脚SSOP表面封装形式,其管脚功能如图1所示。

AD9850分为可编程序DDS系统、高性能数/模变换器(DAC)和高速比较器三部分,其中可编程DDS系统包含输入寄存器、数据寄存器和高速DDS三部分。高速DDS包括相位累加器和正弦查找表,其中相位累加器由一个加法器和一个 32位相位寄存器组成,相位寄存器的输出与一个5位的外部相位控制字相加后作为正弦查找表的地址。正弦查找表包含一个正弦波周期的数字幅度信息,每一个地址对应正弦波中0~360范围的一个相位点。查找表输出后驱动10 b的DAC转换器,输出两个互补的电流,其幅度可通过外接电阻Rset来调节,输出电流可由Iset=32(1.248 V/Rset)来计算,Rset的典型值为3.9 kΩ。输出信号经过外部的一个低通滤波器后接到AD9850内部自带的高速比较器,即可产生一个与正弦波同频率且抖动很小的方波。

2 AD9850的控制字及控制时序

AD9850的控制字有40位,其中32位是频率控制位,5位是相位控制位,1位是电源休眠控制位,2位是工作方式选择控制位。在应用中,工作方式选择位设为00,因为01,10,11已经预留作为工厂测试用。相位控制位按增量 180°,90°,45°,22.5°,11.25°或这些组合来调整。频率控制位可通过下式计算得到:

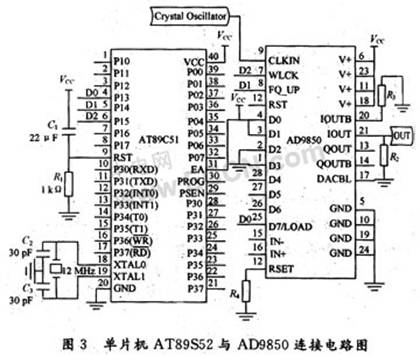

其中:fout要输出的频率值;fr为参考时钟频率;W为相应的十进制频率控制字,然后转换为十六进制即可。

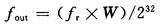

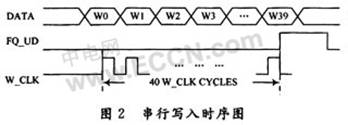

AD9850有串行和并行两种控制命令字写入方式。其中串行写入方式是采用D7作为数据输入端,每次W_CLK 的上升沿把一个数据串行移人到输入寄存器,40位数据都移入后,FQ_UD上升沿完成输出信号频率和相位的更新。串行控制字的写入时序如图2所示。但是要注意的是,此时数据输入端的三个管脚不可悬空,其中D0,D1脚接高电平,D2脚要接地。

3 硬件电路设计

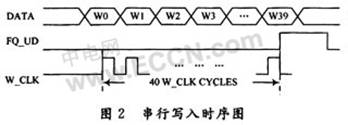

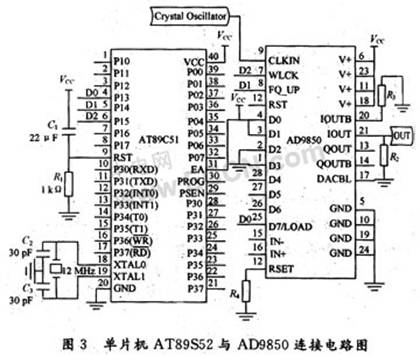

AD9850控制字的写入方式有串行和并行两种。并行写入方式的优点是数据传输的速度快,能够提升整个系统的处理速度,但占用的单片机的I/O口资源太多。与并行方式相比,串行写入方式在数据传输的速度上要慢些,但它更大优点是能节省很多I/O口资源。所以,本系统采用AT89S52单片机作为控制核心,通过串行写入控制字的方式控制AD9850芯片,加上键盘和LED显示部分等外围电路,构成整个系统电路。为了详细介绍AD9850的用法,这里重点给出本系统中AT89S52单片机与AD9850芯片连接电路,如图3所示,其中R1=3.9 kΩ,R2=50 Ω,R3=25 Ω,单片机晶振选用12 MHz,电容采用20 pF经典值。单片机采用12 MHz晶振时,它的高电平时间能够满足AD9850复位要求,故可将AD9850的复位端与单片机的复位端直接相连。

4 软件部分设计

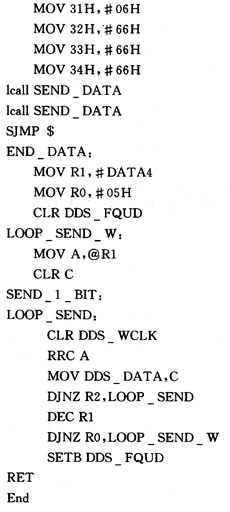

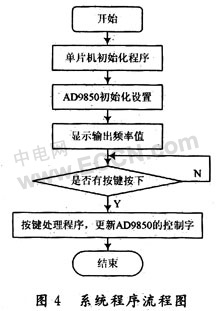

软件程序的功能就是通过程序使整个系统按照人们的设想要求工作起来,本系统中最主要的部分就是将AD9850的40位控制字通过单片机写入到AD9850芯片内,系统的程序流程图如图4所示。要根据写入控制字方式的不同严格按照AD9850的耐序图来编写控制字写入子程序。本文主要给出串行写入方式的汇编源程序以供读者调试参考。

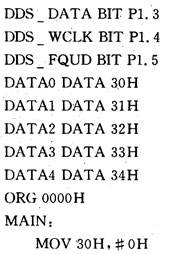

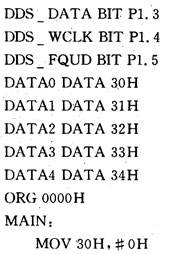

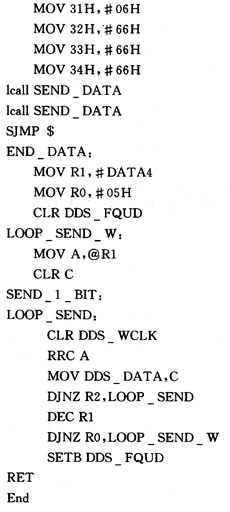

AD9850数据传送子程序如下:

5 结语

本文在介绍经典DDS芯片AD9850的基础上,采用 AT89S52单片机设计了一个串行控制方式的正弦信号发生器可行性方案,并给出了部分重要电路图和调试源程序。最后笔者通过实际电路的测试表明,该电路设计方案正确可行,频率容易控制,操作简单灵活,且具有广阔的应用前景。

作者:石桂名,冀勇钢,彭海龙

来源:《现代电子技术》2010年第33卷第01期

1 AD9850芯片性能及管脚功能

AD9850采用了先进的CMOS工艺,支持5 V和3.3 V两种供电电压,在3.3 V供电时功耗仅为155 mW,扩展工业级温度为-40~+80℃。支持并行或串行输入控制接口形式,最大支持时钟频率为125MHz,此时输出的频率分辨率达0.029 1 Hz。采用28脚SSOP表面封装形式,其管脚功能如图1所示。

AD9850分为可编程序DDS系统、高性能数/模变换器(DAC)和高速比较器三部分,其中可编程DDS系统包含输入寄存器、数据寄存器和高速DDS三部分。高速DDS包括相位累加器和正弦查找表,其中相位累加器由一个加法器和一个 32位相位寄存器组成,相位寄存器的输出与一个5位的外部相位控制字相加后作为正弦查找表的地址。正弦查找表包含一个正弦波周期的数字幅度信息,每一个地址对应正弦波中0~360范围的一个相位点。查找表输出后驱动10 b的DAC转换器,输出两个互补的电流,其幅度可通过外接电阻Rset来调节,输出电流可由Iset=32(1.248 V/Rset)来计算,Rset的典型值为3.9 kΩ。输出信号经过外部的一个低通滤波器后接到AD9850内部自带的高速比较器,即可产生一个与正弦波同频率且抖动很小的方波。

2 AD9850的控制字及控制时序

AD9850的控制字有40位,其中32位是频率控制位,5位是相位控制位,1位是电源休眠控制位,2位是工作方式选择控制位。在应用中,工作方式选择位设为00,因为01,10,11已经预留作为工厂测试用。相位控制位按增量 180°,90°,45°,22.5°,11.25°或这些组合来调整。频率控制位可通过下式计算得到:

其中:fout要输出的频率值;fr为参考时钟频率;W为相应的十进制频率控制字,然后转换为十六进制即可。

AD9850有串行和并行两种控制命令字写入方式。其中串行写入方式是采用D7作为数据输入端,每次W_CLK 的上升沿把一个数据串行移人到输入寄存器,40位数据都移入后,FQ_UD上升沿完成输出信号频率和相位的更新。串行控制字的写入时序如图2所示。但是要注意的是,此时数据输入端的三个管脚不可悬空,其中D0,D1脚接高电平,D2脚要接地。

3 硬件电路设计

AD9850控制字的写入方式有串行和并行两种。并行写入方式的优点是数据传输的速度快,能够提升整个系统的处理速度,但占用的单片机的I/O口资源太多。与并行方式相比,串行写入方式在数据传输的速度上要慢些,但它更大优点是能节省很多I/O口资源。所以,本系统采用AT89S52单片机作为控制核心,通过串行写入控制字的方式控制AD9850芯片,加上键盘和LED显示部分等外围电路,构成整个系统电路。为了详细介绍AD9850的用法,这里重点给出本系统中AT89S52单片机与AD9850芯片连接电路,如图3所示,其中R1=3.9 kΩ,R2=50 Ω,R3=25 Ω,单片机晶振选用12 MHz,电容采用20 pF经典值。单片机采用12 MHz晶振时,它的高电平时间能够满足AD9850复位要求,故可将AD9850的复位端与单片机的复位端直接相连。

4 软件部分设计

软件程序的功能就是通过程序使整个系统按照人们的设想要求工作起来,本系统中最主要的部分就是将AD9850的40位控制字通过单片机写入到AD9850芯片内,系统的程序流程图如图4所示。要根据写入控制字方式的不同严格按照AD9850的耐序图来编写控制字写入子程序。本文主要给出串行写入方式的汇编源程序以供读者调试参考。

AD9850数据传送子程序如下:

5 结语

本文在介绍经典DDS芯片AD9850的基础上,采用 AT89S52单片机设计了一个串行控制方式的正弦信号发生器可行性方案,并给出了部分重要电路图和调试源程序。最后笔者通过实际电路的测试表明,该电路设计方案正确可行,频率容易控制,操作简单灵活,且具有广阔的应用前景。

作者:石桂名,冀勇钢,彭海龙

来源:《现代电子技术》2010年第33卷第01期

电路 电子 ADI 单片机 信号发生器 CMOS 电压 DAC 比较器 电流 电阻 滤波器 LED 电容 电路图 相关文章:

- 集成电路的电磁兼容测试(06-06)

- 低功耗制造测试的设计-第一部分(01-29)

- 低功耗制造性测试的设计-第二部分(01-29)

- ASA测试技术在电路维修测试仪上的应用(06-28)

- 示波器前级衰减电路(06-21)

- 电调谐LC滤波器的研究与设计(11-09)