通过长距离I2C总线实现模拟信号的数字传输

时间:01-08

来源:互联网

点击:

内部集成电路总线(I2C)是一种同步串行数据通信总线,其中由主器件发起通信,从器件通过寻址机制加以控制。I2C总线上的节点很容易连接,因为只需连接两条开漏形式的信号线(SDA用于数据,SCL用于时钟)。这些线上的电容是限制传输速率和节点间距离的主要因素[1]。要想扩展速率和距离,有必要使用能够识别数据方向的缓冲器。本文所述的设计案例充分展示了PCA9605缓冲器的优势。

PCA9605是一种单片CMOS集成电路,可在包括I2C总线的应用中实现总线缓冲功能。该缓冲器可以通过缓冲驱动SCL和SDA线来扩展总线负载,缓冲器两侧可达到最大允许的总线电容。在其最基本的实现中,该缓冲器允许扩展数量的从器件连接到一个主器件。在本例设计中,主器件是PIC的微控制器[2],从器件是两个数据转换器,其中一个是模数转换器,另一个是数模转换器。PCA9605的方向引脚(DIR)固定接地,因为时钟由主器件提供(单向时钟模式)。图1给出了总的原理图。

U2 ADC捕获来自信号发生器的模拟信号并转换成数字信号,然后发送给缓冲器U3,由U3驱动后上电缆传输,并经U4中继后继续传输。SDA数据线需要双向驱动,从U3到U4以及U4到U3。最终由U5 ADC产生数字化后的信号。如果需要经过更长距离的电缆传输,可以在电路中间插入另一个缓冲器进行扩展。这种方法可以覆盖长达数百米的有线传输距离[3]。

图1:用扩展I2C总线连接两个节点的电路原理图。

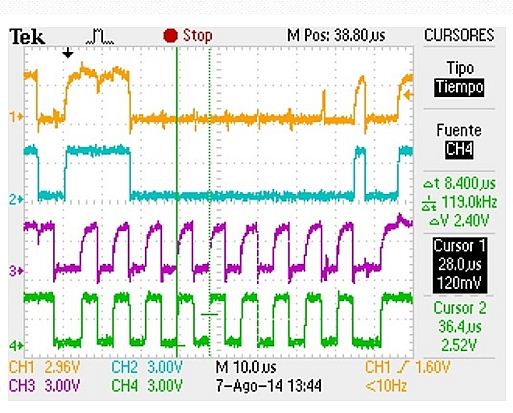

图2显示了通过电缆总线以125kHz速率传输DAC地址(0xC0)。通道1连接的是总线侧SDA线(U4的引脚6),该信号通过缓冲器驱动后可消除毛刺和来自时钟线的容性干扰以及由于使用上拉电阻的开路集成极和走线电容引起的RC效应。通道2显示的是经过缓冲器驱动后的SDA数据信号(U4的引脚7),通道4(U4的引脚2)是经过驱动后的时钟SCL。电缆上的时钟信号(U4的引脚3)示于通道3,通道4是经过缓冲器驱动后的信号(U4的引脚2)。

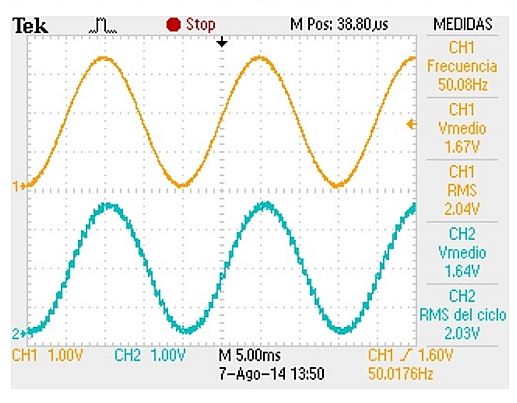

如果系统测试时给ADC U2发送一个电压幅度为满输入刻度的单极性模拟信号,在DAC U5的输出负载上就可以得到图3所示的波形。本设计充分利用了ADC和DAC电路的特性,允许它们处理轨到轨信号。这种低频信号可以通过在DAC输出端增加一个低通滤波器加以改进,因为低通滤波器可以降低采样和重构噪声。

图2:缓冲器前后的从节点信号。

图3:通过I2C发送的满刻度输入正弦信号。

参考文献:

[1] Chris Parris and Jonathan Dillon, Microchip Technology Inc.. Design calculations for robust I2C communications. EDN Network. April, 2012.

[2] Application note AN11084.NXP Semiconductors. Very large I2C-bus systems and long buses. October 2011.

[3] Code of the PIC microcontroller. [On line]

集成电路 总线 电容 CMOS 电路 PIC ADC 信号发生器 DAC 电阻 电压 滤波器 低通滤波器 Microchip NXP 相关文章:

- 基于新型ASSP LTC3455的硬盘MP3电源设计(06-07)

- 单片彩色LCoS显示系统的设计实现(09-09)

- 具有开关电源通路管理的下一代电源管理集成电路(08-28)

- 如何利用DCP获得更精确的性能(10-01)

- 集成电路的种类与用途(09-20)

- CMOS集成电路中ESD保护技术研究(10-17)