3G手机的DigRF测试解决方案

ATE策略的比较

传统生产测试系统有静态的选通时序以及简单的比较功能(例如H、L、X、M、V、存储),因此它们自身并不具备强大的校准能力,以应对DigRF器件需要的非确定性。不过,这类测试仪中的数字仪器有所需要的数字捕捉能力,一般用于ADC(模数转换器)输出数据或DUT寄存器读取操作。因此,你可以保留在这台仪器上的投资,并且采用一种批量捕捉和后处理技术(block-capture-and-post-processing)应对DigRF的RF接收测试挑战。

对于RF接收测试,一般CW(连续波)测试需要1kB至4kB的I/Q采样,而日益普遍的采用调制波形的系统级测试则使用16 kB至32 kB的I/Q采样。注意转换为实际的串行位:

1k I/Q = 1024 ? [8 bits (I) + 8 bits (Q)] ? 协议_开销 = 串行位数

为了解决实时情况下的非确定性行为,测试仪必须提供专为DigRF 3G DUT与数字捕捉之间编码的数字逻辑。其目标是在数据到达测试仪的DSP(数字信号处理器)前,减轻捕捉时所出现的所有时序与数据不确定性问题。

一种测试选择是在DIB(器件接口板)上设计一个FPGA(现场可编程门阵列)电路。这种方法可以用一片廉价器件提供定制逻辑,但也有三个麻烦:

·接口以及为电路提供支持信号将会非常复杂;

·在隔离与屏蔽能力有限情况下,在与这些敏感RF信号如此近的地方增加一个数字噪声发生器,存在着更多的风险;

·为每个器件负载板增加元件会使成本上升,延长测试开发时间。

作为另一种选择,可以采用一台提供嵌入实时功能的数字测试仪器,它可以在降低成本的同时简化DIB复杂性。这种方案的缺点是缺乏测试工程师所需要的灵活性,因为他们要测试一组通信协议。只针对DigRF的解决方案是不实用的。

采用这种选择时,当测试程序知道有RF接收数据时,就能在RxData总线上捕捉到大块数据;这个块必须放大到能可靠地捕捉足够的数据包,从而有足够数量的I/Q采样用于后处理算法。数据从数字仪器的捕捉内存送至DSP引擎,在那里由一个预处理算法执行一个三步处理:

·找到每个包的起始索引;

·分析每个包的头;

·顺序地对有效载荷中的I/Q采样进行去交错操作,并保存在新的独立数组中。

一旦数据完成预处理,就可以对所需的I/Q数据集执行用户定制的处理算法,或将数据集输出到其它ATE软件工具,测试EVM(误差矢量幅度)等特性。

这一方法的成功与否取决定于数据移动时间,以及所需处理步骤的效率。尽量减少总测试时间的关键是避免与主控PC的不必要交互,因为这种交互要求测试程序暂停DUT测试的执行。如果测试仪具有边做模式捕捉边移动数据的能力,则向DSP传输数据的整个时间都被隐蔽在后台,测试时间是零损失。

如果测试仪没有此项功能,则测试工程师就必须寻找能减少移动数据量的方法。一个选择是只捕捉失效数据,但这会在DSP中增加一个重构原始数据的新处理步骤;单单这个不必要的步骤就会增加数毫秒的关键测试时间。

一个完整的DigRF解决方案需要完全在后台执行预处理算法和I/Q处理。因此,第三种选择就需要测试仪架构能支持执行数字信号处理算法的专用处理器,一旦DUT信号捕捉完成,测试程序就能立即开始下一个测试的设置。另外,多址测试也需要这种后台处理的并行式高效率。

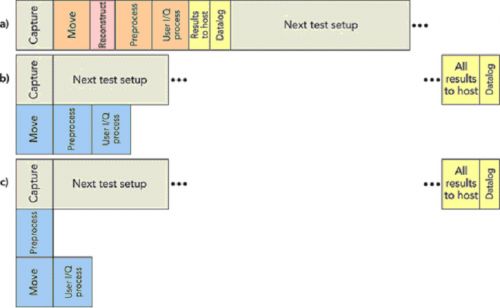

图4表示这三种选择对测试时间的可能影响。对第一种选择,缺乏后台处理而产生了一个串行的测试流,有最长的测试时间。第三种情况下,采用了实时处理,似乎最为理想,因为它用全后台处理,以最高效的方式解决了测试挑战。

图 4. 这里显示的三种测试选择的测试时间开销:(a) 串行执行流,(b) 批量捕捉与后处理方案,(c) 实时处理。

不过,批量捕捉和后处理方案也可以有低的测试时间开销,只要数据转移是在后台完成,并且高效地处理,没有被浪费的步骤,并有独立的多址并行处理器。有了适当的系统能力,八址程序的预处理器时间可以低至数毫秒,足以隐藏在一个典型RF测试时间中。

- 新型HELP技术与开关调节器在3G手机中的应用(01-09)

- 3G手机语音识别应用中DSP的选择策略(02-19)

- 展讯3G手机电视芯片组设计(09-11)

- 3G手机电视芯片组应用方案(01-27)

- 3G手机射频集成障碍(02-28)

- 3G手机的RF屏蔽设计(04-18)