运放稳定性连载9:单电源缓冲器电路的实际设计(2)

时间:07-31

来源:互联网

点击:

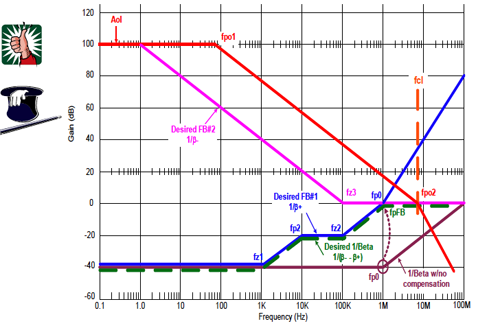

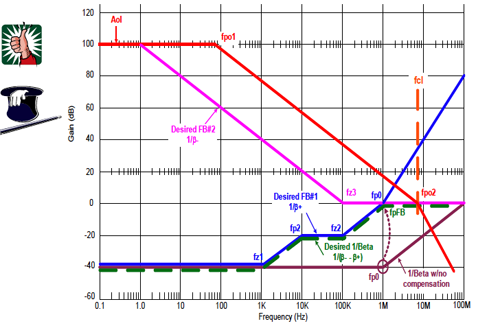

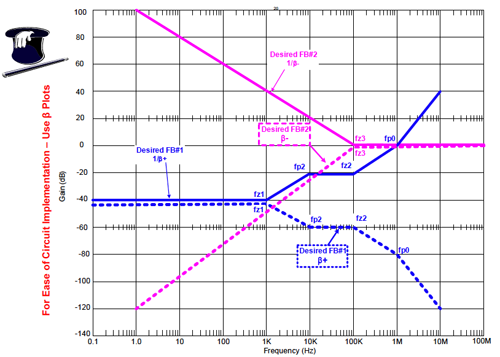

在图5.16中,我们分析了缓冲器电路拓扑w/o补偿原理,并给出了采用两条反馈路径的解决方案。我们的Aol曲线是取自厂商的数据资料(见图5.15)。标为“缓冲器拓扑w/o 补偿”的曲线是我们的直流Beta 分析结果,我们用Tina SPICE 仿真来找出高频极点。现在我们利用十倍频程经验法则来调整FB#1,这是我们缓冲电路中已有的反馈路径。我们注意到,在fcl 处,我们想得到20dB/decade 的闭合速度。

从 -40dB 到0dB 的距离较大,因此我们每次用掉数量上的一个十倍频程,这使我们得到如图5.16 所示的阶跃式上升,频率上也是如此。一旦我们在FB#1 曲线上达到1MHz,由于晶体管电容的寄生效应,我们需要加入高频极点(从1/Beta w/no 补偿曲线)。我们对FB#1 进行了所有能做的工作,但我们注意到它与Aol 曲线 以40dB/decade 的闭合速度相交。现在我们将增加第二条反馈路径FB#2。如果我们能将它加入我们的缓冲电路中(如图所示),则我们可以看到它将在频率大于1MHz 时占优势,且1/β 曲线和Aol 曲线将以20dB/decade 的闭合速度相交!!

图5.16:1 阶分析:Aol 与1/β 曲线

图字:所期望的FB#2 1/β-、所期望的FB#1 1/β+、所期望的1/Beta 1/(β--β+)、1/Beta w/no 补偿

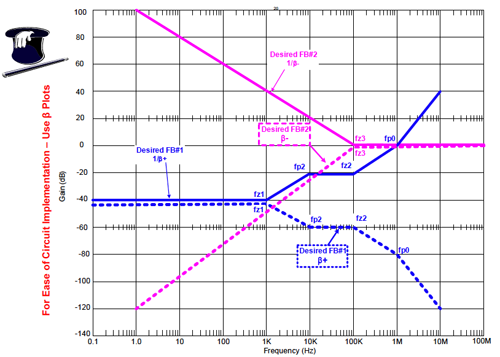

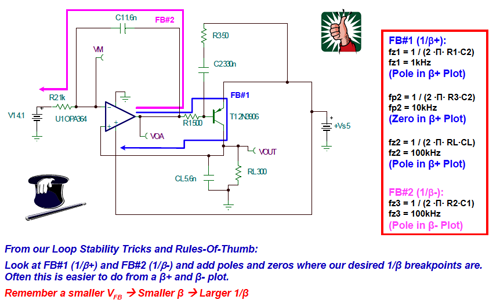

如果我们将1/β 曲线转化成β 曲线的话,我们将更容易将需的1/β 曲线综合至器件中。正如我们在反馈环路中“围绕”缓冲器电路一样, 我们可以更容易地知道在哪里增加所需的极点和零点。如图5.17 所示,我们利用有关β 和1/β 互为倒数的知识,可方便地画出β 曲线。在 FB#2 中我们需要增加fZ3。而在FB#1 中我们则需要增加fz1、fp2 与fz2。由于晶体管T1 的寄生电容,fp0 已经存在。

图5.17:得自1/β+的β+曲线与得自1/β- 的β-曲线

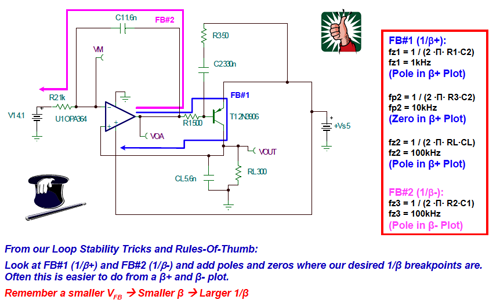

当我们看图5.18时,我们首先环顾FB#1周围,找出在哪里我们可以方便的加入fz1、fp2及fz2。由于在我们以β+视图沿着环路的行走过程中,fz1是一个极点,因此我们可以方便的通过增加 C2来加入该点,且可以利用已有的R1 来使用它。fp2作为β+视图中的零点,可以通过电阻R3与C2的串联来加入。fz2作为β+视图中的极点,可以通过增加电容CL 与负载电阻RL 并联来实现。事实上,CL起了双重作用。除有助于提高回路的稳定性外,它还作为阻性电桥负载的局部高频旁路,这里用RL来表示。FB#2要求我们加入β-视图中的极点fz3。这可通过增加反馈电容C1与输入电阻R2 来实现。鉴于完整性,我们考虑是否要将RO 的影响包括进来,RO是我们在计算β和1/ β时运放的开环输出电阻。对于OPA364,RO 为160Ω。对FB#2 来说,VOA是RO与T1基极输入(它看起来是个大阻抗)的中点。对于FB#1,RO与R1串联,为500Ω,这对我们的一阶分析来说并不会带来很大的误差。因此在此电路中,对于一阶分析,我们可以忽略RO的影响,同时检查与使用Tina SPICE仿真的结果是否相接近。

图5.18:用于稳定性的极点与零点综合

图字:

(β+曲线上的极点)

(β+曲线上的零点)

(β+曲线上的极点)

(β-曲线上的极点)

从我们的环路稳定性技巧和经验可得:

考虑FB#1(β+)和FB#2(β-),在我们所预计的1/β 断点处增加极点与零点,这通常在β+和β-曲线上较容易现。

请记住:VFB越小→β越小→1/β越大

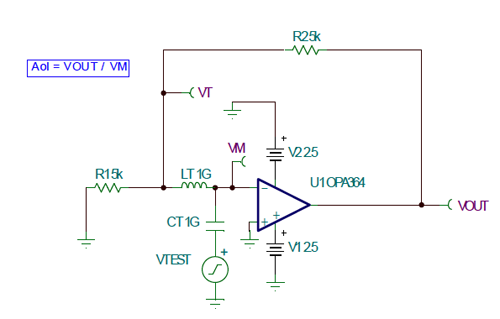

CMOS 放大器与Aol 注意点:

一个关于Aol 和CMOS 的注意点。随着CMOS 放大器输出负载的增加(负载阻值变小),Aol 曲线的直流部分在数值上减小。对如图 5.19 所示的OPA364 电路,我们看到VOUT 上有一个2MΩ的负载。图5.20 给出了用这个负载时,对Aol 曲线的Tina SPICE 仿真结果。我们注意到图5.20 中的直流Aol 值在10Hz 时扩大到大约118dB,这与图5.15 中的数据资料Aol 曲线不相符。

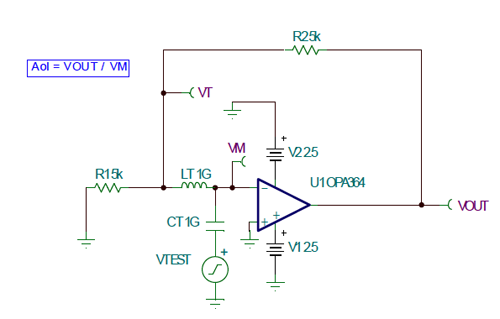

图5.19:OPA364 Aol 测试电路w/Load = 2MΩ

图5.20:OPA364 Aol w/Load = 2MΩ

图5.21所示电路在OPA364 的输出上加了10kΩ 的负载。这是在OPA364 数据资料Aol 曲线中给定的。我们对负载为10kΩ 的OPA364(图5.22)所进行的Tina SPICE 仿真结果与数据资料Aol 曲线相符。因此,在单电源缓冲器Tina SPICE 分析中,所给出的未加负载的OPA364 Aol 曲线也是正确的。因此这个OPA364 SPICE 模型准确地模拟了OPA364 CMOS 放大器在实际电路中的行为,即低频情况下输出负载改变时Aol 的变化。

图5.21:OPA364 Aol 测试电路w/Load = 10KΩ(数据资料Aol 曲线)

图5.22:OPA364 Aol w/Load = 10kΩ(数据资料Aol 曲线)

图字:OPA364 Aol 曲线、数据资料负载、Load=10kΩ、增益、频率

最终缓冲器分析:

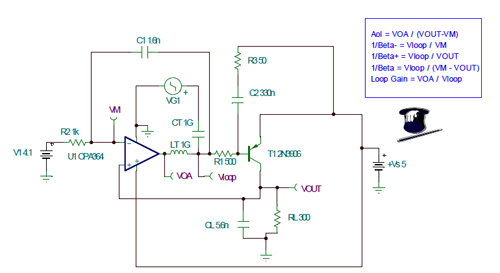

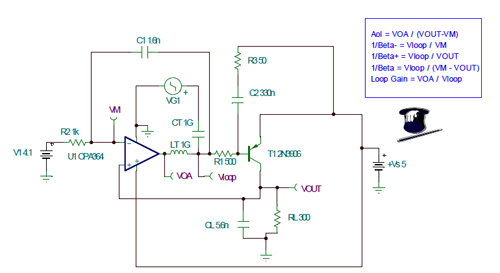

现在我们将用如图5.23 所示电路来对我们的补偿缓冲放大器电路进行Tina SPICE 分析。通过一个Tina SPICE交流分析运算,我们能得到图5.23 列出的公式所表示的所有感兴趣曲线。

图5.23:完整交流分析电路

在图5.24中,我们可以看到OPA364 Aol曲线和1/β+曲线及1/β-曲线。请注意,正如我们所预计的,在任何给定频率下,1/β 曲线的增益比1/β+曲线及1/β-曲线都要低。同样需注意的是,与我们的一阶分析相比,这些Tina SPICE 仿真曲线与我们所预计结果的相符!

图5.24:Aol、1/β+、1/β- 与1/β 曲线

那么,如果想对我们的稳定性画面进行仔细查看的话,我们可以使用从Tina SPICE 得到的环路增益幅度和相位曲线(见图5.25),从而可详细地查看我们在综合一个稳定的统一增益缓冲电路中的工作。我们的一个目的是避免相位余量在频率小于fcl 时降低到45 度以下。我们的结果不错,但在300kHz 附近稍微下降到了45 度以下,从那以后相位余量上升直至超出频率范围。

图5.25:环路增益 (Aolβ) 幅度与相位曲线

图5.26 所示电路将被用来预测及仿真VOUT/VIN 的交流闭环传输函数。

图5.26:VOUT/VIN 交流响应电路

图字:VOUT/VIN交流响应:VOUT/VG1

在我们的一阶分析曲线Aol、1/β+、1/β -及1/β曲线中,我们将增加一条预计的VOUT/VIN曲线以用于闭环交流响应(见图5.27)。从直流到fpx U1,OPA364 充当一个带有积分器功能的误差放大器,这样就迫使VOUT与VIN相匹配。在fpx处,由于XC1/R2 =1,积分器被强制设置成增益为1。从fpx 到 fpy ,由于XC1/R2 的存在,VOUT/VIN

继续以 -20dB/decade速度下降。在fpy处, VOUT/VIN继续沿Aol曲线下降,这是因为没有余下的环路增益(Aolβ)可用来校正误差。

图5.27:1 阶VOUT / VIN 分析

图字:从直流到fpx:

OPA364 充当一个带有积分器功能的误差放大器。VOUT/VIN=0dB

fpx 处:

XC1/R2=1

fpx 到 fpy:

由于XC1/R2,VOUT/VIN继续以-20db/decade下降

>fpy:

由于没有余下环路增益(Aolβ=0)可用来校正误差,因此VOUT/VIN随Aol下降

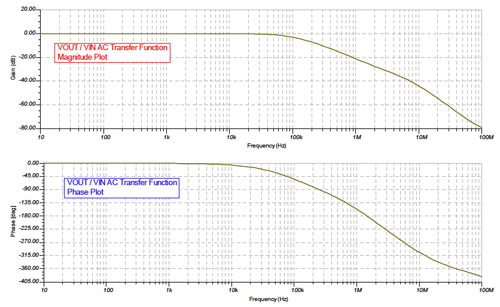

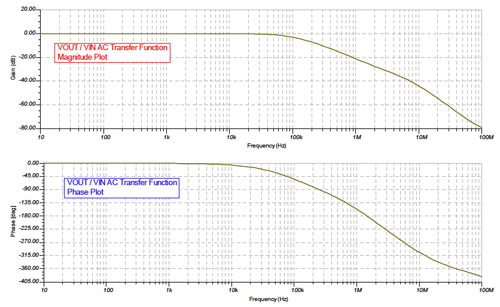

图5.28 给出了用Tina SPICE 仿真得到的VOUT/VIN 结果,该结果也表明它与我们从一阶分析得到的预测一致。我们还注意到,我们达到了缓冲放大器电路100kHz 小信号带宽的最初目标。

图5.28:VOUT / VIN SPICE 仿真结果

图字:VOUT/VIN 交流传输函数幅度曲线

VOUT/VIN 交流传输函数相位曲线

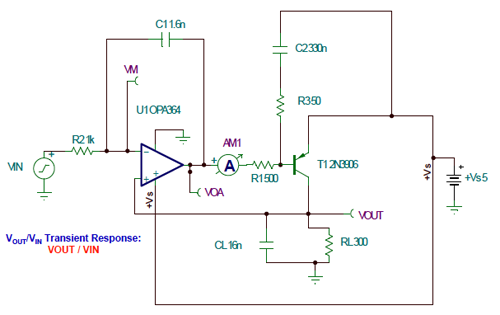

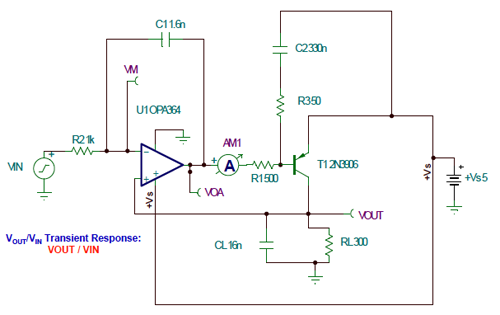

现在,让我们根据实际的稳定性测试,在Tina SPICE 上运行一个瞬态分析测试来查看过冲与振铃现象。图5.29给出了该电路。

图5.29:瞬态稳定性测试电路

图字:VOUT/VIN瞬态响应:VOUT/VIN

从Tina SPICE 瞬态分析得到如图5.30 所示的结果,表明VOUT 没有表现出过大的过冲和振铃,这是我们从环路稳定性分析中所预计到的。此外,我们还监测了在快速200mV 阶跃变化时(从4V 升至4.2V,又返回)从OPA364 流入和流出的电流。这里,也没有产生过大的电流尖峰,我们可以预计,我们现在的缓冲放大器电路运行良好、耐用、稳定、真实且具有统一增益。

图5.30:瞬态稳定性测试SPICE 结果

但等一等,这还不是全部。我们还在实验室实际电路中增加了稳定性网络,并对它进行了瞬态稳定性测试,结果如图5.31 所示。真是令人愉快的成功!我们从使用一阶分析,到使用Tina SPICE 仿真,再到最后使用实际电路稳定性测试,都证实了我们的缓冲放大电路是稳定的。我们的分析与综合技术证明是行之有效的,它得到了一种稳定、可靠、单电源、大电流的缓冲放大器电路。

图5.31:“实际瞬态稳定性测试结果” –––– 缓冲器拓扑 w/o 补偿

从 -40dB 到0dB 的距离较大,因此我们每次用掉数量上的一个十倍频程,这使我们得到如图5.16 所示的阶跃式上升,频率上也是如此。一旦我们在FB#1 曲线上达到1MHz,由于晶体管电容的寄生效应,我们需要加入高频极点(从1/Beta w/no 补偿曲线)。我们对FB#1 进行了所有能做的工作,但我们注意到它与Aol 曲线 以40dB/decade 的闭合速度相交。现在我们将增加第二条反馈路径FB#2。如果我们能将它加入我们的缓冲电路中(如图所示),则我们可以看到它将在频率大于1MHz 时占优势,且1/β 曲线和Aol 曲线将以20dB/decade 的闭合速度相交!!

图5.16:1 阶分析:Aol 与1/β 曲线

图字:所期望的FB#2 1/β-、所期望的FB#1 1/β+、所期望的1/Beta 1/(β--β+)、1/Beta w/no 补偿

如果我们将1/β 曲线转化成β 曲线的话,我们将更容易将需的1/β 曲线综合至器件中。正如我们在反馈环路中“围绕”缓冲器电路一样, 我们可以更容易地知道在哪里增加所需的极点和零点。如图5.17 所示,我们利用有关β 和1/β 互为倒数的知识,可方便地画出β 曲线。在 FB#2 中我们需要增加fZ3。而在FB#1 中我们则需要增加fz1、fp2 与fz2。由于晶体管T1 的寄生电容,fp0 已经存在。

图5.17:得自1/β+的β+曲线与得自1/β- 的β-曲线

当我们看图5.18时,我们首先环顾FB#1周围,找出在哪里我们可以方便的加入fz1、fp2及fz2。由于在我们以β+视图沿着环路的行走过程中,fz1是一个极点,因此我们可以方便的通过增加 C2来加入该点,且可以利用已有的R1 来使用它。fp2作为β+视图中的零点,可以通过电阻R3与C2的串联来加入。fz2作为β+视图中的极点,可以通过增加电容CL 与负载电阻RL 并联来实现。事实上,CL起了双重作用。除有助于提高回路的稳定性外,它还作为阻性电桥负载的局部高频旁路,这里用RL来表示。FB#2要求我们加入β-视图中的极点fz3。这可通过增加反馈电容C1与输入电阻R2 来实现。鉴于完整性,我们考虑是否要将RO 的影响包括进来,RO是我们在计算β和1/ β时运放的开环输出电阻。对于OPA364,RO 为160Ω。对FB#2 来说,VOA是RO与T1基极输入(它看起来是个大阻抗)的中点。对于FB#1,RO与R1串联,为500Ω,这对我们的一阶分析来说并不会带来很大的误差。因此在此电路中,对于一阶分析,我们可以忽略RO的影响,同时检查与使用Tina SPICE仿真的结果是否相接近。

图5.18:用于稳定性的极点与零点综合

图字:

(β+曲线上的极点)

(β+曲线上的零点)

(β+曲线上的极点)

(β-曲线上的极点)

从我们的环路稳定性技巧和经验可得:

考虑FB#1(β+)和FB#2(β-),在我们所预计的1/β 断点处增加极点与零点,这通常在β+和β-曲线上较容易现。

请记住:VFB越小→β越小→1/β越大

CMOS 放大器与Aol 注意点:

一个关于Aol 和CMOS 的注意点。随着CMOS 放大器输出负载的增加(负载阻值变小),Aol 曲线的直流部分在数值上减小。对如图 5.19 所示的OPA364 电路,我们看到VOUT 上有一个2MΩ的负载。图5.20 给出了用这个负载时,对Aol 曲线的Tina SPICE 仿真结果。我们注意到图5.20 中的直流Aol 值在10Hz 时扩大到大约118dB,这与图5.15 中的数据资料Aol 曲线不相符。

图5.19:OPA364 Aol 测试电路w/Load = 2MΩ

图5.20:OPA364 Aol w/Load = 2MΩ

图5.21所示电路在OPA364 的输出上加了10kΩ 的负载。这是在OPA364 数据资料Aol 曲线中给定的。我们对负载为10kΩ 的OPA364(图5.22)所进行的Tina SPICE 仿真结果与数据资料Aol 曲线相符。因此,在单电源缓冲器Tina SPICE 分析中,所给出的未加负载的OPA364 Aol 曲线也是正确的。因此这个OPA364 SPICE 模型准确地模拟了OPA364 CMOS 放大器在实际电路中的行为,即低频情况下输出负载改变时Aol 的变化。

图5.21:OPA364 Aol 测试电路w/Load = 10KΩ(数据资料Aol 曲线)

图5.22:OPA364 Aol w/Load = 10kΩ(数据资料Aol 曲线)

图字:OPA364 Aol 曲线、数据资料负载、Load=10kΩ、增益、频率

最终缓冲器分析:

现在我们将用如图5.23 所示电路来对我们的补偿缓冲放大器电路进行Tina SPICE 分析。通过一个Tina SPICE交流分析运算,我们能得到图5.23 列出的公式所表示的所有感兴趣曲线。

图5.23:完整交流分析电路

在图5.24中,我们可以看到OPA364 Aol曲线和1/β+曲线及1/β-曲线。请注意,正如我们所预计的,在任何给定频率下,1/β 曲线的增益比1/β+曲线及1/β-曲线都要低。同样需注意的是,与我们的一阶分析相比,这些Tina SPICE 仿真曲线与我们所预计结果的相符!

图5.24:Aol、1/β+、1/β- 与1/β 曲线

那么,如果想对我们的稳定性画面进行仔细查看的话,我们可以使用从Tina SPICE 得到的环路增益幅度和相位曲线(见图5.25),从而可详细地查看我们在综合一个稳定的统一增益缓冲电路中的工作。我们的一个目的是避免相位余量在频率小于fcl 时降低到45 度以下。我们的结果不错,但在300kHz 附近稍微下降到了45 度以下,从那以后相位余量上升直至超出频率范围。

图5.25:环路增益 (Aolβ) 幅度与相位曲线

图5.26 所示电路将被用来预测及仿真VOUT/VIN 的交流闭环传输函数。

图5.26:VOUT/VIN 交流响应电路

图字:VOUT/VIN交流响应:VOUT/VG1

在我们的一阶分析曲线Aol、1/β+、1/β -及1/β曲线中,我们将增加一条预计的VOUT/VIN曲线以用于闭环交流响应(见图5.27)。从直流到fpx U1,OPA364 充当一个带有积分器功能的误差放大器,这样就迫使VOUT与VIN相匹配。在fpx处,由于XC1/R2 =1,积分器被强制设置成增益为1。从fpx 到 fpy ,由于XC1/R2 的存在,VOUT/VIN

继续以 -20dB/decade速度下降。在fpy处, VOUT/VIN继续沿Aol曲线下降,这是因为没有余下的环路增益(Aolβ)可用来校正误差。

图5.27:1 阶VOUT / VIN 分析

图字:从直流到fpx:

OPA364 充当一个带有积分器功能的误差放大器。VOUT/VIN=0dB

fpx 处:

XC1/R2=1

fpx 到 fpy:

由于XC1/R2,VOUT/VIN继续以-20db/decade下降

>fpy:

由于没有余下环路增益(Aolβ=0)可用来校正误差,因此VOUT/VIN随Aol下降

图5.28 给出了用Tina SPICE 仿真得到的VOUT/VIN 结果,该结果也表明它与我们从一阶分析得到的预测一致。我们还注意到,我们达到了缓冲放大器电路100kHz 小信号带宽的最初目标。

图5.28:VOUT / VIN SPICE 仿真结果

图字:VOUT/VIN 交流传输函数幅度曲线

VOUT/VIN 交流传输函数相位曲线

现在,让我们根据实际的稳定性测试,在Tina SPICE 上运行一个瞬态分析测试来查看过冲与振铃现象。图5.29给出了该电路。

图5.29:瞬态稳定性测试电路

图字:VOUT/VIN瞬态响应:VOUT/VIN

从Tina SPICE 瞬态分析得到如图5.30 所示的结果,表明VOUT 没有表现出过大的过冲和振铃,这是我们从环路稳定性分析中所预计到的。此外,我们还监测了在快速200mV 阶跃变化时(从4V 升至4.2V,又返回)从OPA364 流入和流出的电流。这里,也没有产生过大的电流尖峰,我们可以预计,我们现在的缓冲放大器电路运行良好、耐用、稳定、真实且具有统一增益。

图5.30:瞬态稳定性测试SPICE 结果

但等一等,这还不是全部。我们还在实验室实际电路中增加了稳定性网络,并对它进行了瞬态稳定性测试,结果如图5.31 所示。真是令人愉快的成功!我们从使用一阶分析,到使用Tina SPICE 仿真,再到最后使用实际电路稳定性测试,都证实了我们的缓冲放大电路是稳定的。我们的分析与综合技术证明是行之有效的,它得到了一种稳定、可靠、单电源、大电流的缓冲放大器电路。

图5.31:“实际瞬态稳定性测试结果” –––– 缓冲器拓扑 w/o 补偿

电路 PIC 仿真 电容 电阻 CMOS 放大器 电流 相关文章:

- 整流电路(11-30)

- 单运放构成的单稳延时电路(11-29)

- 直流稳压电源电路(11-30)

- 基于ISP1581型接口电路的USB2.0接口设计(01-18)

- 单电源供电的IGBT驱动电路在铁路辅助电源系统中的应用(01-16)

- 为太阳能灯供电的低损耗电路的设计(01-22)