GC5322 在CDMA中的应用~*

时间:09-02

来源:互联网

点击:

作者:Chen,Andy TI HSP/Telecom team China

1.CDMA系统概况

1.1 CDMA关键指标需求

载波带宽:1.23M,1.24M,1.25M,不同的频段对应不同的带宽,900M 频段对应的是1.23M 带宽

码片速率:1.2288M

解调码域需求:MaxIT<=-29db; RHO>=0.97

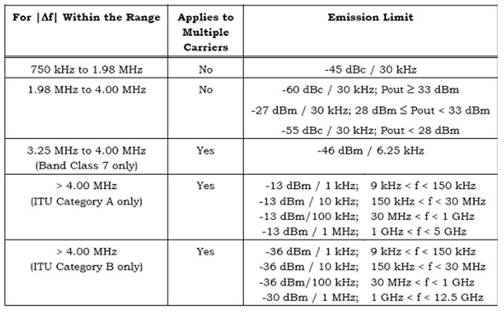

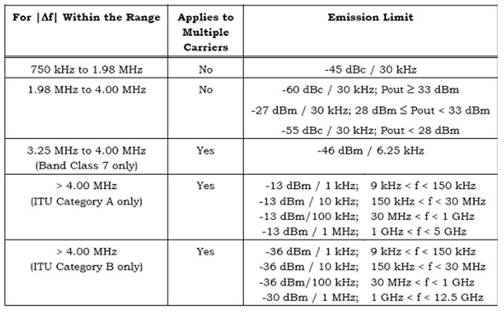

发射频谱杂散模板需求

表1

1.2 系统框图及时钟频率规划

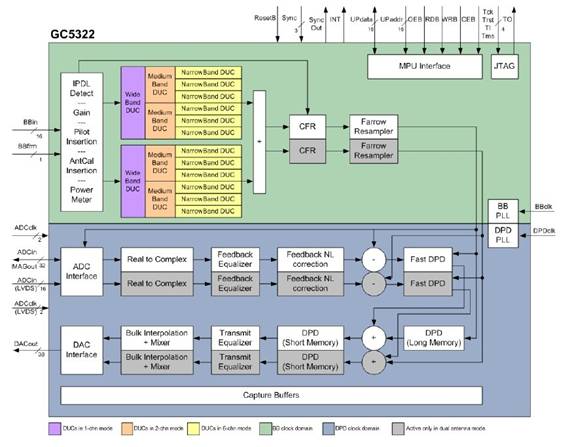

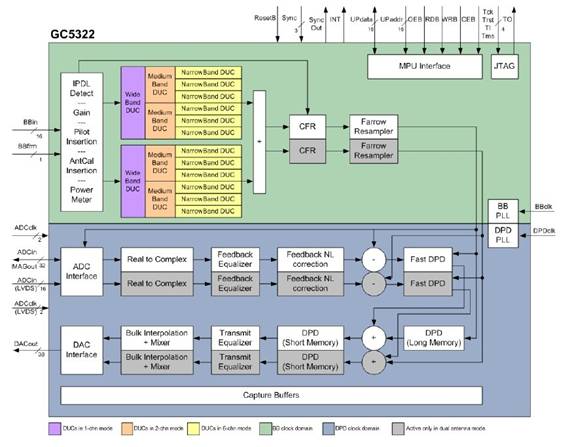

GC5322 内有DUC、CFR、DPD 三大模块(见图1),提供单芯片发射机解决方案,最大可支持20M 信号处理带宽。GC5322 有两种工作模式:单天线模式和双天线模式: 当用户选择单天线模式时,其DUC工作在窄带模式,最多可同时处理12 载波,总带宽为20M,如CDMA, TD-SCDMA;当用户选择双天线模式时,每天线最多可同时处理6 载波窄带信号,总带宽为10M,可校准5 阶非线性。本文主要讲述在单天线模式的CDMA 的应用。

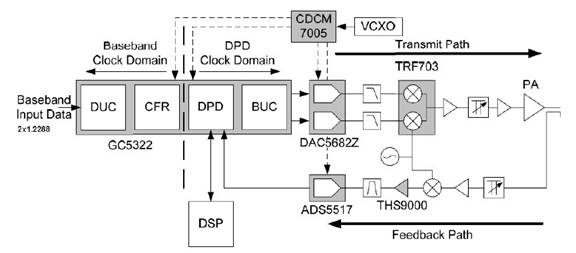

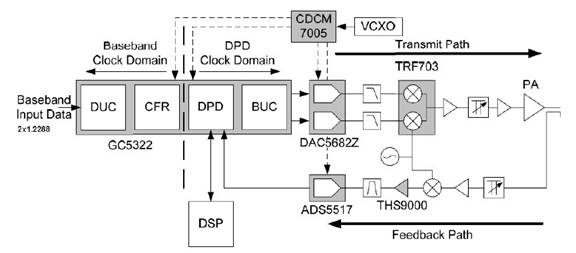

整个系统以GC5322 为核心,以其接口DAC 为DAC5682, ADC 为ADS5517(见图2), CDMA码片速率为1.2288,但输入到GC5322 的速率为2.4576M,这是因为在CDMA 应用中,通常用户会在DUC 之前用2 倍内插进行滤波,满足CDMA 系统基带处理的需求。下表是数据在整个链路的内插倍数分配。

表2

通过下表可以计算出CIC 的数据输出速率,也就是DUC的数据速率为61.44M, DPD的数据速率是92.16M,GC5322 的数据输出速率是184.32M,DAC 的采样率是737.28M,对应的时钟分配见下表:

表3

对于中频的选择,一般保证为(2n+1)/4*Fs(Fs 为反馈ADC 的采样率), 如果选择3/4*Fs,则中频为138.24M,在整个发射链路中,GC5322 的DUC,Farrow 重采样器,BUC 都有数字NCO 可供调频,这里我们选择在DAC 中调整Fs/4,BUC 中调整-46.08M,最终DAC输出为138.24 的复中频。

Figure 1 GC5322 系统框图

Figure 2 CDMA 系统框图

2.GC5322 关键参数计算及设置

2.1 GC5322 接口

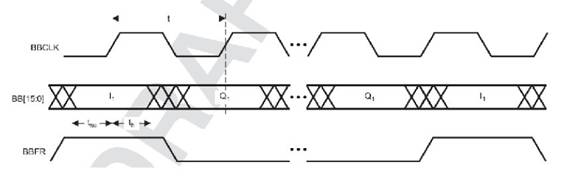

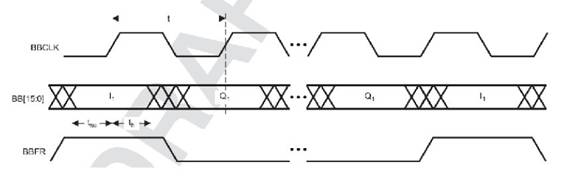

GC5322 输入接口共有18 位数据线(一般用16 位)、1 个时钟线(BBCLK)和1 个帧同步信BBFSR,其对应的时序关系如下图:

Figure 3 BBDATA 输入时序

本应用中BBCLK 是61.44M,输入的码片速率是2.4576M,最多可复用25 个I,Q 数据,此应用中为4 载波,因此还需要在补入17 个0,BBFSR 的频率为码片速率,其长度一般为一个BBCLK的周期。

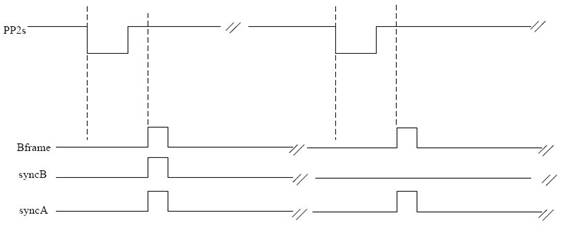

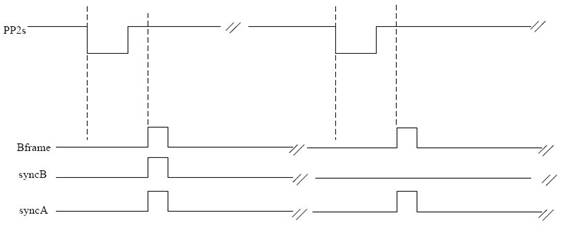

在CDMA EVDO 系统中,同步对整个系统是非常重要的,GC5322 有硬件同步和软件同步等多种同步方式,其内部各个功能模块可通过设置寄存器选择需要的同步方式。GC5322 共有4 个硬件同步输入管脚:SyncA,SyncB,SyncC,SyncD,本系统中用到了SyncA,SynCB 作为GC5322 的同步,其NCO 用SyncB 同步,其余的模块都用SyncA 同步,单独把NCO 分离出来用一个同步是因为EVDO 系统对NCO 的相位比较敏感,当载波连续时,是存在一组相位值使得每个通道的MaxIT 都较好。SyncA 是一个周期为26.6666ms 的周期信号(帧周期),SyncB 是用户可配的单周期信号,两者应具备如下关系:

Figure 4 SyncA 和SyncB

图中PP2s 是EVDO 整个系统的同步

2.2 DUC滤波器的设计

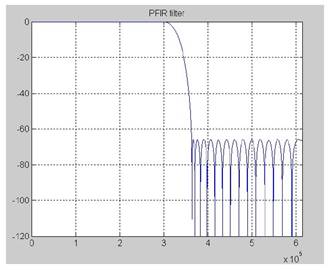

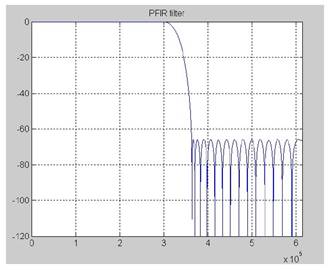

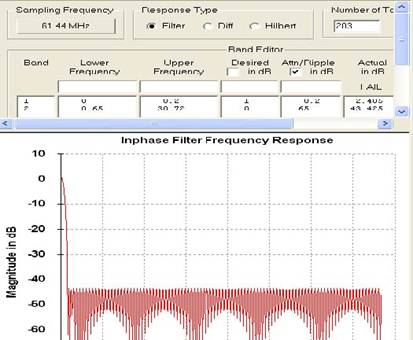

GC5322 的DUC主要由PFIR, CFIR,CIC 和NCO 组成,完成对信号的滤波,内插,搬移功能可以支持1 通道,2 通道以及6 通道模式。PFIR 主要对信号完成成形滤波,有1 倍内插和2倍内插两种模式,这里我们用1 倍内插模式,最大滤波器长度为127(对于不同的标准最大滤波器长度不一样),一般PFIR 的设计方法有低通和RRC 两种,对于CDMA 多数采用低通滤波器。下图5 是一个PFIR 的频谱响应,其为低通滤波器,通带波动为0.05db,阻带衰减为80db,长度为61。

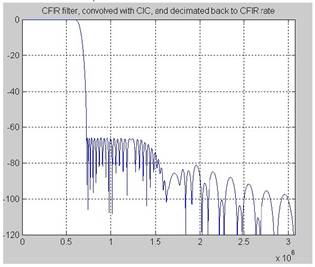

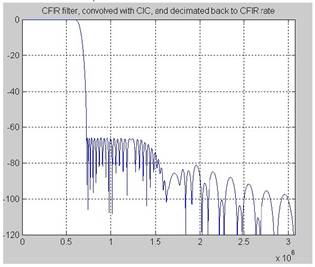

CFIR 的主要目的是用来补偿CIC 引起的通带不平坦,可以完成1.5,2,2.5 或3 倍的内插,最大长度取决于输入数据速率和内插倍数,其设计方法同时用一低通滤波器与一段反sinc 卷积得到,在设计低通滤波器时,其通带和阻带一般要比PFIR 的通带阻带略宽,这是为了保证其不影响PFIR 的性能。下图6 是CFIR 和CIC 卷积后的频谱。

Figure 5 PFIR 频谱响应

Figure 6 CFIR 频谱响应

2.3 CFR参数的设定

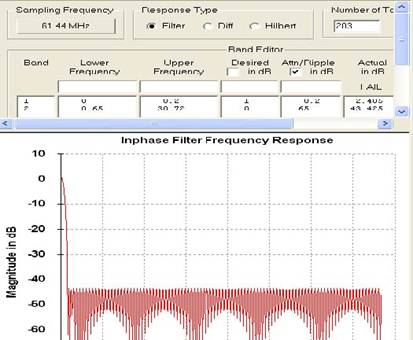

与CFR 有关的参数包括削峰门限、滤波器、削峰脉冲的分配等,其中最关键的是滤波器和削峰门限的确定,如果系统有多个载波,削峰滤波器与载波的位置有关系,即与NCO 的频点值有关系。以4 载波CDMA 为例,如果载波位置发生变化,则CFR 滤波器要作相应的更新,我们通常与设计PFIR 的方法类似,设计一个CDMA 单载波的低通滤波器,只是其阻带抑制一般比PFIR略低,然后将这个单载波低通滤波器搬移到各个载波位置上然后合成。滤波器的阻带抑制一般影响信号的ACPR, 如果这个值设置得过高过低,都会引起ACPR 的恶化。GC5322 最大的CFR tap数为256,通常CFR 的运行速率和DUC 的输出速率一样,对于CDMA 来说,都为61.44M。下图是一个用ScopeFIR 设计的CDMA CFR 滤波器的例子,实际应用中要根据需要调整阻带抑制以得到最好的ACPR,其原则是削峰前后信号的ACPR 要基本一致。

Figure 7 CFR 滤波器

CFR另一个重要参数就是门限,门限的确定主要根据信号的输入功率而定,在GC5322 应用中,我们通常固定门限,用户可以通过调整增益而获得合适的PAR输出,增益越高,PAR输出越小,EVM(CDMA对应的是RHO和MaxIT)就会越大,反之PAR输出越大,EVM越小,根据系统的需求在一定EVM(RHO)内获得尽可能低的PAR输出。对于CDMA EVDO系统而言,门限的设置非常关键,以4 载波EVDO系统为例,其原始PAR很高,一般在[email=13db@0.01%]13db@0.01%[/email],如果门限设置的过高,意味着如果要想获得尽可能低的PAR,必须设置很高的增益,这可能会引起sumchain益处,在频谱上会看到很多毛刺,如果门限设置的过低,会造成DA低信号输出,因此模拟链路需要更多的增益,这会带来大的噪声,不利于整个系统。

一般CDMA EVDO 系统中,首先根据信号的PEAK 值(可以通过GC5322 的功率检测得到)确定CFR 计算门限所需的RMS 值,然后根据削峰量来确定门限。

GC5322 多处可以调整信号的增益,主要有3 处,DUC通道增益,合波后的增益,以及LONGDPD里的增益,其中影响CFR 的是前2 处,合理分配这两处的增益以及合理的门限设置非常关键,尤其要注意sumchain 的益处,否则会影响信号输出的质量,而带来小的毛刺,从而影响杂散模板的测试。

3.总结

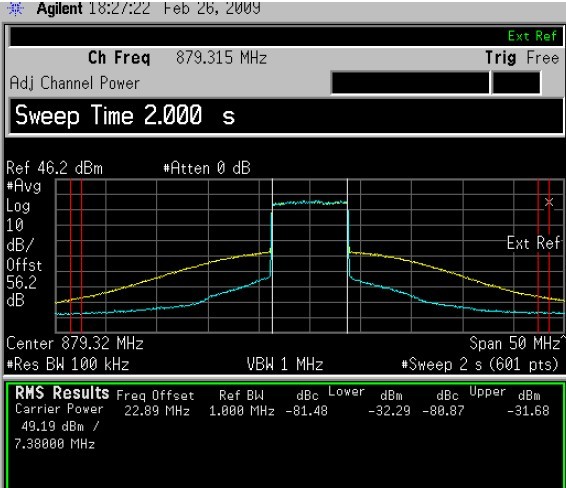

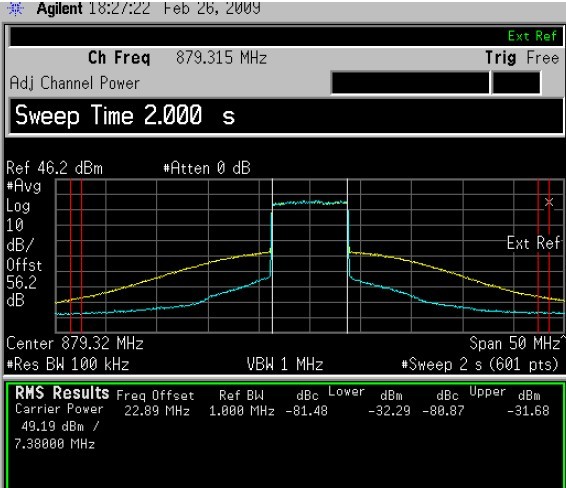

本文虽然描述的是GC5322 在CDMA 中的应用,但各标准之间的差异主要是在带宽和码片速率,对于GC5322 而言只是duc 的应用稍有不同,其设计方法和思路都是一样的。下图是采用GC5322 后实测的DPD 对功放的线性改善结果,信号是CDMA6 载波,总带宽为7.38M,黄线是DPD 前,蓝线是DPD 后,其近端有21db 的改善。

Figure 8 GC5322 实测效果图

DPD 系统是一个很复杂的系统,GC5322 的参数设置是保证系统正常运行的前提,其中较为复杂的是DUC 和CFR 参数的设置,DPD 主要完成非线性的校准功能,只要设置正确的速率和合适的中频,DPD 就能正常的运行,但是要发挥出DPD 的最优的性能,需要和射频、DUC 和CFR的参数结合起来,尤其射频的增益分配,噪声系数都会以及链路的毛刺等因素都会影响DPD 的性能,因此如果要发挥GC5322 的最大的性能,需要认真仔细设计系统中的任何部分,尤其是射频链路。

1.CDMA系统概况

1.1 CDMA关键指标需求

载波带宽:1.23M,1.24M,1.25M,不同的频段对应不同的带宽,900M 频段对应的是1.23M 带宽

码片速率:1.2288M

解调码域需求:MaxIT<=-29db; RHO>=0.97

发射频谱杂散模板需求

表1

1.2 系统框图及时钟频率规划

GC5322 内有DUC、CFR、DPD 三大模块(见图1),提供单芯片发射机解决方案,最大可支持20M 信号处理带宽。GC5322 有两种工作模式:单天线模式和双天线模式: 当用户选择单天线模式时,其DUC工作在窄带模式,最多可同时处理12 载波,总带宽为20M,如CDMA, TD-SCDMA;当用户选择双天线模式时,每天线最多可同时处理6 载波窄带信号,总带宽为10M,可校准5 阶非线性。本文主要讲述在单天线模式的CDMA 的应用。

整个系统以GC5322 为核心,以其接口DAC 为DAC5682, ADC 为ADS5517(见图2), CDMA码片速率为1.2288,但输入到GC5322 的速率为2.4576M,这是因为在CDMA 应用中,通常用户会在DUC 之前用2 倍内插进行滤波,满足CDMA 系统基带处理的需求。下表是数据在整个链路的内插倍数分配。

| Fin | PFIR | CFIR | CIC | Farrow RS | BUC | DAC |

| 1.2288x2 | x1 | x2.5 | x10 | x1.5 | x2 | x4 |

表2

通过下表可以计算出CIC 的数据输出速率,也就是DUC的数据速率为61.44M, DPD的数据速率是92.16M,GC5322 的数据输出速率是184.32M,DAC 的采样率是737.28M,对应的时钟分配见下表:

| BBCLK | DPDCLK | ADS5517 | DAC5682 |

| 61.44 | 184.32 | 184.32 | 737.28 |

表3

对于中频的选择,一般保证为(2n+1)/4*Fs(Fs 为反馈ADC 的采样率), 如果选择3/4*Fs,则中频为138.24M,在整个发射链路中,GC5322 的DUC,Farrow 重采样器,BUC 都有数字NCO 可供调频,这里我们选择在DAC 中调整Fs/4,BUC 中调整-46.08M,最终DAC输出为138.24 的复中频。

Figure 1 GC5322 系统框图

Figure 2 CDMA 系统框图

2.GC5322 关键参数计算及设置

2.1 GC5322 接口

GC5322 输入接口共有18 位数据线(一般用16 位)、1 个时钟线(BBCLK)和1 个帧同步信BBFSR,其对应的时序关系如下图:

Figure 3 BBDATA 输入时序

本应用中BBCLK 是61.44M,输入的码片速率是2.4576M,最多可复用25 个I,Q 数据,此应用中为4 载波,因此还需要在补入17 个0,BBFSR 的频率为码片速率,其长度一般为一个BBCLK的周期。

在CDMA EVDO 系统中,同步对整个系统是非常重要的,GC5322 有硬件同步和软件同步等多种同步方式,其内部各个功能模块可通过设置寄存器选择需要的同步方式。GC5322 共有4 个硬件同步输入管脚:SyncA,SyncB,SyncC,SyncD,本系统中用到了SyncA,SynCB 作为GC5322 的同步,其NCO 用SyncB 同步,其余的模块都用SyncA 同步,单独把NCO 分离出来用一个同步是因为EVDO 系统对NCO 的相位比较敏感,当载波连续时,是存在一组相位值使得每个通道的MaxIT 都较好。SyncA 是一个周期为26.6666ms 的周期信号(帧周期),SyncB 是用户可配的单周期信号,两者应具备如下关系:

Figure 4 SyncA 和SyncB

图中PP2s 是EVDO 整个系统的同步

2.2 DUC滤波器的设计

GC5322 的DUC主要由PFIR, CFIR,CIC 和NCO 组成,完成对信号的滤波,内插,搬移功能可以支持1 通道,2 通道以及6 通道模式。PFIR 主要对信号完成成形滤波,有1 倍内插和2倍内插两种模式,这里我们用1 倍内插模式,最大滤波器长度为127(对于不同的标准最大滤波器长度不一样),一般PFIR 的设计方法有低通和RRC 两种,对于CDMA 多数采用低通滤波器。下图5 是一个PFIR 的频谱响应,其为低通滤波器,通带波动为0.05db,阻带衰减为80db,长度为61。

CFIR 的主要目的是用来补偿CIC 引起的通带不平坦,可以完成1.5,2,2.5 或3 倍的内插,最大长度取决于输入数据速率和内插倍数,其设计方法同时用一低通滤波器与一段反sinc 卷积得到,在设计低通滤波器时,其通带和阻带一般要比PFIR 的通带阻带略宽,这是为了保证其不影响PFIR 的性能。下图6 是CFIR 和CIC 卷积后的频谱。

Figure 5 PFIR 频谱响应

Figure 6 CFIR 频谱响应

2.3 CFR参数的设定

与CFR 有关的参数包括削峰门限、滤波器、削峰脉冲的分配等,其中最关键的是滤波器和削峰门限的确定,如果系统有多个载波,削峰滤波器与载波的位置有关系,即与NCO 的频点值有关系。以4 载波CDMA 为例,如果载波位置发生变化,则CFR 滤波器要作相应的更新,我们通常与设计PFIR 的方法类似,设计一个CDMA 单载波的低通滤波器,只是其阻带抑制一般比PFIR略低,然后将这个单载波低通滤波器搬移到各个载波位置上然后合成。滤波器的阻带抑制一般影响信号的ACPR, 如果这个值设置得过高过低,都会引起ACPR 的恶化。GC5322 最大的CFR tap数为256,通常CFR 的运行速率和DUC 的输出速率一样,对于CDMA 来说,都为61.44M。下图是一个用ScopeFIR 设计的CDMA CFR 滤波器的例子,实际应用中要根据需要调整阻带抑制以得到最好的ACPR,其原则是削峰前后信号的ACPR 要基本一致。

Figure 7 CFR 滤波器

CFR另一个重要参数就是门限,门限的确定主要根据信号的输入功率而定,在GC5322 应用中,我们通常固定门限,用户可以通过调整增益而获得合适的PAR输出,增益越高,PAR输出越小,EVM(CDMA对应的是RHO和MaxIT)就会越大,反之PAR输出越大,EVM越小,根据系统的需求在一定EVM(RHO)内获得尽可能低的PAR输出。对于CDMA EVDO系统而言,门限的设置非常关键,以4 载波EVDO系统为例,其原始PAR很高,一般在[email=13db@0.01%]13db@0.01%[/email],如果门限设置的过高,意味着如果要想获得尽可能低的PAR,必须设置很高的增益,这可能会引起sumchain益处,在频谱上会看到很多毛刺,如果门限设置的过低,会造成DA低信号输出,因此模拟链路需要更多的增益,这会带来大的噪声,不利于整个系统。

一般CDMA EVDO 系统中,首先根据信号的PEAK 值(可以通过GC5322 的功率检测得到)确定CFR 计算门限所需的RMS 值,然后根据削峰量来确定门限。

GC5322 多处可以调整信号的增益,主要有3 处,DUC通道增益,合波后的增益,以及LONGDPD里的增益,其中影响CFR 的是前2 处,合理分配这两处的增益以及合理的门限设置非常关键,尤其要注意sumchain 的益处,否则会影响信号输出的质量,而带来小的毛刺,从而影响杂散模板的测试。

3.总结

本文虽然描述的是GC5322 在CDMA 中的应用,但各标准之间的差异主要是在带宽和码片速率,对于GC5322 而言只是duc 的应用稍有不同,其设计方法和思路都是一样的。下图是采用GC5322 后实测的DPD 对功放的线性改善结果,信号是CDMA6 载波,总带宽为7.38M,黄线是DPD 前,蓝线是DPD 后,其近端有21db 的改善。

Figure 8 GC5322 实测效果图

DPD 系统是一个很复杂的系统,GC5322 的参数设置是保证系统正常运行的前提,其中较为复杂的是DUC 和CFR 参数的设置,DPD 主要完成非线性的校准功能,只要设置正确的速率和合适的中频,DPD 就能正常的运行,但是要发挥出DPD 的最优的性能,需要和射频、DUC 和CFR的参数结合起来,尤其射频的增益分配,噪声系数都会以及链路的毛刺等因素都会影响DPD 的性能,因此如果要发挥GC5322 的最大的性能,需要认真仔细设计系统中的任何部分,尤其是射频链路。

- D类MOSFT在发射机射频功放中的应用(11-18)

- 单片射频收发芯片A7105的原理与应用(10-12)

- LDO电源管理模块的分析及其在数字模拟射频系统中的应用(01-26)

- 如何完善您的射频采样解决方案?(11-26)

- 核磁共振系统中射频开关设计(01-04)

- 基于MATLAB仪器控制工具箱的SAW标签阅读器系统设计(06-24)