LMK04800:双回路PLL低噪音时钟抖动消除方案

时间:06-16

来源:互联网

点击:

NS公司的LMK04800系列是双回路PLL的低噪音时钟抖动消除器,具有超低的RMS抖动性能:12kHz~20MHz为111fs RMS,100Hz~20MHz为123fs RMS,工作电压3.15V~3.45V,时钟速率高达1536 MHz,可以满足新一代系统所需的要求,主要用在数据转换器时钟、无线基础设备、网络、SONET/SDH、DSLAM、医疗、视频以及测试测量设备等。

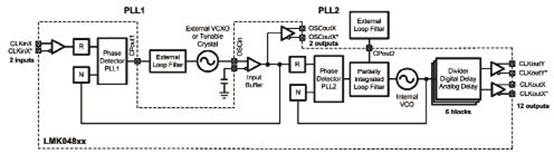

该LMK04800系列是业界最高性能的时钟调节器,具有优越的时钟抖动清除、生成和分配性能,并具有其它先进功能,以满足下一代系统时钟调整的要求。这种双循环PLLatinum™架构,可以采用低噪声VCXO模块,提供111fs rms抖动(12kHz至20MHz)或者,采用低成本的外部晶体和变容二极管,提供次200fs rms抖动(12kHz至20MHz)。

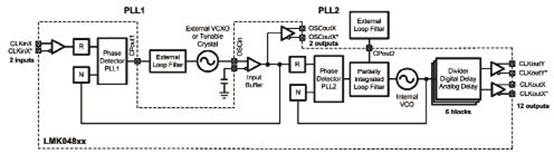

这种双循环结构包括两个高性能锁相环(PLL)电路,一个低噪声晶体振荡器电路,以及高性能的电压控制振荡器(VCO),第一个锁相环(PLL1)提供了低噪声抖动清除器的功能,而第二个锁相环(PLL2的)执行时钟产生。

PLL1可配置成与外部VCXO模块工作,或者与具有外部可调晶体和变容二极管的集成晶体振荡器工作。当被用于很窄的环路带宽时,PLL1使用VCXO模块,或可调晶体的优异相位噪声(偏移低于50千赫),以清理输入时钟。 PLL1的输出作为PLL2的清除输入参考,以锁定集成的VCO。 PLL2的环路带宽可以进行优化,以清除远出相位噪声(偏移50千赫以上),集成的VCO优于VCXO模块,或PLL1使用的可调晶体。

图1 LMK0480x详细方框图

LMK04800主要特性

•超低RMS抖动性能

- 111 fs RMS抖动(12 kHz至20 MHz)

- 123 fs RMS抖动(100 Hz至20 MHz)

•双回路PLLatinum PLL架构

- PLL1

•集成的低噪声晶体振荡器电路

•输入时钟丢失时为保持模式

- 自动或手动触发/恢复

• 正常[1 Hz]锁相环底噪声-227 dBc/Hz

•最高相探测器率155兆赫

• OSCin频率倍增

•集成低噪声压控振荡器

• 2个Los冗余输入时钟

- 自动和手动切换模式

• 50%占空比输出分离,1至1045(奇偶)

• LVPECL,LVDS或LVCMOS的可编程输出

•精密数字延时,固定或动态调整

• 25 ps步模拟延时控制。

• 14个差分输出,最多26个单端。

- 最多6个压控/水晶缓冲输出

• 时钟速率高达1536兆赫

• 零延迟模式

• 三个上电默认时钟输出

• 多模式:双锁相环,单PLL和时钟分配

• 工业级温度范围:-40至85℃

• 3.15 V至3.45 V工作电压

•封装:64引脚LLP(9.0 ×9.0 ×0.8毫米)

图2 双回路模式的LMK0480x简化方框图

LMK04800目标应用

•数据转换器时钟/无线基础设施

•网络:SONET / SDH ,DSLAM

•医疗/视频/军事/航空航天

•测试和测量

详情请见:

http://solution.eccn.com/solution_2011050309550763.htm

该LMK04800系列是业界最高性能的时钟调节器,具有优越的时钟抖动清除、生成和分配性能,并具有其它先进功能,以满足下一代系统时钟调整的要求。这种双循环PLLatinum™架构,可以采用低噪声VCXO模块,提供111fs rms抖动(12kHz至20MHz)或者,采用低成本的外部晶体和变容二极管,提供次200fs rms抖动(12kHz至20MHz)。

这种双循环结构包括两个高性能锁相环(PLL)电路,一个低噪声晶体振荡器电路,以及高性能的电压控制振荡器(VCO),第一个锁相环(PLL1)提供了低噪声抖动清除器的功能,而第二个锁相环(PLL2的)执行时钟产生。

PLL1可配置成与外部VCXO模块工作,或者与具有外部可调晶体和变容二极管的集成晶体振荡器工作。当被用于很窄的环路带宽时,PLL1使用VCXO模块,或可调晶体的优异相位噪声(偏移低于50千赫),以清理输入时钟。 PLL1的输出作为PLL2的清除输入参考,以锁定集成的VCO。 PLL2的环路带宽可以进行优化,以清除远出相位噪声(偏移50千赫以上),集成的VCO优于VCXO模块,或PLL1使用的可调晶体。

图1 LMK0480x详细方框图

LMK04800主要特性

•超低RMS抖动性能

- 111 fs RMS抖动(12 kHz至20 MHz)

- 123 fs RMS抖动(100 Hz至20 MHz)

•双回路PLLatinum PLL架构

- PLL1

•集成的低噪声晶体振荡器电路

•输入时钟丢失时为保持模式

- 自动或手动触发/恢复

• 正常[1 Hz]锁相环底噪声-227 dBc/Hz

•最高相探测器率155兆赫

• OSCin频率倍增

•集成低噪声压控振荡器

• 2个Los冗余输入时钟

- 自动和手动切换模式

• 50%占空比输出分离,1至1045(奇偶)

• LVPECL,LVDS或LVCMOS的可编程输出

•精密数字延时,固定或动态调整

• 25 ps步模拟延时控制。

• 14个差分输出,最多26个单端。

- 最多6个压控/水晶缓冲输出

• 时钟速率高达1536兆赫

• 零延迟模式

• 三个上电默认时钟输出

• 多模式:双锁相环,单PLL和时钟分配

• 工业级温度范围:-40至85℃

• 3.15 V至3.45 V工作电压

•封装:64引脚LLP(9.0 ×9.0 ×0.8毫米)

图2 双回路模式的LMK0480x简化方框图

LMK04800目标应用

•数据转换器时钟/无线基础设施

•网络:SONET / SDH ,DSLAM

•医疗/视频/军事/航空航天

•测试和测量

详情请见:

http://solution.eccn.com/solution_2011050309550763.htm

- 选择最佳的电压基准源(11-29)

- 对电压参考进行滤波以获得低噪声性能(01-16)

- 可编程快速充电管理芯片MAX712/ MAX713及其应用(01-23)

- 改进型全桥移相ZVS-PWMDC/DC变换器(01-23)

- 负输出罗氏变换器实用性剖析(01-09)

- 通信电源设备对杂音电压的控制要求(02-13)