Gbps无线基站设计中Virtex-5FPGA的应用

本文基于Virtex-5FPGA设计面向未来移动通信标准的Gbps无线通信基站系统,具有完全的可重配置性,可以完成MIMO、OFDM及LDPC等复杂信号处理算法,实现1Gbps速率的无线通信。

引言

随着集成电路(IC)技术进入深亚微米时代,片上系统SoC(SySTem-ON-a-Chip)以其显着的优势成为当代IC设计的热点。基于软硬件协同设计及IP复用技术的片上系统具有功能强大、高集成度和低功耗等优点,可显着降低系统体积和成本,缩短产品上市的时间。IP核是SoC设计的一个重要组成部分,已成为目前微电子设计的热点和主要方向[1]。

UART 核以其可靠性、传送距离远的特点被广泛应该到通信系统和嵌入式微处理器上。利用传统的EDA工具通过对RTL代码仿真、验证、综合、布局布线后生成网表,下载到FPGA中实现,这样做成的核主要用于验证的[2],不适合用来做掩膜。在ASIC/SoC技术日渐成熟的今天,设计商更希望得到能够做掩膜的IP核,从而便于嵌入到ASIC/SoC设计中。本文描述的UART核采用SYNOPSYS软件的设计流程,在RTL级上进行优化,解决了综合优化中碰到的一些常见问题。利用VCS 仿真、编写测试激励来验证,最后用design compile 综合优化做成的IP核可以满足此要求,应用到ASIC/SoC设计中将产生巨大的效益。

Gbps无线通信系统的算法链路设计

为满足未来移动通信标准的需要[3],在算法链路上Gbps系统采用时分双工(TDD)、多天线(MIMO)、空时编码、正交频分复用(OFDM)、高阶调制和LDPC编码等高性能物理层传输技术,以实现Gbps系统所需的高数据速率业务传输和高频谱效率。以频分、时分为主的多址方式实现,能够在多天线环境下对无线资源进行灵活调配,在兼顾实时话音传输的同时,最大程度上满足分组数据传输的需要。

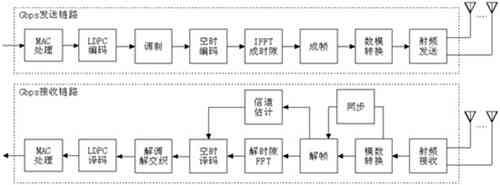

具体而言,Gbps系统使用3.4GHz频段,实际带宽100MHz,移动台采用2发4收的天线,基站采用4发8收的天线,OFDM子载波数为2048子载波,有效为1664子载波。图1是Gbps无线传输系统的算法链路示意图。

图1Gbps无线传输系统算法链路

Gbps基站系统的设计实现考虑

移动通信基站往往在一个站址上同时有GSM、TD-SCDMA等多种标准的基站,越来越多地呈现多标准共存的局面,基站研发应当着眼于降低建设、运营维护和升级成本。对此,Gbps无线通信基站应当采用可重配置方式,在支持Gbps无线传输的同时能够兼容未来的LTE-A、IMT-Advanced标准,实现平滑演进。

从实现技术上看,实现信号处理算法并支持可重配置需要可编程的处理器件,现代基站系统广泛采用的可编程处理器以DSP和FPGA为主。尽管高端多核DSP的工作时钟频率已经提升到1.2GHz,在TD-SCDMA基站中得到广泛应用,但还是无法满足Gbps系统中同步、MIMO、LDPC等算法对信号处理复杂度和实时性的要求。因此,Gbps项目需要采用大容量的高性能FPGA来作为复杂算法的承载平台。

从基站系统的互连与数据传输机制上看,互连连接所有的无线接口、网络接口和计算资源,传输代表计算任务的数据,是使基站系统成为整体、协调运行的关键要素。由于MIMO算法需要多天线输入数据到多基带处理芯片的传输,应当采用以交换式互连网络和分组数据传输机制,更好满足未来基站系统中MIMO、并行处理、动态可重配置、计算资源动态调度等的需要。

综合以上设计实现考虑,经过综合调研考察,Gbps项目决定采用Xilinx公司Virtex-5系列FPGA构架硬件系统平台[4],承载复杂的信号处理算法,采用串行RapidIO[5]技术作为板间高性能互连,采用千兆以太网(GE)连接业务服务器及LMT计算机。

Virtex-5FPGA介绍

Virtex-5系列FPGA是Xilinx率先发布和量产的65nm平台FPGA,目前包括LX、LXT、SXT、FXT及TXT等面向不同应用的多个子系列。

Virtex-5系列FPGA最高工作时钟可以达到550MHz,总逻辑单元数多达330,000个。提供了高达11.6Mbit的灵活嵌入式BlockRAM,能有效地存储和缓冲各种运算数据。多达640个

增强型嵌入式DSP48Eslice块,可以满足高性能DSP算法加速的需要,实现352GMACs的性能。Virtex-5FXT系列FPGA提供多达两个标准的PowerPC 440处理器模块,每个处理器在550 MHz时钟频率下可提供1,100 DMIPS 的性能。利用PowerPC 440嵌入式处理器模块,可快速方便地实现Gbps基站中复杂的控制和通信协议处理。

Virtex-5系列FPGA集成100Mbps–6.5Gbps的高性能收发器,配合FPGA内部编程实现的串行RapidIO逻辑层模块可以实现芯片间和板间高性能的数据交换互连。集成符合IEEE802.3标准的10/100/1000Mbps以太网MAC硬核,连接外部GEPHY或直接使用FPGA本身的GTP/GTX,就可以实现高性能的千兆以太网接口。

算法对

Virtex-5FPGA Gbps 无线通信基站 可重配置 相关文章:

- 40G光传输网络中的OPM应用(05-27)

- 光纤的调制方法(07-02)

- 基于Virtex-5 FPGA的Gbps通信基站设计(01-06)

- 第五代WiFi无线速率将达1Gbps(01-15)

- 索尼开发6.3Gbps毫米波通信技术(01-27)