有源电力滤波器中锁相倍频电路的实现

时间:10-27

来源:互联网

点击:

有源电力滤波器(ActivePowerFilter,APF)是一种动态抑制谐波和补偿无功的电力电子装置。锁相倍频电路是有源电力滤波器谐波检测模块的重要组成部分,它的稳定性对有源电力滤波器快速响应起到了关键的作用。供电系统的信号频率随负载的变化在较大的范围内变化,为实现准确的信号采样,DSP必须准确的知道当前信号的频率,确保采样频率与信号频率保持一致。锁相倍频电路就是将一个完整的周期等分成N份,作为DSP的采样信号。

1 锁相倍频电路的原理

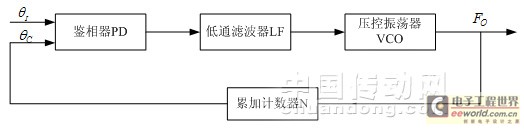

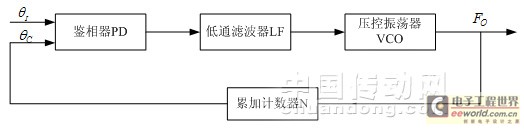

锁相倍频电路能否实时稳定的输出12.8kHz的方波,是整个检测模块在开机后能否在最短时间内开始工作的关键。图1所示为锁相倍频电路的原理框图。

图1锁相倍频电路的原理框图

由图1可以看出,锁相倍频电路是一个闭环频率反馈系统,它主要由鉴相器、低通滤波器、压控振荡器和累加计数器构成。

鉴相器是使输出电压与两个输入信号之间的相位差有确定关系的电路,它是锁相环PLL(PhaseLockedLoop)的基本部件之一,鉴相器可以分为模拟鉴相器和数字鉴相器两种。

鉴相器的输出信号包含很多的谐波分量,当锁相环处于锁定状态时,这些分量的第一项为“直流”分量,其它频率的分量为不需要的信号,而且在锁相倍频电路的信号传递中,也会有高频噪声对信号产生干扰,这些较高频率的分量也是不需要的信号,所以要用低通滤波器将其滤除。在此设计中,采用一阶低通滤波器。

压控振荡器是输出频率与输入电压有对应关系的振荡电路VCO(Voltage-controlledOscillator),在自动频率控制环路和锁相环环路中,输入控制电压是误差信号电压,压控振荡器是环路中的一个受控部件。

在APF的检测系统中,锁相倍频电路的输出作为启动AD采样的信号,分频器将VCO产生的输出信号频率除以N,这个因子多数情况下可变或可编程控制,分频器通常由触发器(如RS触发器、JK触发器或是T触发器)级联而成,一个JK触发器可以将加到它的时钟输入端信号2分频,两个就是4分频等。

在此电路中,使用了二进制加法计数器CD4040,即其累加数均为2的倍数,如要得到256倍,即把输出信号从其Q8脚输出。

2锁相倍频电路的设计

2.1过零检测电路

过零检测电路原理图如图2所示。电路中采用宇波CHV-25P霍尔电压传感器,此霍尔电压传感器的额定电流为10mA,原边与副边匝数比为2500:1000,所以在将A相电网电压接入霍尔电压传感器前,需要通过一个限流电阻进行限流,以免电流过大将霍尔电压传感器烧坏,它的M端为副边电流输出端,需要加一支采样电阻,将电阻上的压降引入一个由运算放大器CA3140及四个电阻组成的滞回比较器,然后在其输出端通过一个由两个二极管组成的钳位电路之后,将高低电平锁定为5V和0V,然后再进入一个与非门CD4093,对输出信号进行整形,将信号变成高电平为5V,低电平为0V的标准的方波,然后此方波会作为锁相倍频电路的输入信号。

图2过零检测电路原理图

2.2锁相倍频电路

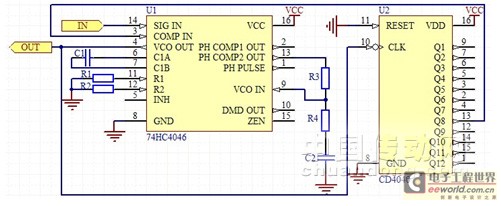

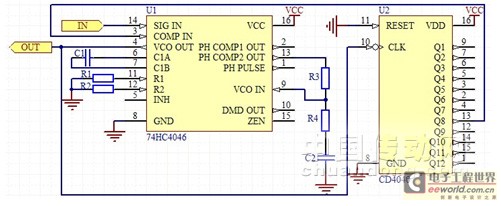

此锁相倍频电路采用了一片锁相环芯片74HC4046、一片累加计数器CD4040和低通滤波器,其电路连接图如图3所示。

图3锁相倍频电路原理图

A相电压经过零信号检测电路后得到与A相电压同步的50Hz方波,作为锁相倍频电路的输入信号进入锁相环芯片74HC4046的14号引脚,4号引脚是74HC4046内部压控振荡器的输出端,其输出信号输入CD4040的10号引脚,进行256倍的倍频,其倍频信号从二进制计数器CD4040的13号引脚输出又进入74HC4046的3号引脚,即比较信号输入端,74HC4046内部的相位比较器对两个信号进行相位比较后,从相位比较器Ⅱ的输出端13号引脚输入,经过由、和组成的低通滤波器,将高频噪声滤除后,再进入74HC4046的内部压控振荡器,作为其控制信号,从上述过程可以看到这是一个闭环控制系统,经过不断的调节,使输出信号频率为输入信号频率的256倍,并且使输入信号与比较信号的频差为零。

3 实验结果及分析

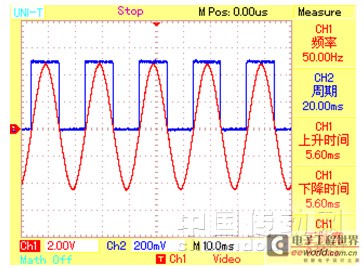

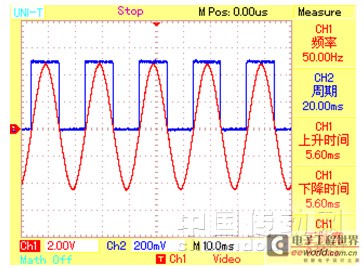

过零检测电路在外加信号频率为50Hz正弦波时的实验波形图如图4所示。

图4过零信号与正弦波形

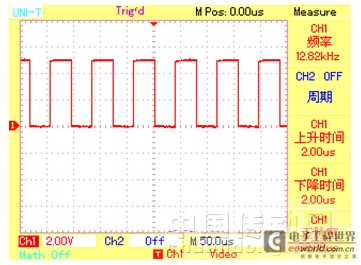

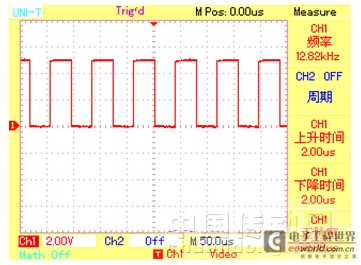

图5所示为所设计的锁相倍频电路的输出实验波形。

图5锁相倍频电路输出的12.82kHz方波

压控振荡器的输入电压来自于低通滤波器的输出,所以输出频率会有一定的波动,此锁相倍频电路的输出频率范围在12.77kHz-12.82kHz。锁相倍频电路输出的频率在被DSP捕捉到后就会启动AD7656对信号采样,由于输出频率的脉动,采样点的正弦和余弦值可能会与表中存储的正弦和余弦表有一定误差。在满足锁相速度的前提下,应当尽可能减小低通滤波器的截止频率,以减小输出频率的波动。

1 锁相倍频电路的原理

锁相倍频电路能否实时稳定的输出12.8kHz的方波,是整个检测模块在开机后能否在最短时间内开始工作的关键。图1所示为锁相倍频电路的原理框图。

图1锁相倍频电路的原理框图

由图1可以看出,锁相倍频电路是一个闭环频率反馈系统,它主要由鉴相器、低通滤波器、压控振荡器和累加计数器构成。

鉴相器是使输出电压与两个输入信号之间的相位差有确定关系的电路,它是锁相环PLL(PhaseLockedLoop)的基本部件之一,鉴相器可以分为模拟鉴相器和数字鉴相器两种。

鉴相器的输出信号包含很多的谐波分量,当锁相环处于锁定状态时,这些分量的第一项为“直流”分量,其它频率的分量为不需要的信号,而且在锁相倍频电路的信号传递中,也会有高频噪声对信号产生干扰,这些较高频率的分量也是不需要的信号,所以要用低通滤波器将其滤除。在此设计中,采用一阶低通滤波器。

压控振荡器是输出频率与输入电压有对应关系的振荡电路VCO(Voltage-controlledOscillator),在自动频率控制环路和锁相环环路中,输入控制电压是误差信号电压,压控振荡器是环路中的一个受控部件。

在APF的检测系统中,锁相倍频电路的输出作为启动AD采样的信号,分频器将VCO产生的输出信号频率除以N,这个因子多数情况下可变或可编程控制,分频器通常由触发器(如RS触发器、JK触发器或是T触发器)级联而成,一个JK触发器可以将加到它的时钟输入端信号2分频,两个就是4分频等。

在此电路中,使用了二进制加法计数器CD4040,即其累加数均为2的倍数,如要得到256倍,即把输出信号从其Q8脚输出。

2锁相倍频电路的设计

2.1过零检测电路

过零检测电路原理图如图2所示。电路中采用宇波CHV-25P霍尔电压传感器,此霍尔电压传感器的额定电流为10mA,原边与副边匝数比为2500:1000,所以在将A相电网电压接入霍尔电压传感器前,需要通过一个限流电阻进行限流,以免电流过大将霍尔电压传感器烧坏,它的M端为副边电流输出端,需要加一支采样电阻,将电阻上的压降引入一个由运算放大器CA3140及四个电阻组成的滞回比较器,然后在其输出端通过一个由两个二极管组成的钳位电路之后,将高低电平锁定为5V和0V,然后再进入一个与非门CD4093,对输出信号进行整形,将信号变成高电平为5V,低电平为0V的标准的方波,然后此方波会作为锁相倍频电路的输入信号。

图2过零检测电路原理图

2.2锁相倍频电路

此锁相倍频电路采用了一片锁相环芯片74HC4046、一片累加计数器CD4040和低通滤波器,其电路连接图如图3所示。

图3锁相倍频电路原理图

A相电压经过零信号检测电路后得到与A相电压同步的50Hz方波,作为锁相倍频电路的输入信号进入锁相环芯片74HC4046的14号引脚,4号引脚是74HC4046内部压控振荡器的输出端,其输出信号输入CD4040的10号引脚,进行256倍的倍频,其倍频信号从二进制计数器CD4040的13号引脚输出又进入74HC4046的3号引脚,即比较信号输入端,74HC4046内部的相位比较器对两个信号进行相位比较后,从相位比较器Ⅱ的输出端13号引脚输入,经过由、和组成的低通滤波器,将高频噪声滤除后,再进入74HC4046的内部压控振荡器,作为其控制信号,从上述过程可以看到这是一个闭环控制系统,经过不断的调节,使输出信号频率为输入信号频率的256倍,并且使输入信号与比较信号的频差为零。

3 实验结果及分析

过零检测电路在外加信号频率为50Hz正弦波时的实验波形图如图4所示。

图4过零信号与正弦波形

图5所示为所设计的锁相倍频电路的输出实验波形。

图5锁相倍频电路输出的12.82kHz方波

压控振荡器的输入电压来自于低通滤波器的输出,所以输出频率会有一定的波动,此锁相倍频电路的输出频率范围在12.77kHz-12.82kHz。锁相倍频电路输出的频率在被DSP捕捉到后就会启动AD7656对信号采样,由于输出频率的脉动,采样点的正弦和余弦值可能会与表中存储的正弦和余弦表有一定误差。在满足锁相速度的前提下,应当尽可能减小低通滤波器的截止频率,以减小输出频率的波动。

滤波器 电力电子 电路 DSP 低通滤波器 振荡器 电压 传感器 电流 电阻 放大器 比较器 二极管 相关文章:

- 无需调谐的“砖墙式”低通音频滤波器(11-20)

- 视频有源滤波器 (11-26)

- 通用和低噪声的有源滤波器提供达10MHz的可重复性能(01-05)

- 直流耦合视频放大器/滤波器的视频信号电平转换(07-03)

- 开关电容梳状滤波器幅频特性的深入分析(06-05)

- 在高温超导滤波器后级的低温低噪声放大器的设计和调试方法(06-01)