MXB7846型4线触摸屏数据转换器的原理及应用

时间:10-25

来源:互联网

点击:

1 概述

随着家用电子设备和智能仪器的广泛应用,人们对其人机接口的要求越来越高,人性化的人机接口能大大提高人们的操作水平,更好地发挥装置性能。触摸屏因此而被大量应用于家用电子、检测仪器、通讯设备等装置的人机接口部分。

MXB7846是Maxim公司的一款集成了%26;#177;15kV ESD保护的4线工业标准触摸屏数据转换器,广泛应用于电阻式触摸屏输入系统中。它集成了一个12位的同步采样模数转换器,可以采用内部集成的+2.5V参考电源,也可以采用外接参考电源。还集成了片上温度传感器、电源监测通道和辅助AD转换器。电路的所有模拟输入通道都处于ESD保护之中,因此使用时不需要额外的静电保护装置。

2 引脚排列及引脚功能

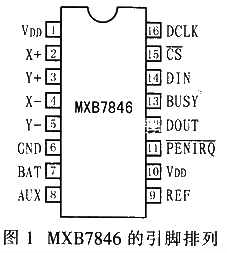

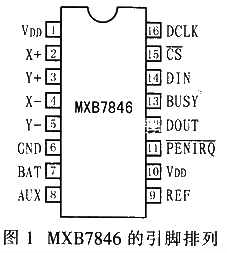

MXB7846采用16脚QSOP和TSSOP封装。其引脚排列如图1所示,各引脚功能如下所述。

VDD:电源输入,电压范围为+2.375V~+5.25V。采用内部参考电源时,参考电源大小由此引脚决定。工作时采用1μF电容器旁路滤波。

GND:地。

X+、X-、Y+、Y-:横纵坐标输入,其中X+、Y+为ADC输入的第1、2通道。

BAT:电源监测输入端,为ADC的第3通道。

AUX:辅助模拟输入端,为ADC的第4通道。

REF:参考电压输入/输出通道,为AD转换提供参考电压。当采用内部参考电源时,该引脚提供2.5V的参考电压输出;采用外部参考电源时,参考电压由此输入,可输入1V~VDD的电压。工作时采用0.1μF电容器旁路滤波。

PENIRQ:触摸中断引脚,工作时通过10kΩ~100kΩ电阻器上拉。触摸屏被触摸时引起中断,ADC开始转换。

DIN:串行数据输入,DCLK的上升沿读入数据。

DOUT:串行数据输出,DCLK的下降沿输出数据,CS为高时,DOUT为高阻状态。

BUSY:忙输出标志,在数据转换时持续一个时钟周期的高状态,CS为高时,BUSY为高阻状态。

CS:片选信号,只有当CS为低时,串行数据才可以从DIN读入。

DCLK:时钟信号输入,输入时钟信号决定电路的转换速度,其占空比必须为40%~60%。

3 工作原理

MXB7846采用逐次逼近型技术来实现模拟信号到12位数字信号的转换。其内部结构如图2所示。当电路工作于单输入模式时,ADC将REF做为参考输入;电路工作于差分输入模式时,ADC的REF+连接到X+或Y+,REF-连接到X-或Y-。具体的连续方式如表1所示。

表1 MXB7846控制字格式

BIT7

BIT6

BIT5

NIT4

START

A2

A1

A0

BIT3

BIT2

BIT1

BIT0

MODE

SER/DFR

PD1

PD0

MXB7846的控制字格式如表1所列,其中START为数据传输起始标志位,该位必为“1”。A2-A0进行通道选择(见表2)。MODE用来选择AD转换的精度,“1”表示8位“0”表示12位。SER/DFR选择参考电压的输入模式,“1”为单输入模式,“0”为差分输入模式。PD1、PD0选择省电模式:“00”表示省电模式允许,在二次A/D转换之间掉电,且中断允许;“01”同“00”,只是不允许中断;“10”为保留;“11”表示禁止省电模式。

表2 MXB7846的控制及工作方式

A2

A1

A0

测量值

ADC输入

ADC连接

0

0

0

Temp0

Temp0

-

0

0

1

Y坐标

X+

Y+、Y-

0

1

0

BAT

BAT

-

1

0

1

X坐标

Y+

X+、X-

1

1

0

AUX

AUX

-

1

1

1

Temp1

Temp1

-

4 典型应用

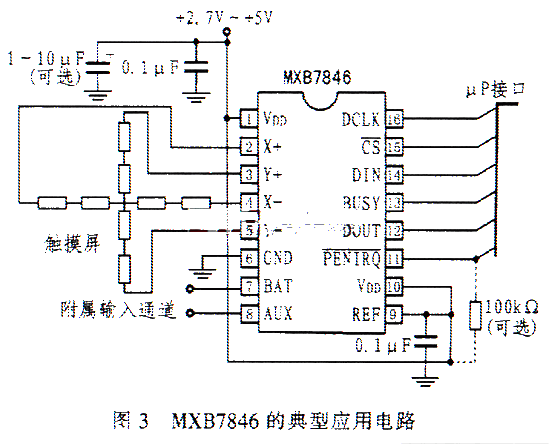

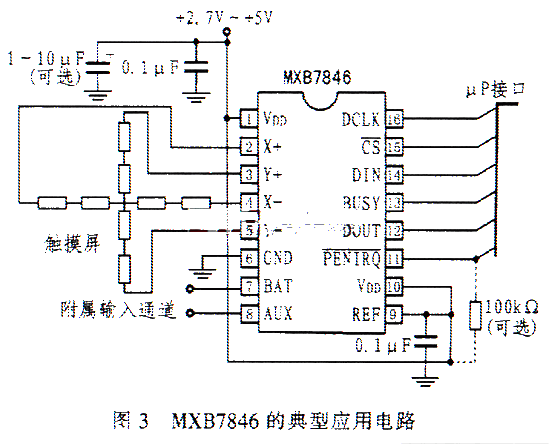

MXB7846用于控制电阻式触摸屏的典型电路原理如图3所示。

触摸屏工作时,上下导体层相当于电阻网络,如图3所示。当某一层电极加上电压时,会在该网络上形成电压梯度。如有外力使得上下两层在某一点接触,则在电极未加电压的另一层可以测得接触点处的电压,从而知道触点处的坐标。比如,在顶层的电极(X+,Y-)上加电压,则会在顶层导体导上形成电压梯度,当有外力使得上下两层在某一点接触,就可以在底层测得接触点处的电压,再根据该电压与电极(X+)之间的距离关系算出该处的X坐标。然后,将电压切换到底层电极(Y+,Y-)上,并在顶层测量接触点处的电压,从而知道Y坐标。

为了完成一次电极电压切换和A/D转换,首先应通过串口向MXB7846发送控制字,转换完成后再通过串口读出电压转换值。标准的一次转换需要24个时钟周期。由于串口支持双向同时传送,并且在一次读数与下一次发控制字之间可以重叠,所以转换速率可以提高到每次16个时钟周期。如果条件允许,即CPU可以产生15个时钟周期(比如FPGAs和ASICs),转换速率还可以提高到每次15个时钟周期,其转换时序如图4所示。

本文采用Altera公司的EPM7128LC84-6型CPLD生产MXB7846所需的控制逻辑,以使其工作在较高的转换效率。用Verilog语言编制的控制程序如下:

module max(DATAIN,CLK,DOUT,BUSY,CS,DCLK,DIN,DATAOUT,FLAG);

input [7:0]DATAIN;

input BUSY,CLK,DOUT;

output[11:0]DATAOUT;

output CS,DCLK,DIN,FLAG;

reg [11:0]DATAOUT;

reg [11:0]yiwei;

reg [5:0]count;

reg [4:0]jishu;

reg shizhong,CS,DCLK,DIN,FLAG;

always @(negedge CLK)

begin

count=count+1;

if(count==6"d2)

begin

shizhong=~shizhong;

count=0;

end

end

always@(negedge shizhong)

begin

if (DATAIN==8"hff)

CS=1;

Else

Begin

CS=0;

jishu=jishu+1;

DCLK=~DCLK;

if(jishu==30)

jishu=0;

case(jishu)

5"b00000:begin DIN=DATAIN ;yiwei =DOUT;end

5"b00010:begin DIN=DATAIN ; yiwei =DOUT;end

5"b00100:begin DIN=DATAIN ; yiwei =DOUT;end

5"b01000:begin DIN=DATAIN ;yiwei [11]=DOUT;DATAOUT=yiwei;FLAG=1;end

5"b01010:begin DIN=DATAIN;FLAG=0;end

5"b01100:DIN=DATAIN;

5"b01110:DIN=DATAIN[0];

5"b10000:if(BUSY==0)yiwei[0]=DOUT;

5"b10010:yiwei=DOUT;

5"b10100:yiwei=DOUT;

5"b10110:yiwei=DOUT;

5"b11000:yiwei=DOUT;

5"b11010:yiwei=DOUT;

5"b11100:yiwei=DOUT;

endcase

end

end

endmodule

本程序为CPLD模块中MXB7846的控制模块,其主要作用是通过CPLD时钟进行分频(分频数可设定)生产MXB7846的时钟,以及通过DATAIN给定MXB7846的控制字。其CS、DOUT、DCLK、DIN、BUSY分别与MXB7846的对应管脚相连以对其进行控制。当MXB7846完成一次转换后,CPLD读取其中的串行数据并转化为并行数据,待FLAG为高以后就可以从DATAOUT读取数据了。

5 结束语

MXB7846易于与目前各种常用的CPU接口,其低功耗特性使得非常适用于电源供电的系统,在个人掌上电脑、手机、医用仪器、测量仪表等各种便携式装置中具有广阔的应用前景。

随着家用电子设备和智能仪器的广泛应用,人们对其人机接口的要求越来越高,人性化的人机接口能大大提高人们的操作水平,更好地发挥装置性能。触摸屏因此而被大量应用于家用电子、检测仪器、通讯设备等装置的人机接口部分。

MXB7846是Maxim公司的一款集成了%26;#177;15kV ESD保护的4线工业标准触摸屏数据转换器,广泛应用于电阻式触摸屏输入系统中。它集成了一个12位的同步采样模数转换器,可以采用内部集成的+2.5V参考电源,也可以采用外接参考电源。还集成了片上温度传感器、电源监测通道和辅助AD转换器。电路的所有模拟输入通道都处于ESD保护之中,因此使用时不需要额外的静电保护装置。

2 引脚排列及引脚功能

MXB7846采用16脚QSOP和TSSOP封装。其引脚排列如图1所示,各引脚功能如下所述。

VDD:电源输入,电压范围为+2.375V~+5.25V。采用内部参考电源时,参考电源大小由此引脚决定。工作时采用1μF电容器旁路滤波。

GND:地。

X+、X-、Y+、Y-:横纵坐标输入,其中X+、Y+为ADC输入的第1、2通道。

BAT:电源监测输入端,为ADC的第3通道。

AUX:辅助模拟输入端,为ADC的第4通道。

REF:参考电压输入/输出通道,为AD转换提供参考电压。当采用内部参考电源时,该引脚提供2.5V的参考电压输出;采用外部参考电源时,参考电压由此输入,可输入1V~VDD的电压。工作时采用0.1μF电容器旁路滤波。

PENIRQ:触摸中断引脚,工作时通过10kΩ~100kΩ电阻器上拉。触摸屏被触摸时引起中断,ADC开始转换。

DIN:串行数据输入,DCLK的上升沿读入数据。

DOUT:串行数据输出,DCLK的下降沿输出数据,CS为高时,DOUT为高阻状态。

BUSY:忙输出标志,在数据转换时持续一个时钟周期的高状态,CS为高时,BUSY为高阻状态。

CS:片选信号,只有当CS为低时,串行数据才可以从DIN读入。

DCLK:时钟信号输入,输入时钟信号决定电路的转换速度,其占空比必须为40%~60%。

3 工作原理

MXB7846采用逐次逼近型技术来实现模拟信号到12位数字信号的转换。其内部结构如图2所示。当电路工作于单输入模式时,ADC将REF做为参考输入;电路工作于差分输入模式时,ADC的REF+连接到X+或Y+,REF-连接到X-或Y-。具体的连续方式如表1所示。

表1 MXB7846控制字格式

BIT7

BIT6

BIT5

NIT4

START

A2

A1

A0

BIT3

BIT2

BIT1

BIT0

MODE

SER/DFR

PD1

PD0

MXB7846的控制字格式如表1所列,其中START为数据传输起始标志位,该位必为“1”。A2-A0进行通道选择(见表2)。MODE用来选择AD转换的精度,“1”表示8位“0”表示12位。SER/DFR选择参考电压的输入模式,“1”为单输入模式,“0”为差分输入模式。PD1、PD0选择省电模式:“00”表示省电模式允许,在二次A/D转换之间掉电,且中断允许;“01”同“00”,只是不允许中断;“10”为保留;“11”表示禁止省电模式。

表2 MXB7846的控制及工作方式

A2

A1

A0

测量值

ADC输入

ADC连接

0

0

0

Temp0

Temp0

-

0

0

1

Y坐标

X+

Y+、Y-

0

1

0

BAT

BAT

-

1

0

1

X坐标

Y+

X+、X-

1

1

0

AUX

AUX

-

1

1

1

Temp1

Temp1

-

4 典型应用

MXB7846用于控制电阻式触摸屏的典型电路原理如图3所示。

触摸屏工作时,上下导体层相当于电阻网络,如图3所示。当某一层电极加上电压时,会在该网络上形成电压梯度。如有外力使得上下两层在某一点接触,则在电极未加电压的另一层可以测得接触点处的电压,从而知道触点处的坐标。比如,在顶层的电极(X+,Y-)上加电压,则会在顶层导体导上形成电压梯度,当有外力使得上下两层在某一点接触,就可以在底层测得接触点处的电压,再根据该电压与电极(X+)之间的距离关系算出该处的X坐标。然后,将电压切换到底层电极(Y+,Y-)上,并在顶层测量接触点处的电压,从而知道Y坐标。

为了完成一次电极电压切换和A/D转换,首先应通过串口向MXB7846发送控制字,转换完成后再通过串口读出电压转换值。标准的一次转换需要24个时钟周期。由于串口支持双向同时传送,并且在一次读数与下一次发控制字之间可以重叠,所以转换速率可以提高到每次16个时钟周期。如果条件允许,即CPU可以产生15个时钟周期(比如FPGAs和ASICs),转换速率还可以提高到每次15个时钟周期,其转换时序如图4所示。

本文采用Altera公司的EPM7128LC84-6型CPLD生产MXB7846所需的控制逻辑,以使其工作在较高的转换效率。用Verilog语言编制的控制程序如下:

module max(DATAIN,CLK,DOUT,BUSY,CS,DCLK,DIN,DATAOUT,FLAG);

input [7:0]DATAIN;

input BUSY,CLK,DOUT;

output[11:0]DATAOUT;

output CS,DCLK,DIN,FLAG;

reg [11:0]DATAOUT;

reg [11:0]yiwei;

reg [5:0]count;

reg [4:0]jishu;

reg shizhong,CS,DCLK,DIN,FLAG;

always @(negedge CLK)

begin

count=count+1;

if(count==6"d2)

begin

shizhong=~shizhong;

count=0;

end

end

always@(negedge shizhong)

begin

if (DATAIN==8"hff)

CS=1;

Else

Begin

CS=0;

jishu=jishu+1;

DCLK=~DCLK;

if(jishu==30)

jishu=0;

case(jishu)

5"b00000:begin DIN=DATAIN ;yiwei =DOUT;end

5"b00010:begin DIN=DATAIN ; yiwei =DOUT;end

5"b00100:begin DIN=DATAIN ; yiwei =DOUT;end

5"b01000:begin DIN=DATAIN ;yiwei [11]=DOUT;DATAOUT=yiwei;FLAG=1;end

5"b01010:begin DIN=DATAIN;FLAG=0;end

5"b01100:DIN=DATAIN;

5"b01110:DIN=DATAIN[0];

5"b10000:if(BUSY==0)yiwei[0]=DOUT;

5"b10010:yiwei=DOUT;

5"b10100:yiwei=DOUT;

5"b10110:yiwei=DOUT;

5"b11000:yiwei=DOUT;

5"b11010:yiwei=DOUT;

5"b11100:yiwei=DOUT;

endcase

end

end

endmodule

本程序为CPLD模块中MXB7846的控制模块,其主要作用是通过CPLD时钟进行分频(分频数可设定)生产MXB7846的时钟,以及通过DATAIN给定MXB7846的控制字。其CS、DOUT、DCLK、DIN、BUSY分别与MXB7846的对应管脚相连以对其进行控制。当MXB7846完成一次转换后,CPLD读取其中的串行数据并转化为并行数据,待FLAG为高以后就可以从DATAOUT读取数据了。

5 结束语

MXB7846易于与目前各种常用的CPU接口,其低功耗特性使得非常适用于电源供电的系统,在个人掌上电脑、手机、医用仪器、测量仪表等各种便携式装置中具有广阔的应用前景。