12b双通道高速A/D转换器AD9238的原理及应用

时间:09-13

来源:互联网

点击:

3.4 工作时序

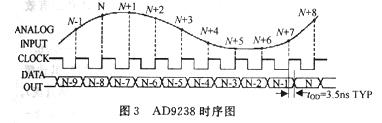

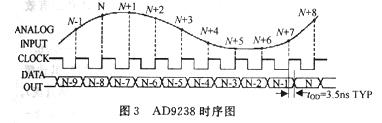

AD9238的数据输出会有7个时钟周期的流水线延迟,如图3所示。开始采样后前7个数据是无用的,应该在后端数字信号处理时舍弃掉。

AD9238两个通道的12 b数字信号输出(D0_A-D11_A和D0_B-D11_B)是独立的。一般情况下,他们各自独立的输出转换结果。当把AD9238两个通道的时钟输入CLK_A,CLK_B和管脚MUX_SELECT连接在一起时,系统处于单通道输出工作状态。此时当时钟上升沿到来时,转换数据分别送给各自对应的通道;当时钟下降沿到来时,转换数据分别送给相反的通道。这样在一个时钟周期内,数据结果可以从一个通道输出,另外一个不用的输出通道可以通过管脚OEB_A(或OEB_B)关闭掉。可以看到,这时数据率是采样率的2倍。

3.5 数字输出数据格式

AD8138输出数据为TTL/CMOS兼容电平(可以设置成2.5V或者3.3V),通过设置DFS可以使AD8138输出数据格式为偏移二进制码(DFS接AGND)或者是二进制补码(DFS接AVDD)。

另外,管脚OTR_A和OTR_B为溢出标志位,当某个通道的输入模拟信号幅度超出范围,对应通道的溢出标志位会输出高电平。

3.6 电压参考

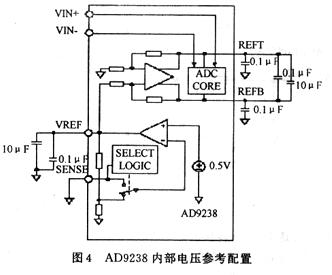

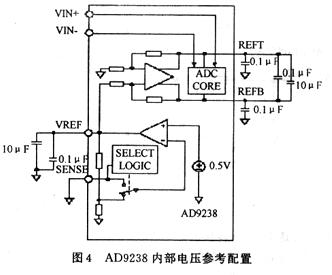

AD8238内部有一个稳定精确的0.5 V电压参考。调整AD9238的参考电压可以改变输入信号范围,调整的方法有2种:内部参考和外部参考。输入范围根据参考电压的改变做线性变化。当把SENSE(第9脚)接地时,VREF 被设置成1 V,此时器件采用内部参考,输入信号范围为2Vp-p。有关管脚的接法如图4所示。

当把SENSE(第9脚)直接与VREF管脚连接时,输入信号范围为1Vp-p当在SENSE管脚、VREF管脚和模拟地三者之间串接2个电阻R1和R2时,输入信号范围为可改变的,即VREF=0.5×(1+R2/R1)。上述两种情况都属于内部电压参考。

当把SENSE管脚接到AVDD时,内部参考无效,采用外部电压参考。这种情况使用不多,不再做详细介绍。

在设置电压参考时,主要是改变SENSE管脚的接法,REFT和REFB管脚的接法如图4所示。值得注意的是,AD8238对每个通道都提供了电压参考,如果采用共享电压参考模式可以取得较好的性能。此时需要把SHARED_REF管脚(第62脚)接高电平,2个通道的REFT和REFB管脚互相连接(即REFT_A接REFT_B,REFB_A接REFB_B),他们各自的去耦和隔离电容接法仍同图4所示。

4 AD9238设计实例

AD9238在通信接收机的射频采样中有很好的应用,现介绍一个在通信I/Q两路数据采集中的具体设计实例。

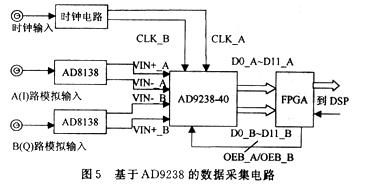

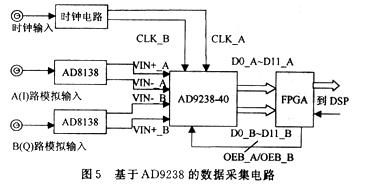

如图5所示,该数据采集电路由时钟电路、运放驱动电路、A/D转换电路、FPGA电路组成。FPGA主要完成和DSP芯片之间数据的缓冲、转换及传递,利用握手信号实现异步通信。该电路工作在2Vp-p差分工作模式,采用内部电压参考,最高采样频率可达40 MS/s。下面主要对运放驱动电路和A/D转换电路做详细的介绍。

4.1 运放驱动电路

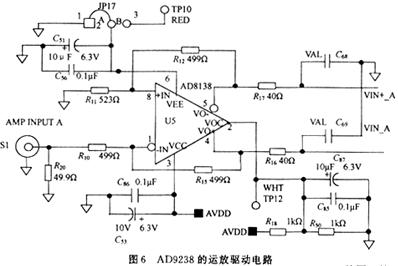

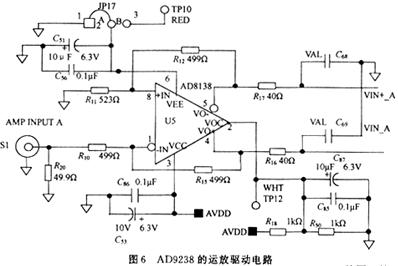

AD9238两个通道分别采用一个AD8138做为运放驱动芯片。I/Q两路中频模拟信号分别经过2个AD8138变为差分信号送给A/D转换器(第2,3,14,15管脚)。图6给出了其中一路的具体电路图,另一路与此基本相同。

4.2 A/D转换电路

该部分电路是整个数据采集电路的核心,下面仅就原理图设计的有关重要管脚进行说明,PCB设计不做详细讨论。

4.2.1 输入信号

包括模拟输入(管脚2,3,14,15)和时钟输入(管脚18,63),其中时钟输入由外部供给可调的时钟,经过反 相器后送给A/D转换器。

另外还有2个通道的输出使能(管脚22,59),由FPGA提供,低电平有效,可以根据通信系统需要控制A/D转换器实时的开始或者停止采样。

4.2.2 电压参考

包括的主要管脚是第6,7,8,9,10,11,62个管脚,在3.6中已经对这些管脚的接法做了详细的讨论。该数据采集电路板采用2 VP-P差分工作模式,使用内部电压参考,两通道工作在共享电压参考模式。

4.2.3 电源和地

AD9238有4组模拟电源和模拟地管脚(第5,12,17,64为AVDD,第1,4,13,16为AGND)、3组数字电源和数字地管脚(第29,49,52为DRVDD,第28,40,53为DRGND),他们的具体接法见3.3说明。值得注意的是,在进行PCB设计时,电路的模拟部分(模拟电源、模拟地等)和数字部分(数字电源、数字地等)应该分开布局,然后把模拟地和数字地单点连接。

4.2.4 输出信号

转换后得到12位I/Q两路的数字信号(D0_A-D11_A和D0_B-D11_B)分为2个通道输出给FPGA。溢出标志(OTR_A和OTR_B)为高电平有效,可外接一发光二级管做为电路溢出指示灯。

4.3 电路测试方法

在电路板设计制作完成后要对其进行测试,图7为该数据采集板的测试连接图。

采用任意波形发生器产生时钟信号和模拟信号(2个通道共用)提供给试验板,这样可以方便地对不同频率和幅度的信号进行调试;稳压电源分别给电路板提供模拟电源和数字电源;逻辑分析仪在读时钟驱动下读取采集到的两路12 b数字信号,导出后可在电脑上进行分析计算。

AD9238的数据输出会有7个时钟周期的流水线延迟,如图3所示。开始采样后前7个数据是无用的,应该在后端数字信号处理时舍弃掉。

AD9238两个通道的12 b数字信号输出(D0_A-D11_A和D0_B-D11_B)是独立的。一般情况下,他们各自独立的输出转换结果。当把AD9238两个通道的时钟输入CLK_A,CLK_B和管脚MUX_SELECT连接在一起时,系统处于单通道输出工作状态。此时当时钟上升沿到来时,转换数据分别送给各自对应的通道;当时钟下降沿到来时,转换数据分别送给相反的通道。这样在一个时钟周期内,数据结果可以从一个通道输出,另外一个不用的输出通道可以通过管脚OEB_A(或OEB_B)关闭掉。可以看到,这时数据率是采样率的2倍。

3.5 数字输出数据格式

AD8138输出数据为TTL/CMOS兼容电平(可以设置成2.5V或者3.3V),通过设置DFS可以使AD8138输出数据格式为偏移二进制码(DFS接AGND)或者是二进制补码(DFS接AVDD)。

另外,管脚OTR_A和OTR_B为溢出标志位,当某个通道的输入模拟信号幅度超出范围,对应通道的溢出标志位会输出高电平。

3.6 电压参考

AD8238内部有一个稳定精确的0.5 V电压参考。调整AD9238的参考电压可以改变输入信号范围,调整的方法有2种:内部参考和外部参考。输入范围根据参考电压的改变做线性变化。当把SENSE(第9脚)接地时,VREF 被设置成1 V,此时器件采用内部参考,输入信号范围为2Vp-p。有关管脚的接法如图4所示。

当把SENSE(第9脚)直接与VREF管脚连接时,输入信号范围为1Vp-p当在SENSE管脚、VREF管脚和模拟地三者之间串接2个电阻R1和R2时,输入信号范围为可改变的,即VREF=0.5×(1+R2/R1)。上述两种情况都属于内部电压参考。

当把SENSE管脚接到AVDD时,内部参考无效,采用外部电压参考。这种情况使用不多,不再做详细介绍。

在设置电压参考时,主要是改变SENSE管脚的接法,REFT和REFB管脚的接法如图4所示。值得注意的是,AD8238对每个通道都提供了电压参考,如果采用共享电压参考模式可以取得较好的性能。此时需要把SHARED_REF管脚(第62脚)接高电平,2个通道的REFT和REFB管脚互相连接(即REFT_A接REFT_B,REFB_A接REFB_B),他们各自的去耦和隔离电容接法仍同图4所示。

4 AD9238设计实例

AD9238在通信接收机的射频采样中有很好的应用,现介绍一个在通信I/Q两路数据采集中的具体设计实例。

如图5所示,该数据采集电路由时钟电路、运放驱动电路、A/D转换电路、FPGA电路组成。FPGA主要完成和DSP芯片之间数据的缓冲、转换及传递,利用握手信号实现异步通信。该电路工作在2Vp-p差分工作模式,采用内部电压参考,最高采样频率可达40 MS/s。下面主要对运放驱动电路和A/D转换电路做详细的介绍。

4.1 运放驱动电路

AD9238两个通道分别采用一个AD8138做为运放驱动芯片。I/Q两路中频模拟信号分别经过2个AD8138变为差分信号送给A/D转换器(第2,3,14,15管脚)。图6给出了其中一路的具体电路图,另一路与此基本相同。

4.2 A/D转换电路

该部分电路是整个数据采集电路的核心,下面仅就原理图设计的有关重要管脚进行说明,PCB设计不做详细讨论。

4.2.1 输入信号

包括模拟输入(管脚2,3,14,15)和时钟输入(管脚18,63),其中时钟输入由外部供给可调的时钟,经过反 相器后送给A/D转换器。

另外还有2个通道的输出使能(管脚22,59),由FPGA提供,低电平有效,可以根据通信系统需要控制A/D转换器实时的开始或者停止采样。

4.2.2 电压参考

包括的主要管脚是第6,7,8,9,10,11,62个管脚,在3.6中已经对这些管脚的接法做了详细的讨论。该数据采集电路板采用2 VP-P差分工作模式,使用内部电压参考,两通道工作在共享电压参考模式。

4.2.3 电源和地

AD9238有4组模拟电源和模拟地管脚(第5,12,17,64为AVDD,第1,4,13,16为AGND)、3组数字电源和数字地管脚(第29,49,52为DRVDD,第28,40,53为DRGND),他们的具体接法见3.3说明。值得注意的是,在进行PCB设计时,电路的模拟部分(模拟电源、模拟地等)和数字部分(数字电源、数字地等)应该分开布局,然后把模拟地和数字地单点连接。

4.2.4 输出信号

转换后得到12位I/Q两路的数字信号(D0_A-D11_A和D0_B-D11_B)分为2个通道输出给FPGA。溢出标志(OTR_A和OTR_B)为高电平有效,可外接一发光二级管做为电路溢出指示灯。

4.3 电路测试方法

在电路板设计制作完成后要对其进行测试,图7为该数据采集板的测试连接图。

采用任意波形发生器产生时钟信号和模拟信号(2个通道共用)提供给试验板,这样可以方便地对不同频率和幅度的信号进行调试;稳压电源分别给电路板提供模拟电源和数字电源;逻辑分析仪在读时钟驱动下读取采集到的两路12 b数字信号,导出后可在电脑上进行分析计算。

ADI 放大器 电压 电路 ADC DAC 电容 电阻 电流 滤波器 CMOS 射频 FPGA DSP 电路图 PCB 稳压电源 相关文章:

- 如何使低功耗放大器在便携式产品中提高性能(10-03)

- D类放大器原理详解及应用设计指南(三)(03-16)

- ADMC331在全数字化逆变电源中的应用(06-20)

- 雷达天线电源故障检测电路的设计(01-27)

- ADISl6300四自由度IMU在姿态测量中的应用(08-18)

- 高性能模拟器件兼顾医疗设备诊断级精度和便携化需求(04-26)