16位∑-Δ模数转换器AD7705及其校准

时间:06-10

来源:互联网

点击:

1 AD7705简介

AD7705是AD公司推出的16位∑-Δ(电荷平衡式)A/D转换器。他包括由缓冲器和增益可编程放大器(PGA)组成的前端模拟调节电路、∑-Δ调制器及可编程数字滤波器等,能直接对来自传感器的微弱信号进行A/D转换。此外他还具有高分辨率、宽动态范围、自校准,低功耗及优良的抗噪声性能,因此非常适用于仪表测量和工业控制等领域。

1.1 基本特性

AD7705的基本特性为:16位无丢失代码;0.003%的非线性度;PGA可选择1,2,4,8,16,32,64,128;8种增益;输出数据更新速率可编程;具有自校准和系统校准功能,三线串行接口,可缓冲模拟输入;低功耗。

1.2 引脚功能

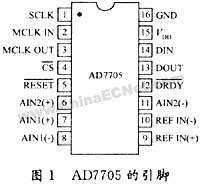

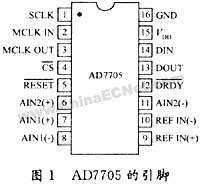

AD7705的引脚排列如图1所示,各引脚的功能说明如下:

SCLK:串行时钟输入。

MCLK IN:主时钟输入。时钟频率为500kHz-5MHz。

MCLK OUT:主时钟输出。

CS反:片选,低电平有效。

RESET反:复位。该端口为低电平时,可以将控制逻辑、接口逻辑、校准系数以及数字滤波器等复位为上电状态;

AIN2(+)、AIN2(-):分别为差分模拟输入通道2的正、负输入端。

AIN1(+)、AIN1(-):分别为差分输入通道1得正、负输入端。

REF IN(+)、REF IN(-):分别为参考电压的正、负端。为了确保元件的正常工作,REF IN(+)端口的输入信号必须大于REF IN(-)端的输入。

DRDY反:逻辑输出。低电平表示可以读取新的数据转换;高电平时不可读取数据。

IDN,DOUT:分别为串行数据输入和输出端。

1.3 片内寄存器

AD7705共有8个片内寄存器,他们是通信寄存器、设置寄存器、时钟寄存器、数据寄存器以及几个测试和校准寄存器。这些寄存器的任何操作都必须先写通信寄存器,然后才能对其他寄存器进行操作。

(1)通信寄存器

通信寄存器是一个8位读/写寄存器,写入通信寄存器的数据决定下一次读/写操作在哪一个寄存器上进行,完成对所选寄存器的读/写操作后,该端口等待下一次写操作,这也是通信寄存器的缺省状态,如果在DIN为高电平时,写操作持续的时间足够长(至少32个串行时钟周期),那么AD7705将返回该缺省状态。

通信寄存器中的RS2,RS1,RS0为寄存器选择位,他们决定对哪一个寄存器进行读/写操作,常用的寄存器主要有通信寄存器(RS2RS1RS0=000)、设置寄存器(RS2RS1RS0=001)、时钟寄存器(RS2RS1RS0=010)以及数据寄存器(RS2RS1RS0=011)。R/W反为读写选择位。该位确定对选定寄存器进行读还是写操作,"0"表示写操作,"1"表示读操作。CH1,CH0为通道选择位,00选择通道1,01选择通道2。

(2)设置寄存器

设置寄存器是一个8位读/写寄存器,其中MD1,MD0为工作模式选择位,MD1MD0=00,01,10,11分别对应正常工作模式,自校准、零标度系统校准以及满标度系统校准。G2,G1,G0为增益选择位,G2G1G0=000-111分别对应1,2,4,8,16,32,64,128八种增益。

(3)时钟寄存器

时钟寄存器是一个8位读/写寄存器。其中CLK为时钟位。如果器件的主时钟频率为2.457 6MHz(CLKdiv=0)或4.915 2MHz(CLKdiv=1),该位置"1",如果主时钟频率为1MHz(CLKdiv=0)或者2MHz(CLKdiv=1),该位置"0",此外CLK还与FS1和FS0共同选择器件的输出更新速率。

(4)数据寄存器

数据寄存器是一个16位只读寄存器,他用来存放AD7705的最新转换结果。这里要注意:当对AD7705进行写操作时,AD7705期望MSB(最高有效位)在前,但微控制器(如8051系列)首先输出LSB(最低有效位),因此必须对数据进行倒序。不过同时还要注意:数据寄存器虽然是一个16位寄存器,但他由2个8位存贮单元组成,因此必须分成2个8位分别进行倒序。进行读操作时同样如此。

(5)测试寄存器

该寄存器主要用于测试,建议用户不要随便对其进行更改。

(6)零标度寄存器

(7)满标度寄存器

2 校准

当环境温度、工作电压、增益或双极/单极输入范围变化时,必须对AD7705进行校准,校准可通过对寄存器的MD1和MD0位编程实现,校准可去除偏置和增益误差。

2.1 自校准

对于所选通道,无论使用何种校准模式,ADC的片上微控制器必须记录2个不同模拟输入状态的调制器输出,也就是"零标度"和"满标度"点。通过这些转换,微控制器可以计算转换器输入/输出转换函数的增益斜率,元件内部通过33位分辨率决定16位的转换结果。

自校准模式中,ADC决定内部校准点,AD7705在内部短接2个输入端比如AIN(+)=AIN(-)=Vref),以得到用以确定校准系系数的零标度点,只要模拟输入引脚上的信号不超过正常范围,他们就不会影响校准过程。而满标度系数则可以在选定的增益下,通过输入端施加电压Vref来确定。

自校准可以通过写设置寄存器中的MD1和MD0来实现(MD1MD0=01)。在该校准模式中,可以通过DRDY来确定转换何时结束且模拟输入的转换数据可用。校准初始化时DRDY为高电平,直到外部模拟输入的转换结果可用时才变为低电平,校准过程必须考虑PGA的增益。

2.2 系统校准

系统校准通过写设置寄存器中的MD1和MD0来实现,他分2步完成,可补偿系统增益、偏移以及器件内部误差。在选定的增益下,先后在外部给AIN(+)端施加零标度电压和满标度电压,分别校准零标度点(MD1MD0=10)和满标度点(MD1MD0=11)。根据零标度和满标度校准的数据,片内微控制器计算出转换器的输出/输出转换函数的偏移和增益斜率,对误差进行补偿。在单极性模式下,系统校准在转换函数的零标度和满标度之间完成;在双极性模式下,标准在中点电压(零差分电压)和正的满标度电压之间完成。

2.3 现场校准

系统校准作为工厂校准的一部分,实现起来并不困难,然而由于校准过程中必须在2个模拟输入端施加系统零标度和满标度电压,而现场的2种标度电压并不容易确定,因此现场的系统校准实现起来要麻烦得多。这样一来,用户在进行工厂系统校准后,还必须考虑如何消除由现场温度变化所延期的ADC漂移误差。下面就介绍一种解决该问题的方法,他包括工厂校准和现场校准2个部分。

(1)工厂校准

在选定增益和输出更新速率下,进行自校准;

读取并存储校准寄存器内容,令偏移=Z0,增益=G0;

在选定增益和输出更新速率下,进行系统校准;

读取并存储校准寄存器内容,令偏移=ZS,增益=GS,将系统校准系统加载到ADC中,便可在现场使用该系统。

如果环境温度变化,可以遵照以下方法对偏移和增益漂移进行校准。

(2)现场校准

在选定增益和输出更新速率下,进行自校准,这里要注意:增益和输出更新速率必须跟前面的自校准和系统校准保持一致;

读取校准寄存器内容,令偏移=Z1,增益=G1;

计算新的校准系数:ZN=ZS+(Z1-Z0)

GN=ZS×(G1/G0)

将ZN与GN写入校准寄存器。

该方法不仅保留了初始的系统校准,又对系统进行了调整,这样便可消除ADC中由温度漂移引起的误差。不过该方法也只能消除由ADC引起的漂移误差,对于由模拟前端信号链引起的漂移误差则不起作用。

2.4 手动校准

在校准过程中,当输入范围不是正常输入范围时,校准过程中不能通过零标度和满标度电压进行系统校准,这时便可通过认为改变校准系数来解决该问题。下面便介绍如何改变系数,来适应输入范围不是0-Vref(±Vref)时的情况,首先,应该针对适当的增益,输入范围、更新速率以及选择的单/双输入模式,使用自校准程序进行校准。然后根据自校准得到的系数,计算出新的系数。

例如,如果所需电压Vin表述如下:

Vin=A×Vref+B

式中B为偏移电压,A×Vref为输入间距。当短接输入端进入零标度校准,且施加Vref进行满标度校准时,A=1,B=0,当输入范围不是0-Vref(±Vref)时,可以遵照下面的步骤进行处理:首先减去偏移B,这样便可以在模拟输入电压为B时得到0代码,然后通过A×Vref来调整输入范围,这样输入Vin便可得到满标度代码。

手动校准过程大致如下:首先进行自校准,并读取校准系数,定义Z0=零标度系数,F0=满标度系数,接下来便可将Z0和F0代入下面的公式,求出适用于新的输入范围的新系数:

ZN=Z0+(B×220/(SPAN×F0/224))

FN=F0/A

式中,SPAN为正常情况下的满标度电压间距,单极模式下等于Vref/增益,双极模式下等于2×Vref/增益,B为偏移电压(单位:V),A为相对于正常间距的缩放因子,为了确保元件正常工作,A的值必须位于0.8-1.05之间,至此,将ZN和FN写入校准寄存器,器件便可继续进行A/D转换。

下面通过具体的实例进行说明,假如器件使用单极模式,自校准后AD7705的零标度系数为2 165 373,满标度系数为5 416 211,由于使用单极模式,因此用作校准的电压范围为0-Vref,当使用5V电压时,Vref等于2.5V,如果用户所需模拟输入范围为0.2-2.6V,那么,B=0.2,而A=(2.6-0.2)/2.5=0.96,这样便可求出新的标度系数ZN和FN:

ZN=2 165 373×(0.2×220/(2.5×5 416 211/224))=2 425 218

FN=5 416 211/0.96=5 641 886

这里需要说明的是,只有当用户清楚地了解期望输入范围的上、下限以及实际输入间距与正常输入间距之比时,才能使用这种方法。

使用该方法时,如果用户能确保变量A位于0.8-1.05之间,那么AD7705能够满足数据手册中的噪声要求。例如,在单极模式中,当电压为5V,更新速率为50Hz,增益为1时,AD7705的rms噪声为4.1μV,其信号范围为0-2.5V。在上例中,将输入范围改为0.2-2.5V。如果操作条件(更新速率、增益等)不变,那么噪声仍为4.1μV。使用前一输入范围时,取整后的峰-峰分辨率为log(2.5V/6.6×4.1μV)/log 2=16位,而更改后的峰-峰分辨率为log(2.4V/6.6×1.5μV)/log2=16位,他同样也进行了取整。

2.5 校准频度

校准的频繁程度通常由以下几个因素决定:

(1)转换器所需的精度;

(2)漂移特性对ADC性能的影响;

(3)系统的工作温度。

当然还有其他一些因素也会对其产生影响,比如热电偶的影响及增益漂移等。

通常,所需的精度越高,校准就越频繁,进行校准后,高分辨率的转换器将会附带一些偏移与增益漂移误差,比如,AD7705由温度引起的偏移为0.5μV/℃。因此为了提高精度,有时也必须考虑寄生电偶的温度效应以及器件外部的漂移源等。

AD7705是AD公司推出的16位∑-Δ(电荷平衡式)A/D转换器。他包括由缓冲器和增益可编程放大器(PGA)组成的前端模拟调节电路、∑-Δ调制器及可编程数字滤波器等,能直接对来自传感器的微弱信号进行A/D转换。此外他还具有高分辨率、宽动态范围、自校准,低功耗及优良的抗噪声性能,因此非常适用于仪表测量和工业控制等领域。

1.1 基本特性

AD7705的基本特性为:16位无丢失代码;0.003%的非线性度;PGA可选择1,2,4,8,16,32,64,128;8种增益;输出数据更新速率可编程;具有自校准和系统校准功能,三线串行接口,可缓冲模拟输入;低功耗。

1.2 引脚功能

AD7705的引脚排列如图1所示,各引脚的功能说明如下:

SCLK:串行时钟输入。

MCLK IN:主时钟输入。时钟频率为500kHz-5MHz。

MCLK OUT:主时钟输出。

CS反:片选,低电平有效。

RESET反:复位。该端口为低电平时,可以将控制逻辑、接口逻辑、校准系数以及数字滤波器等复位为上电状态;

AIN2(+)、AIN2(-):分别为差分模拟输入通道2的正、负输入端。

AIN1(+)、AIN1(-):分别为差分输入通道1得正、负输入端。

REF IN(+)、REF IN(-):分别为参考电压的正、负端。为了确保元件的正常工作,REF IN(+)端口的输入信号必须大于REF IN(-)端的输入。

DRDY反:逻辑输出。低电平表示可以读取新的数据转换;高电平时不可读取数据。

IDN,DOUT:分别为串行数据输入和输出端。

1.3 片内寄存器

AD7705共有8个片内寄存器,他们是通信寄存器、设置寄存器、时钟寄存器、数据寄存器以及几个测试和校准寄存器。这些寄存器的任何操作都必须先写通信寄存器,然后才能对其他寄存器进行操作。

(1)通信寄存器

通信寄存器是一个8位读/写寄存器,写入通信寄存器的数据决定下一次读/写操作在哪一个寄存器上进行,完成对所选寄存器的读/写操作后,该端口等待下一次写操作,这也是通信寄存器的缺省状态,如果在DIN为高电平时,写操作持续的时间足够长(至少32个串行时钟周期),那么AD7705将返回该缺省状态。

通信寄存器中的RS2,RS1,RS0为寄存器选择位,他们决定对哪一个寄存器进行读/写操作,常用的寄存器主要有通信寄存器(RS2RS1RS0=000)、设置寄存器(RS2RS1RS0=001)、时钟寄存器(RS2RS1RS0=010)以及数据寄存器(RS2RS1RS0=011)。R/W反为读写选择位。该位确定对选定寄存器进行读还是写操作,"0"表示写操作,"1"表示读操作。CH1,CH0为通道选择位,00选择通道1,01选择通道2。

(2)设置寄存器

设置寄存器是一个8位读/写寄存器,其中MD1,MD0为工作模式选择位,MD1MD0=00,01,10,11分别对应正常工作模式,自校准、零标度系统校准以及满标度系统校准。G2,G1,G0为增益选择位,G2G1G0=000-111分别对应1,2,4,8,16,32,64,128八种增益。

(3)时钟寄存器

时钟寄存器是一个8位读/写寄存器。其中CLK为时钟位。如果器件的主时钟频率为2.457 6MHz(CLKdiv=0)或4.915 2MHz(CLKdiv=1),该位置"1",如果主时钟频率为1MHz(CLKdiv=0)或者2MHz(CLKdiv=1),该位置"0",此外CLK还与FS1和FS0共同选择器件的输出更新速率。

(4)数据寄存器

数据寄存器是一个16位只读寄存器,他用来存放AD7705的最新转换结果。这里要注意:当对AD7705进行写操作时,AD7705期望MSB(最高有效位)在前,但微控制器(如8051系列)首先输出LSB(最低有效位),因此必须对数据进行倒序。不过同时还要注意:数据寄存器虽然是一个16位寄存器,但他由2个8位存贮单元组成,因此必须分成2个8位分别进行倒序。进行读操作时同样如此。

(5)测试寄存器

该寄存器主要用于测试,建议用户不要随便对其进行更改。

(6)零标度寄存器

(7)满标度寄存器

2 校准

当环境温度、工作电压、增益或双极/单极输入范围变化时,必须对AD7705进行校准,校准可通过对寄存器的MD1和MD0位编程实现,校准可去除偏置和增益误差。

2.1 自校准

对于所选通道,无论使用何种校准模式,ADC的片上微控制器必须记录2个不同模拟输入状态的调制器输出,也就是"零标度"和"满标度"点。通过这些转换,微控制器可以计算转换器输入/输出转换函数的增益斜率,元件内部通过33位分辨率决定16位的转换结果。

自校准模式中,ADC决定内部校准点,AD7705在内部短接2个输入端比如AIN(+)=AIN(-)=Vref),以得到用以确定校准系系数的零标度点,只要模拟输入引脚上的信号不超过正常范围,他们就不会影响校准过程。而满标度系数则可以在选定的增益下,通过输入端施加电压Vref来确定。

自校准可以通过写设置寄存器中的MD1和MD0来实现(MD1MD0=01)。在该校准模式中,可以通过DRDY来确定转换何时结束且模拟输入的转换数据可用。校准初始化时DRDY为高电平,直到外部模拟输入的转换结果可用时才变为低电平,校准过程必须考虑PGA的增益。

2.2 系统校准

系统校准通过写设置寄存器中的MD1和MD0来实现,他分2步完成,可补偿系统增益、偏移以及器件内部误差。在选定的增益下,先后在外部给AIN(+)端施加零标度电压和满标度电压,分别校准零标度点(MD1MD0=10)和满标度点(MD1MD0=11)。根据零标度和满标度校准的数据,片内微控制器计算出转换器的输出/输出转换函数的偏移和增益斜率,对误差进行补偿。在单极性模式下,系统校准在转换函数的零标度和满标度之间完成;在双极性模式下,标准在中点电压(零差分电压)和正的满标度电压之间完成。

2.3 现场校准

系统校准作为工厂校准的一部分,实现起来并不困难,然而由于校准过程中必须在2个模拟输入端施加系统零标度和满标度电压,而现场的2种标度电压并不容易确定,因此现场的系统校准实现起来要麻烦得多。这样一来,用户在进行工厂系统校准后,还必须考虑如何消除由现场温度变化所延期的ADC漂移误差。下面就介绍一种解决该问题的方法,他包括工厂校准和现场校准2个部分。

(1)工厂校准

在选定增益和输出更新速率下,进行自校准;

读取并存储校准寄存器内容,令偏移=Z0,增益=G0;

在选定增益和输出更新速率下,进行系统校准;

读取并存储校准寄存器内容,令偏移=ZS,增益=GS,将系统校准系统加载到ADC中,便可在现场使用该系统。

如果环境温度变化,可以遵照以下方法对偏移和增益漂移进行校准。

(2)现场校准

在选定增益和输出更新速率下,进行自校准,这里要注意:增益和输出更新速率必须跟前面的自校准和系统校准保持一致;

读取校准寄存器内容,令偏移=Z1,增益=G1;

计算新的校准系数:ZN=ZS+(Z1-Z0)

GN=ZS×(G1/G0)

将ZN与GN写入校准寄存器。

该方法不仅保留了初始的系统校准,又对系统进行了调整,这样便可消除ADC中由温度漂移引起的误差。不过该方法也只能消除由ADC引起的漂移误差,对于由模拟前端信号链引起的漂移误差则不起作用。

2.4 手动校准

在校准过程中,当输入范围不是正常输入范围时,校准过程中不能通过零标度和满标度电压进行系统校准,这时便可通过认为改变校准系数来解决该问题。下面便介绍如何改变系数,来适应输入范围不是0-Vref(±Vref)时的情况,首先,应该针对适当的增益,输入范围、更新速率以及选择的单/双输入模式,使用自校准程序进行校准。然后根据自校准得到的系数,计算出新的系数。

例如,如果所需电压Vin表述如下:

Vin=A×Vref+B

式中B为偏移电压,A×Vref为输入间距。当短接输入端进入零标度校准,且施加Vref进行满标度校准时,A=1,B=0,当输入范围不是0-Vref(±Vref)时,可以遵照下面的步骤进行处理:首先减去偏移B,这样便可以在模拟输入电压为B时得到0代码,然后通过A×Vref来调整输入范围,这样输入Vin便可得到满标度代码。

手动校准过程大致如下:首先进行自校准,并读取校准系数,定义Z0=零标度系数,F0=满标度系数,接下来便可将Z0和F0代入下面的公式,求出适用于新的输入范围的新系数:

ZN=Z0+(B×220/(SPAN×F0/224))

FN=F0/A

式中,SPAN为正常情况下的满标度电压间距,单极模式下等于Vref/增益,双极模式下等于2×Vref/增益,B为偏移电压(单位:V),A为相对于正常间距的缩放因子,为了确保元件正常工作,A的值必须位于0.8-1.05之间,至此,将ZN和FN写入校准寄存器,器件便可继续进行A/D转换。

下面通过具体的实例进行说明,假如器件使用单极模式,自校准后AD7705的零标度系数为2 165 373,满标度系数为5 416 211,由于使用单极模式,因此用作校准的电压范围为0-Vref,当使用5V电压时,Vref等于2.5V,如果用户所需模拟输入范围为0.2-2.6V,那么,B=0.2,而A=(2.6-0.2)/2.5=0.96,这样便可求出新的标度系数ZN和FN:

ZN=2 165 373×(0.2×220/(2.5×5 416 211/224))=2 425 218

FN=5 416 211/0.96=5 641 886

这里需要说明的是,只有当用户清楚地了解期望输入范围的上、下限以及实际输入间距与正常输入间距之比时,才能使用这种方法。

使用该方法时,如果用户能确保变量A位于0.8-1.05之间,那么AD7705能够满足数据手册中的噪声要求。例如,在单极模式中,当电压为5V,更新速率为50Hz,增益为1时,AD7705的rms噪声为4.1μV,其信号范围为0-2.5V。在上例中,将输入范围改为0.2-2.5V。如果操作条件(更新速率、增益等)不变,那么噪声仍为4.1μV。使用前一输入范围时,取整后的峰-峰分辨率为log(2.5V/6.6×4.1μV)/log 2=16位,而更改后的峰-峰分辨率为log(2.4V/6.6×1.5μV)/log2=16位,他同样也进行了取整。

2.5 校准频度

校准的频繁程度通常由以下几个因素决定:

(1)转换器所需的精度;

(2)漂移特性对ADC性能的影响;

(3)系统的工作温度。

当然还有其他一些因素也会对其产生影响,比如热电偶的影响及增益漂移等。

通常,所需的精度越高,校准就越频繁,进行校准后,高分辨率的转换器将会附带一些偏移与增益漂移误差,比如,AD7705由温度引起的偏移为0.5μV/℃。因此为了提高精度,有时也必须考虑寄生电偶的温度效应以及器件外部的漂移源等。

放大器 电路 滤波器 传感器 电压 ADC 模拟前端 相关文章:

- 使用简化电路的高压放大器(11-21)

- 无需调谐的“砖墙式”低通音频滤波器(11-20)

- 对数放大器的技术指标(11-26)

- 一种增大放大器增益的方法(11-28)

- 对数放大器的典型应用 (11-26)

- AGC中频放大器的设计 (11-29)