DPGA用负时间常数调整信号

时间:08-04

来源:互联网

点击:

DPGA(数字编程增益放大器)用于模拟信号的放大或衰减,实现一个ADC动态范围的最大化。大多数单片DPGA(如凌特技术公司的LTC6910和美国国家半导体公司的LPM8100)都在运放的反馈回路中使用一个乘法DAC,这样用DAC的输入码设定放大器的闭环增益。除了使用单片DPGA,还可以用两支运算放大器和三个模拟开关,建立一个有负时间常数的DPGA。

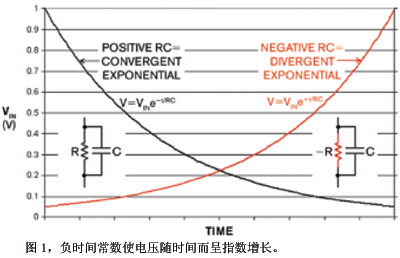

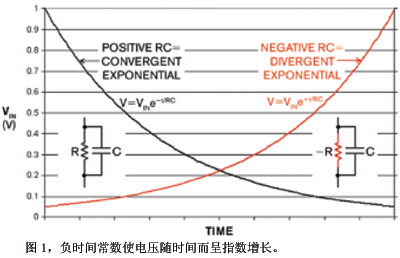

显然大家都很熟悉e–t/RC会聚指数,RC电路中的一只电容会渐近地放电至零。对于输入电压,在t=T=loge(2)RC时 V=VIN/2,t=2T时V=VIN/4,t=3T时V=VIN/8,等等。当用一个合成负电阻的有源电路代替同一个RC结构中的R时,其性能虽不太熟悉但一样简单。如果用-R代替电阻R,就建立了一个正RC的时间常数。于是,就建立了一个发散指数VINe+t/RC。

理论上,波形将不能会聚到零,而是发散至无穷大,并且当t=T时,V=2VIN,t=2T时,V=4VIN,t=3T时,V=8VIN,等等。因此,在负放电开始后简单地等候正确的时间量(t=log2(V/VIN)T),就可以放大输入电压。发散指数和负时间常数是图2中电路的核心概念。

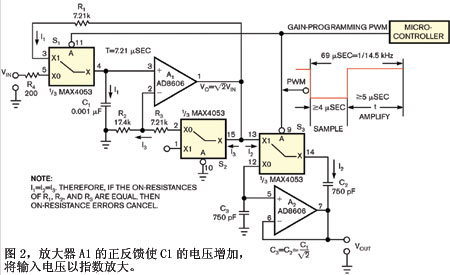

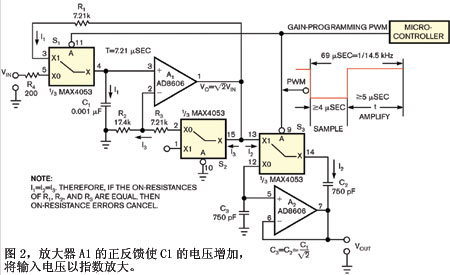

可以用来自微控制器或其它电路的PWM(脉宽调制)信号设定放大器的增益。当PWM信号达到逻辑零时,采样与保持电容C1充电至 VIN。当PWM信号循环到逻辑1时,运放A1驱动正反馈回路R1C1,建立一个负时间常数。当PWM信号保持在逻辑1时,所获得的C1充电发散指数式上升持续下去。这种情况产生的净电压增益为

VOUT(t)=VIN2(t/10 μs+0.5)。

因此,增益=2(t/10 μs+0.5),log(增益)=3+0.6dB/μs。在放大周期结束,PWM返回逻辑零时,放大器A2捕捉并保持住放大的输入电压。

增益与时序之间的对数关系提供了出色的增益分辨率,即使一个PWM信号只有8bit分辨率,其可编程增益范围大于每步0.2dB/LSB。

指数信号时序、ADC采样、抖动以及RC时间常数稳定的精度与可重复性等都限制了放大的增益编程的精度。在图2中,1ns的时序误差(或抖动)会产生 0.007%的增益编程误差。所幸,几乎所有微控制器和数据采集系统中都有可编程定时器/计数器硬件,通常很容易数字式地生成一个高度可重复的PWM控制信号。

显然大家都很熟悉e–t/RC会聚指数,RC电路中的一只电容会渐近地放电至零。对于输入电压,在t=T=loge(2)RC时 V=VIN/2,t=2T时V=VIN/4,t=3T时V=VIN/8,等等。当用一个合成负电阻的有源电路代替同一个RC结构中的R时,其性能虽不太熟悉但一样简单。如果用-R代替电阻R,就建立了一个正RC的时间常数。于是,就建立了一个发散指数VINe+t/RC。

理论上,波形将不能会聚到零,而是发散至无穷大,并且当t=T时,V=2VIN,t=2T时,V=4VIN,t=3T时,V=8VIN,等等。因此,在负放电开始后简单地等候正确的时间量(t=log2(V/VIN)T),就可以放大输入电压。发散指数和负时间常数是图2中电路的核心概念。

可以用来自微控制器或其它电路的PWM(脉宽调制)信号设定放大器的增益。当PWM信号达到逻辑零时,采样与保持电容C1充电至 VIN。当PWM信号循环到逻辑1时,运放A1驱动正反馈回路R1C1,建立一个负时间常数。当PWM信号保持在逻辑1时,所获得的C1充电发散指数式上升持续下去。这种情况产生的净电压增益为

VOUT(t)=VIN2(t/10 μs+0.5)。

因此,增益=2(t/10 μs+0.5),log(增益)=3+0.6dB/μs。在放大周期结束,PWM返回逻辑零时,放大器A2捕捉并保持住放大的输入电压。

增益与时序之间的对数关系提供了出色的增益分辨率,即使一个PWM信号只有8bit分辨率,其可编程增益范围大于每步0.2dB/LSB。

指数信号时序、ADC采样、抖动以及RC时间常数稳定的精度与可重复性等都限制了放大的增益编程的精度。在图2中,1ns的时序误差(或抖动)会产生 0.007%的增益编程误差。所幸,几乎所有微控制器和数据采集系统中都有可编程定时器/计数器硬件,通常很容易数字式地生成一个高度可重复的PWM控制信号。

放大器 ADC 半导体 DAC 运算放大器 电路 电容 电压 电阻 PWM 相关文章:

- 使用简化电路的高压放大器(11-21)

- 无需调谐的“砖墙式”低通音频滤波器(11-20)

- 对数放大器的技术指标(11-26)

- 一种增大放大器增益的方法(11-28)

- 对数放大器的典型应用 (11-26)

- AGC中频放大器的设计 (11-29)