数字下变频器的发展和更新——第二部分

时间:12-28

来源:互联网

点击:

作者:Jonathan Harris

在本文第一部分 《数字下变频器的发展和更新——第一部分》, 中,我们讨论了在更高频率的RF频段中进行频率采样的行业趋势以及数字下变频器(DDC)如何支持此类无线电架构。文中对AD9680系列产品所含DDC的几个技术方面进行了探讨。其中一个方面就是,更高的输入采样带宽允许无线电架构在更高的RF频率下直接采样,并将输入信号直接转换为基带。DDC可使RF采样ADC对此类信号进行数字化,而无需处理大量的数据吞吐量。DDC中的调谐和抽取滤波机制可以用来调整输入频带和滤除干扰频率。在本部分中我们将进一步分析抽取滤波,并将其应用于第一部分所讨论的示例。此外,我们将讨论Virtual Eval,该产品在改良的新型软件仿真工具中融入了ADIsimADC引擎技术。Virtual Eval将用于验证仿真结果与实测数据的匹配程度。

在第一部分中我们分析了一个示例,利用DDC中的NCO和抽取滤波来观察DDC中频率折叠和转换效果的影响。现在我们进一步分析抽取滤波,以及ADC混叠如何影响抽取滤波的有效响应。同样,我们将以AD9680 为例进行讨论。我们对抽取滤波器响应进行了归一化,使其便于查看和理解,并且可应用于每个速度等级。抽取滤波器响应仅与采样速率成比例。本文的滤波器响应图并没有确切具体地提供插入损耗与频率之间的关系,而是形象地描绘了该滤波器的近似响应情况。通过这些示例可以更好地了解抽取滤波器响应,以便大致了解滤波器通带和阻带所处的位置。

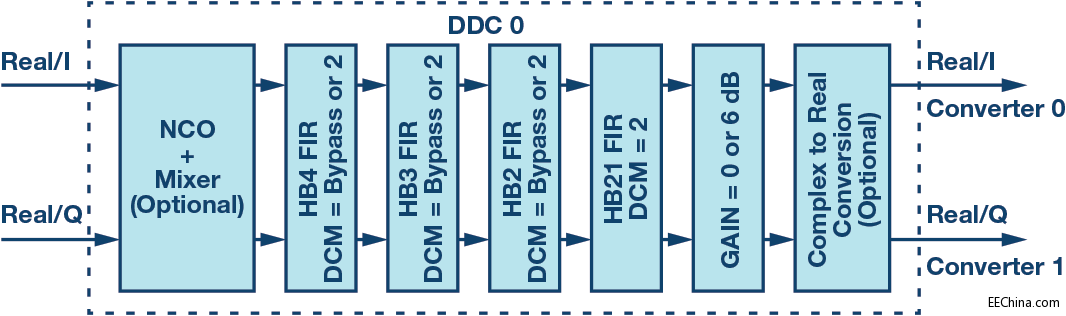

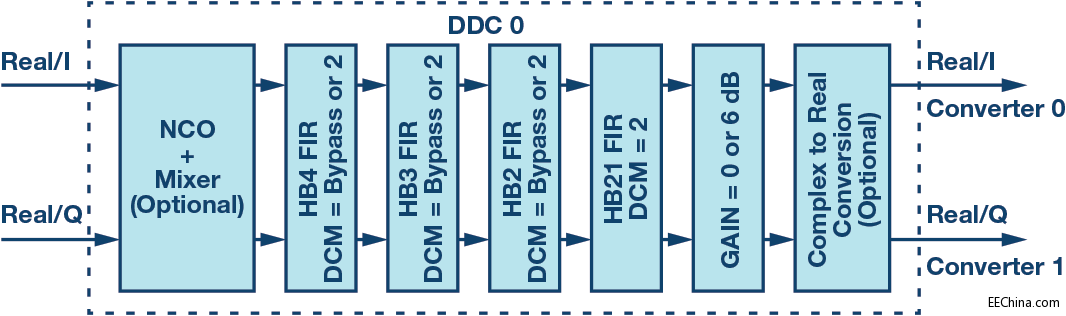

如前所述,AD9680具有四个DDC,各含一个NCO,多达四个级联的半带(HB)滤波器(亦称为抽取滤波器),一个可选性6 dB增益模块以及一个可选复数转实数模块,如图1所示。我们曾在第一部分讨论过,信号首先通过NCO,使输入信号音的频率偏移,然后通过抽取模块,也可选择通过增益模块,以及选择通过复数转实数模块。

图1. AD9680中的DDC信号处理模块。

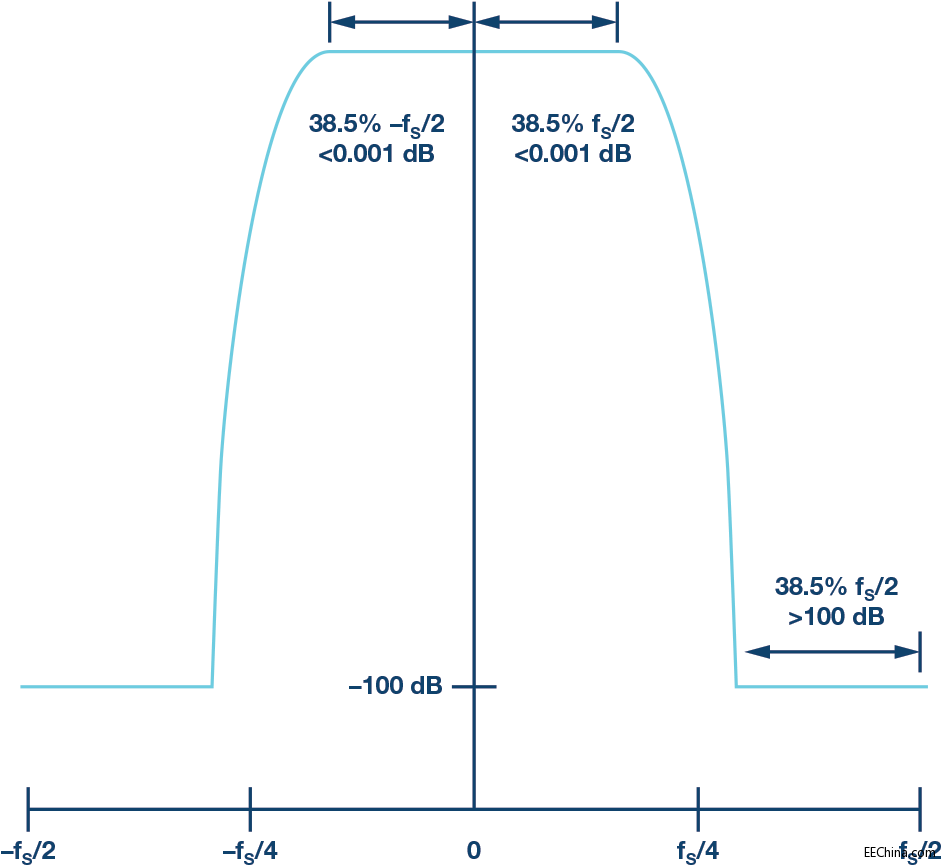

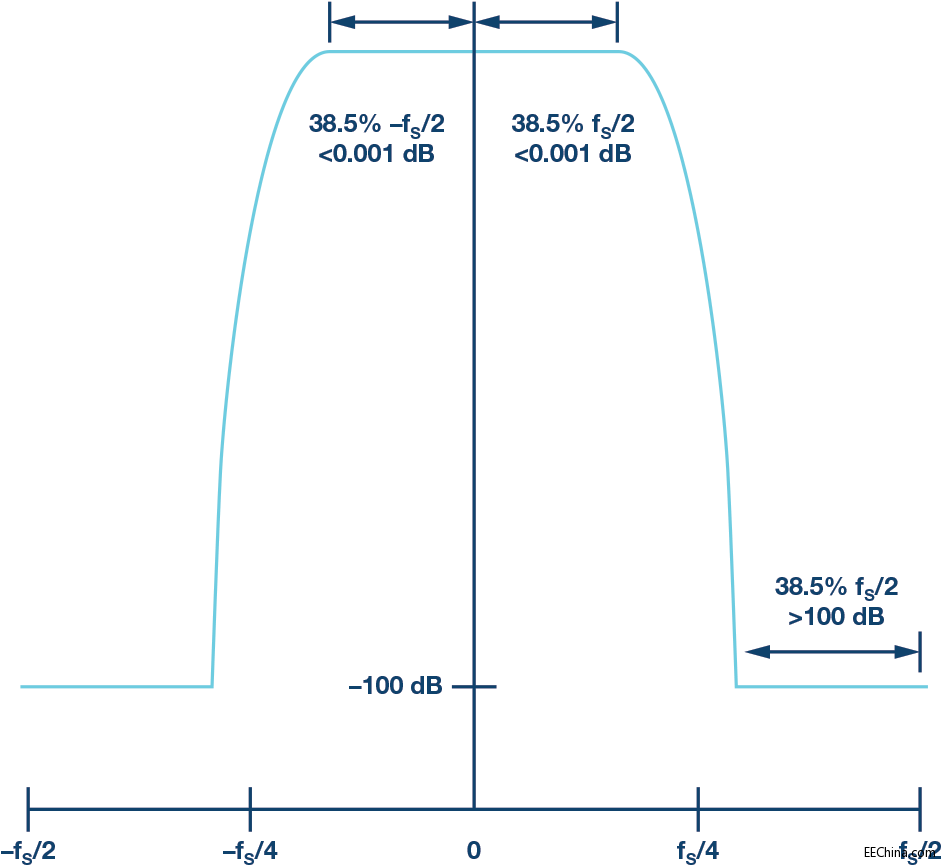

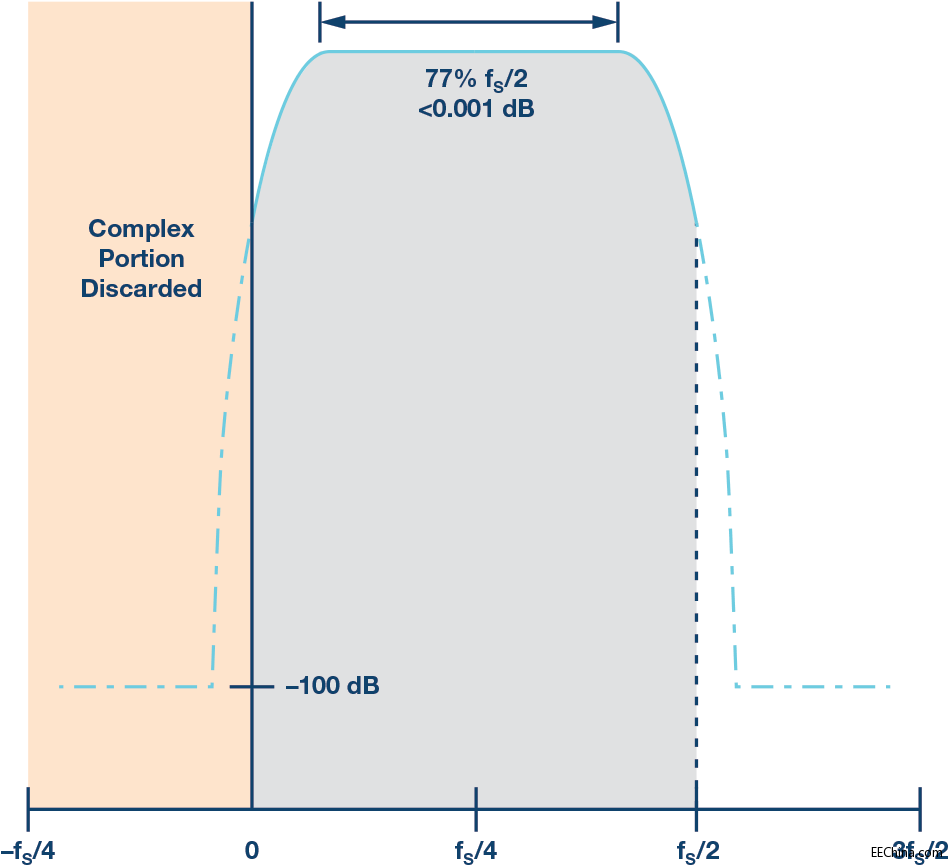

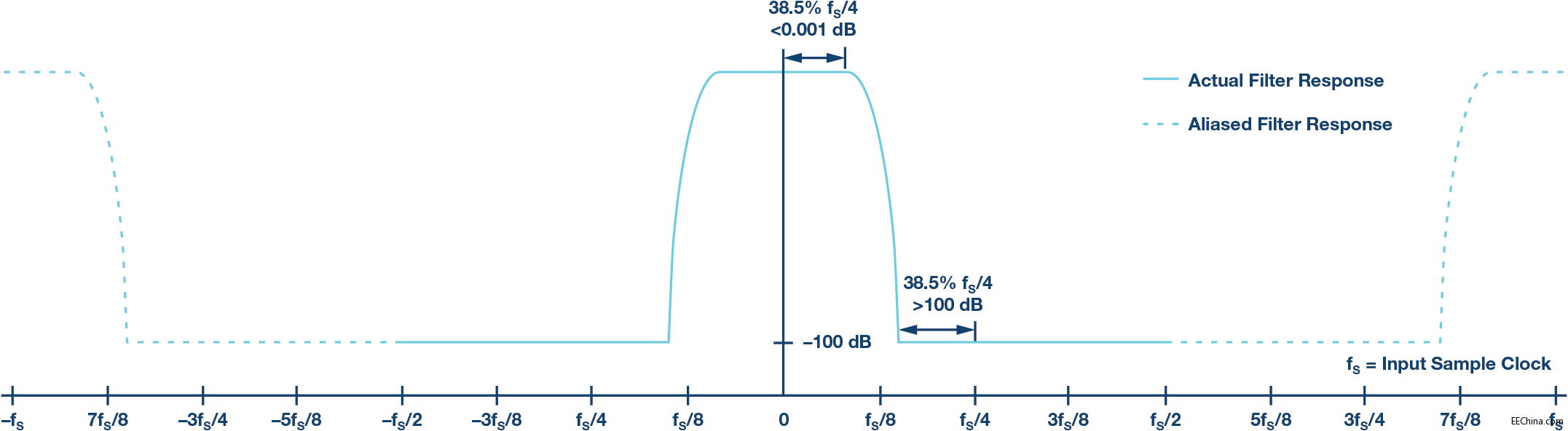

首先我们将讨论在AD9680中使能复数转实数模块时DDC抽取滤波器的情况。这意味着DDC将配置为接受实数输入和产生实数输出。在AD9680中,复数转实数模块会使输入频率自动向上偏移fS/4。图2所示为HB1滤波器的低通响应。这是HB1响应,显示了实数和复数域响应部分。若要了解滤波器的实际运作,首先要观察滤波器在实数域和复数域内的基本响应,从而可以观察到低通响应。HB1滤波器有一个通带占实数奈奎斯特区的38.5%。还有一个阻带也占实数奈奎斯特区的38.5%,其过渡带占剩余的23%。同样,在复数域,通带和阻带各占复数奈奎斯特区的38.5%(共77%),而过渡带占剩余的23%。如图2所示,滤波器是位于实数域和复数域之间的一个镜像。

图2. HB1滤波器响应—实数域和复数域响应。

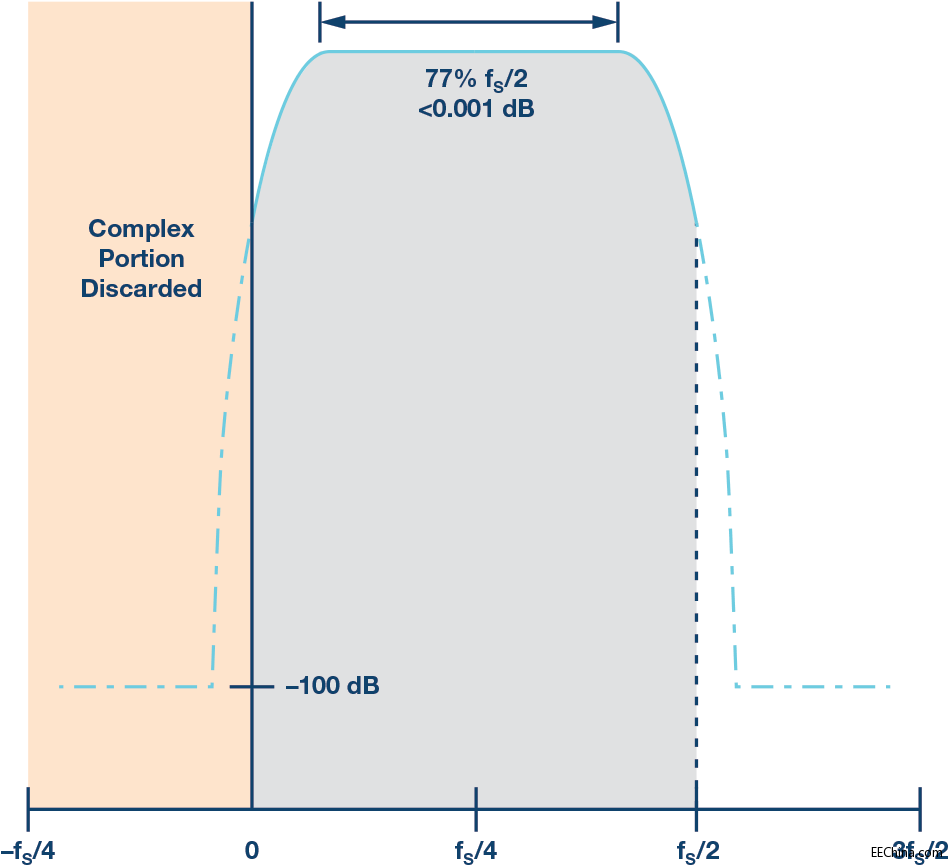

现在我们可以观察到,通过使能复数转实数模块将DDC置为实数模式时会发生什么情况。使能复数转实数模块会导致频域中出现fS/4的偏移。如图3所示,可看到频移和产生的滤波器响应。注意该滤波器响应的实线和虚线。实线和阴影区表示这是fS/4频移后新的滤波器响应(产生的滤波器响应不能跨越奈奎斯特边界)。虚线用来显示若未进入奈奎斯特边界本该存在的滤波器响应。

图3. HB1滤波器响应—DDC实数模式(复数转实数模块使能)。

注意,在图2和图3中,HB1滤波器的带宽保持不变。两者之间的区别是fS/4频移和第一奈奎斯特区内的中心频率。然而应注意,在图2中,我们将奈奎斯特区的38.5%用于信号的实数部分,另38.5%用于信号的复数部分。在图3中,复数转实数模块已使能,奈奎斯特区的77%均用于实数信号,而复数域已被丢弃。除了fS/4频移之外,过滤器响应保持不变。还应注意,该转换的一个结果是:抽取率此时等于1。有效采样速率仍然是fS,但奈奎斯特区内仅有77%的可用带宽,而不是整个奈奎斯特区均可用。这意味着,当HB1滤波器和复数转实数模块使能时,抽取率等于1(更多信息请参阅AD9680数据手册)。

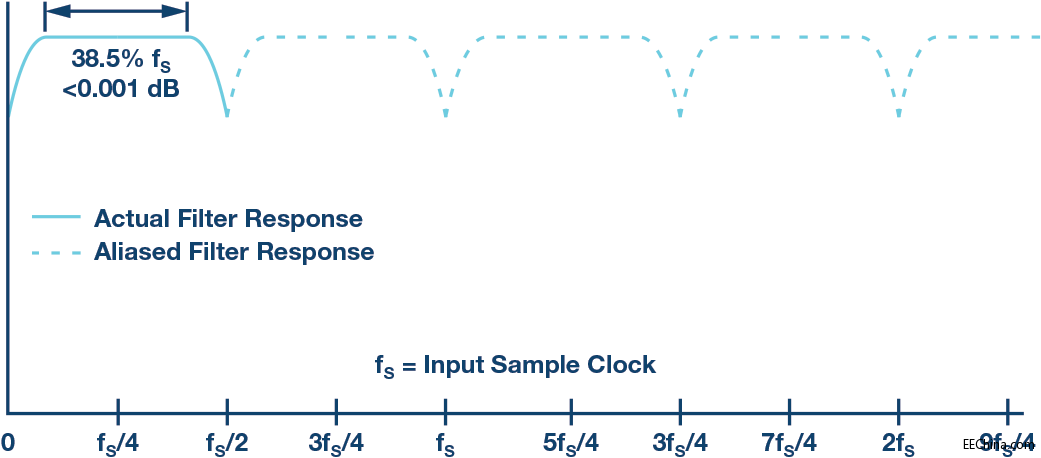

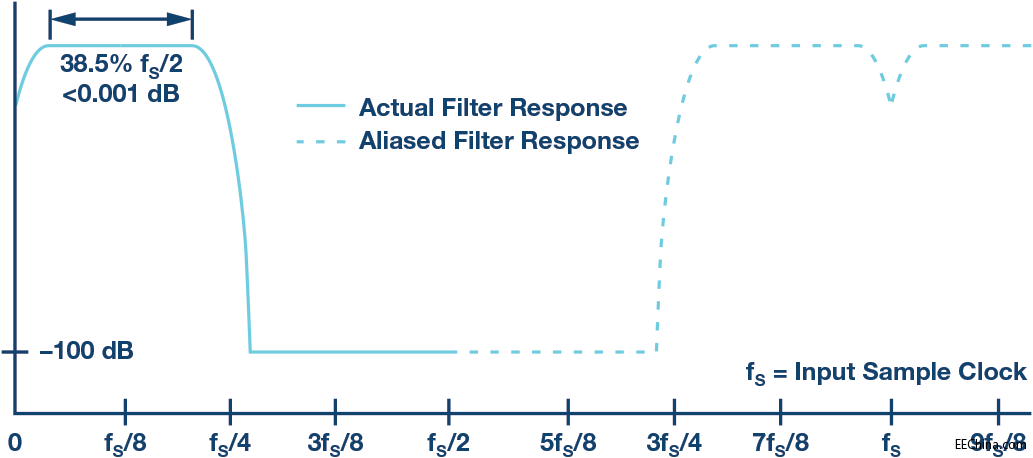

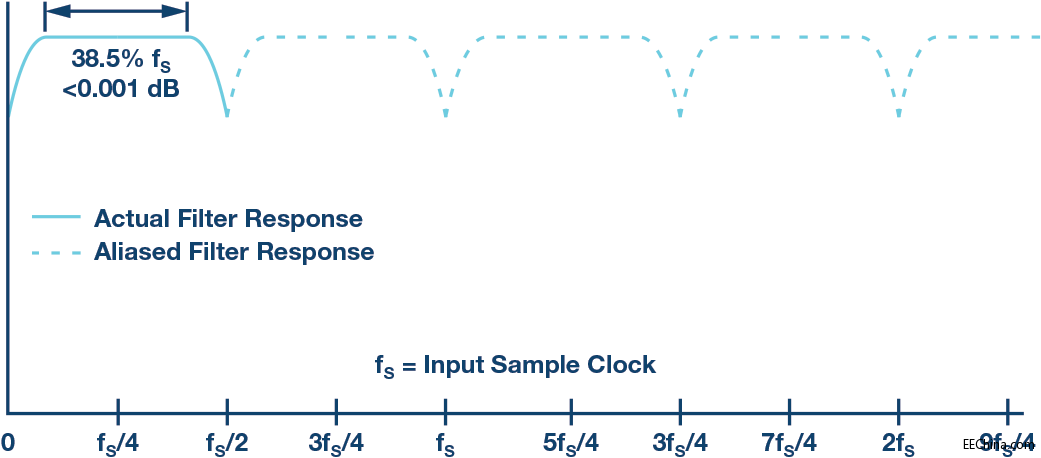

下面我们来看看滤波器在不同抽取率(即,使能多个半带滤波器)的响应,以及ADC输入频率混叠对有效的抽取滤波器响应有何影响。图4中的蓝色实线表示HB1的实际频率响应。虚线则表示因ADC混叠效应所产生的HB1有效混叠响应。由于第二、第三、第四……奈奎斯特区的输入频率实际上混叠到ADC的第一奈奎斯特区,因此HB1滤波器响应有效地混叠到这些奈奎斯特区。例如,一个驻留在3fS/4的信号将混叠到第一奈奎斯特区的fS/4。HB1滤波器响应仅驻留在第一奈奎斯特区,并且是ADC混叠导致了HB1的有效响应看起来像是混叠到其他奈奎斯特区,理解这一点非常重要。

图4. ADC混叠导致的HB1有效滤波器响应。

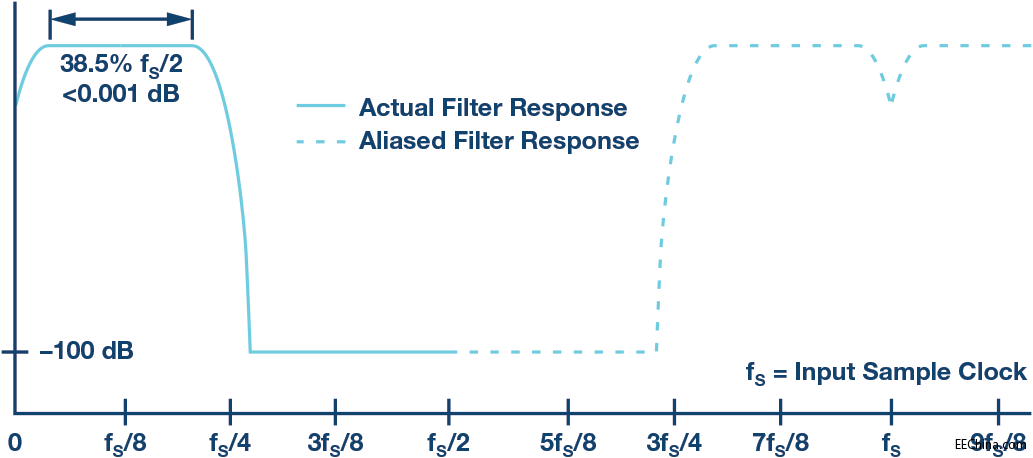

现在我们来讨论HB1 + HB2使能的情况。其结果会使抽取率为2。这里的蓝色实线也表示HB1 + HB2滤波器的实际频率响应。滤波器通带的中心频率仍是fS/4。HB1 + HB2使能将导致可用带宽占奈奎斯特区的38.5%。同样,请注意ADC的混叠效应及其对HB1 + HB2滤波器组合的影响。一个出现在7fS/8的信号将混叠到第一奈奎斯特区的fS/8。类似的,一个5fS/8的信号将混叠到第一奈奎斯特区的3fS/8。这些复数转实数模块使能的示例可以从含有HB1 + HB2很方便地扩展到含有HB3和HB4滤波器二者或其中之一。注意,当DDC使能时,HB1滤波器不可旁通,而HB2、HB3和HB4滤波器可选择使能。

图5. ADC混叠导致的HB1+HB2有效滤波器响应(抽取率=2)。

我们已经讨论了抽取滤波器使能时的实数工作模式,现在我们可以探讨DDC的复数工作模式。仍以AD9680为例。与DDC的实数工作模式类似,这里将展示归一化的抽取滤波器响应。同样,示例滤波器响应图中没有确切表明插入损耗与频率之间的具体关系,而是形象地描绘了该滤波器的近似响应。这样做是为了便于更好地了解ADC混叠如何影响滤波器响应。

在复数模式中使用DDC时,它配置为具有一个复数输出,由实数和复数频域(通常称为I和Q)构成。回顾图2可知,HB1滤波器具有低通响应,通带为实数奈奎斯特区的38.5%。还有一个阻带也占实数奈奎斯特区的38.5%,其过渡带占剩余的23%。同样,在复数域,通带和阻带各占复数奈奎斯特区的38.5%(共77%),而过渡带占剩余的23%。

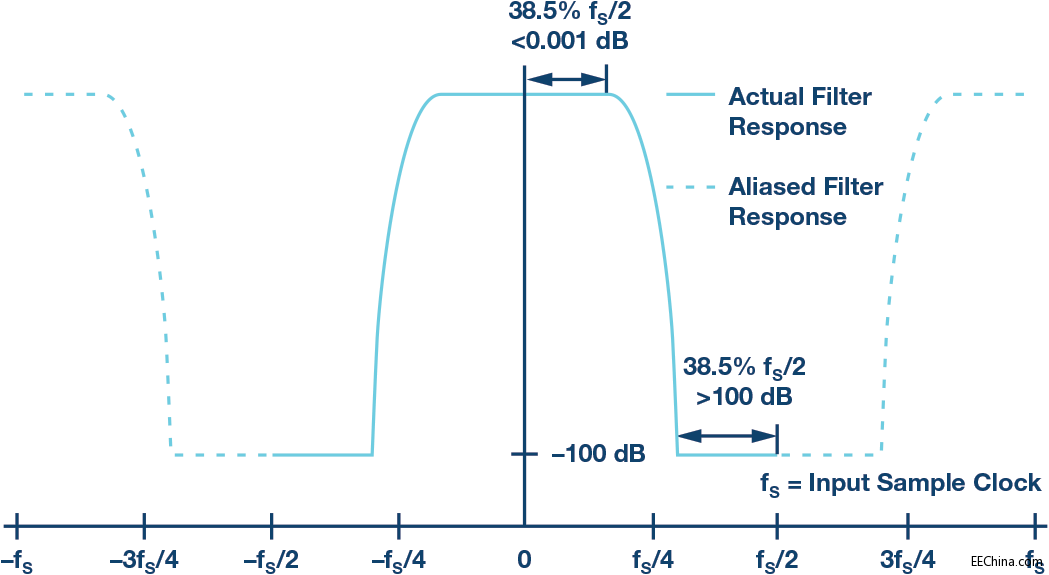

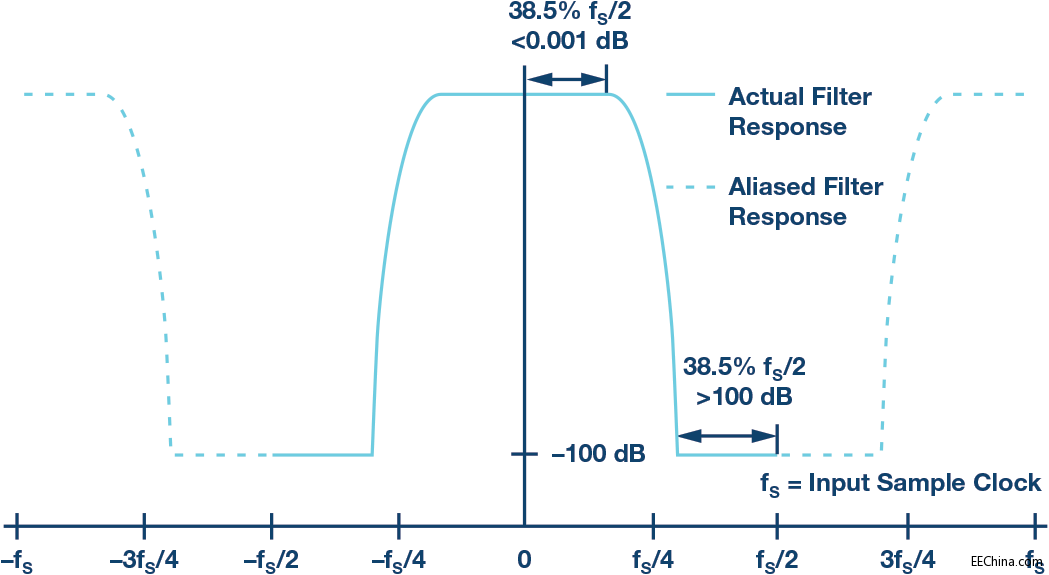

当HB1滤波器使能,在复数输出模式下操作DDC时,抽取率等于二,输出采样速率为输入采样时钟的二分之一。扩展图2中的曲线可显示出图6所示的ADC混叠的影响。其中的蓝色实线表示实际滤波器响应,蓝色虚线则表示因ADC混叠效应所产生的滤波器的有效混叠响应。7fS/8的输入信号将混叠到第一奈奎斯特区的fS/8,使其位于HB1滤波器的通带内。同一信号的复数镜像驻留于–7fS/8,并将在复数域混叠到–fS/8,使其位于复数域的HB1滤波器通带内。

图6. ADC混叠导致的HB1有效滤波器响应(抽取率=2)—复数。

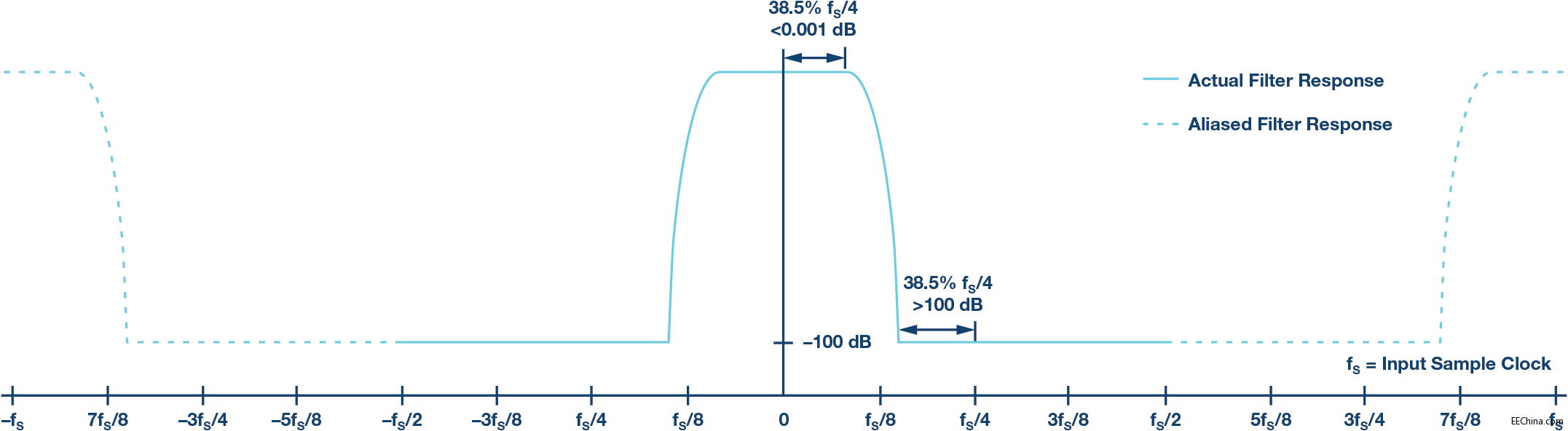

接下来,我们将讨论HB1 + HB2使能的情况,如图7所示。其结果会使得每个I和Q输出的抽取率为4。这里的蓝色实线也表示HB1 +HB2滤波器的实际频率响应。HB1 + HB2滤波器同时使能将导致每个实数和复数域中的可用带宽为抽取奈奎斯特区的38.5%(fS/4的38.5%,其中fS为输入采样时钟)。请注意ADC的混叠效应及其对HB1 + HB2滤波器组合的影响。一个出现在15fS/16的信号将混叠到第一奈奎斯特区的fS/16。该信号在复数域的–15fS/16有一个复数镜像,并将混叠到复数域第一奈奎斯特区的–fS/16。同理,这些示例也可以扩展到HB3和HB4均使能的情况。本文中并未显示这些内容,但根据图7所示的HB1 + HB2响应很容易推算出来。

图7. ADC混叠导致的HB1 + HB2有效滤波器响应(抽取率=4)—复数。

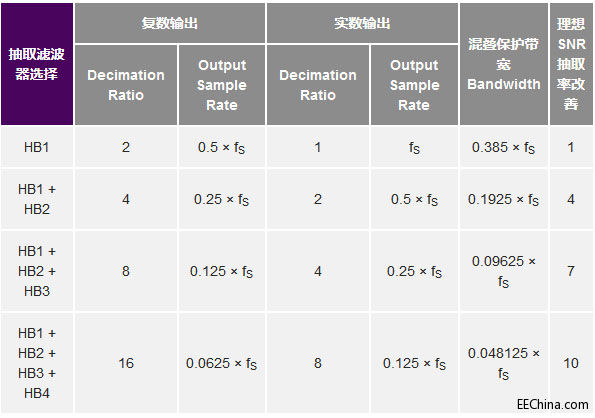

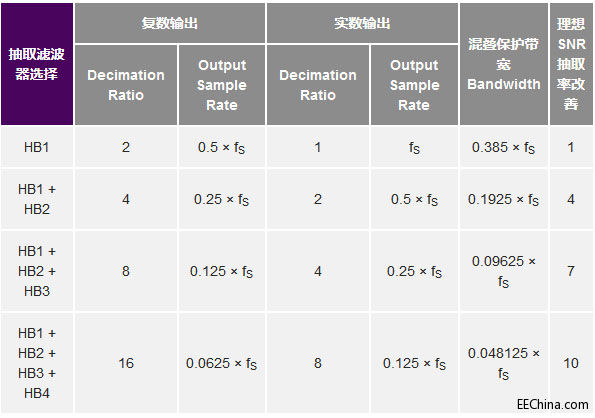

看到所有这些抽取滤波器响应,您的脑海里可能会有这样的问题:"我们为什么要抽取?"以及"这样做有什么好处?"不同的应用具有不同的要求,而这些要求可以从ADC输出数据的抽取中获利。其中一个原因是要增大RF频带中某段狭窄频带上的信噪比。另一个原因是为了使处理带宽更小,这样可使JESD204B接口的输出通道速率降低,从而便于使用低成本的FPGA。通过使用全部四个抽取滤波器,DDC可实现处理增益,并使SNR改善达10 dB。在表1中,我们可以看到当DDC工作于实数模式和复数模式时,不同的抽取滤波器选择所提供的可用带宽、抽取率、输出采样速率和理想SNR改善情况。

表1. DDC滤波器特性(AD9680)

关于DDC工作模式的讨论有助于深入了解AD9680中抽取滤波器的实数工作模式和复数工作模式。采用抽取滤波可提供多个好处。DDC可工作于实数模式或复数模式,允许用户根据特定应用的需求采用不同的接收器拓扑。结合第一部分所述的内容,还有助于探讨采用AD9680的一个真实示例。该示例将综合实测数据和Virtual Eval中导出的仿真数据,以便于比较结果。

在此例中我们将采用在第一部分中曾使用的相同条件。输入采样 速率为491.52 MSPS,输入频率为150.1 MHz。NCO频率为155 MHz, 抽取率设为4(由于NCO分辨率,实际NCO频率为154.94 MHz)。因 此,输出采样速率为122.88 MSPS。由于DDC进行复数混频,因此 分析中包含复数频域。注意,图8中添加了抽取滤波器的响应, 以深紫色曲线表示。

图8. 信号通过DDC信号处理模块—抽取滤波。

NCO偏移后的频谱:

基频从+150.1 MHz下移至–4.94 MHz。

基频镜像从–150.1 MHz开始偏移,并绕回至+186.48 MHz。

二次谐波从191.32 MHz下移至36.38 MHz。

三次谐波从+41.22 MHz下移至–113.72 MHz。

2倍抽取后的频谱:

基频位于–4.94 MHz。

基频镜像向下转换至–59.28 MHz,并由HB1抽取滤波器衰减。

二次谐波位于36.38 MHz。

三次谐波由HB1抽取滤波器衰减。

4倍抽取后的频谱:

基频位于–4.94 MHz。

基频镜像位于–59.28 MHz,并由HB2抽取滤波器衰减。

二次谐波位于-36.38 MHz,并由HB2抽取滤波器衰减。

三次谐波经过滤波,基本由HB2抽取滤波器完全消除。

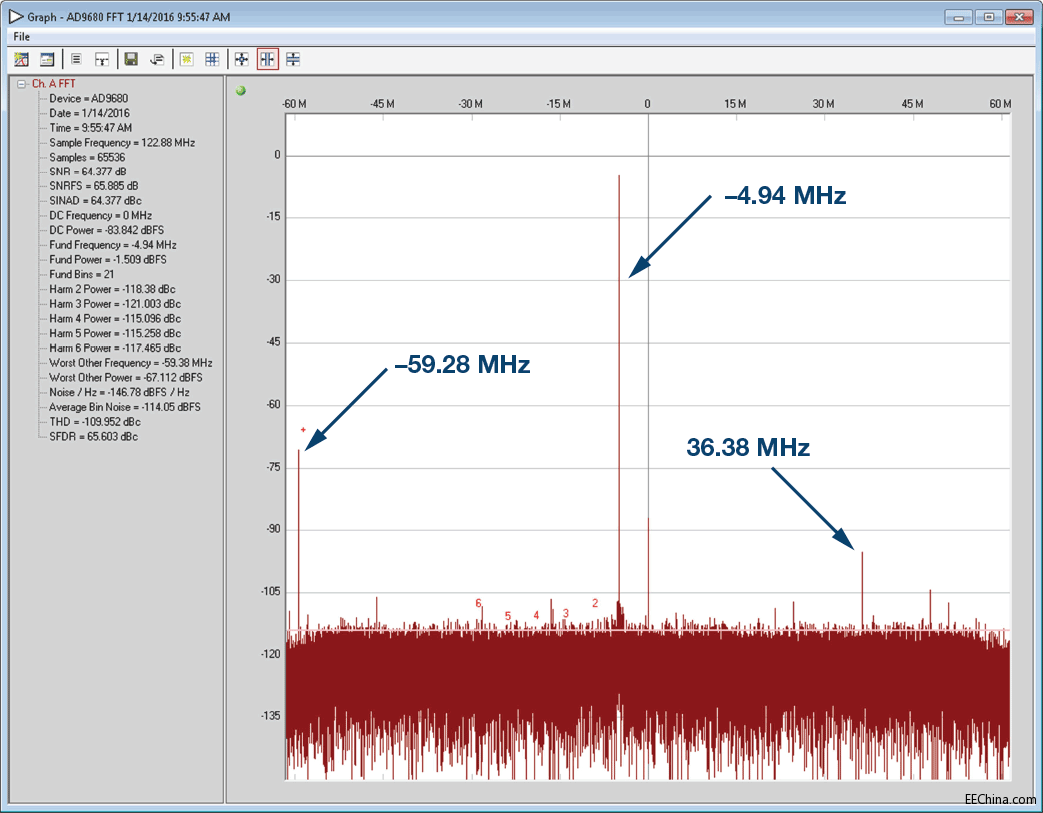

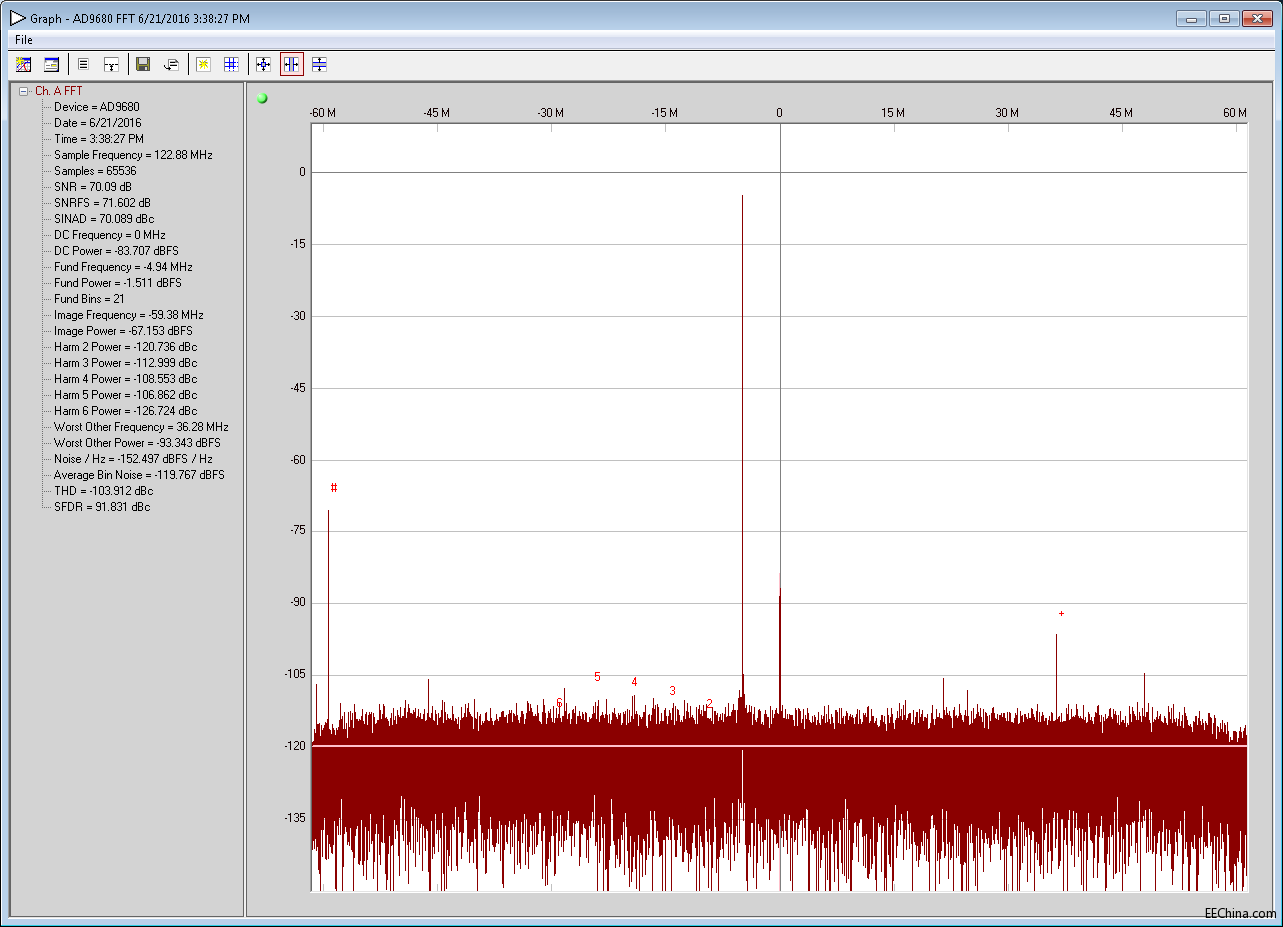

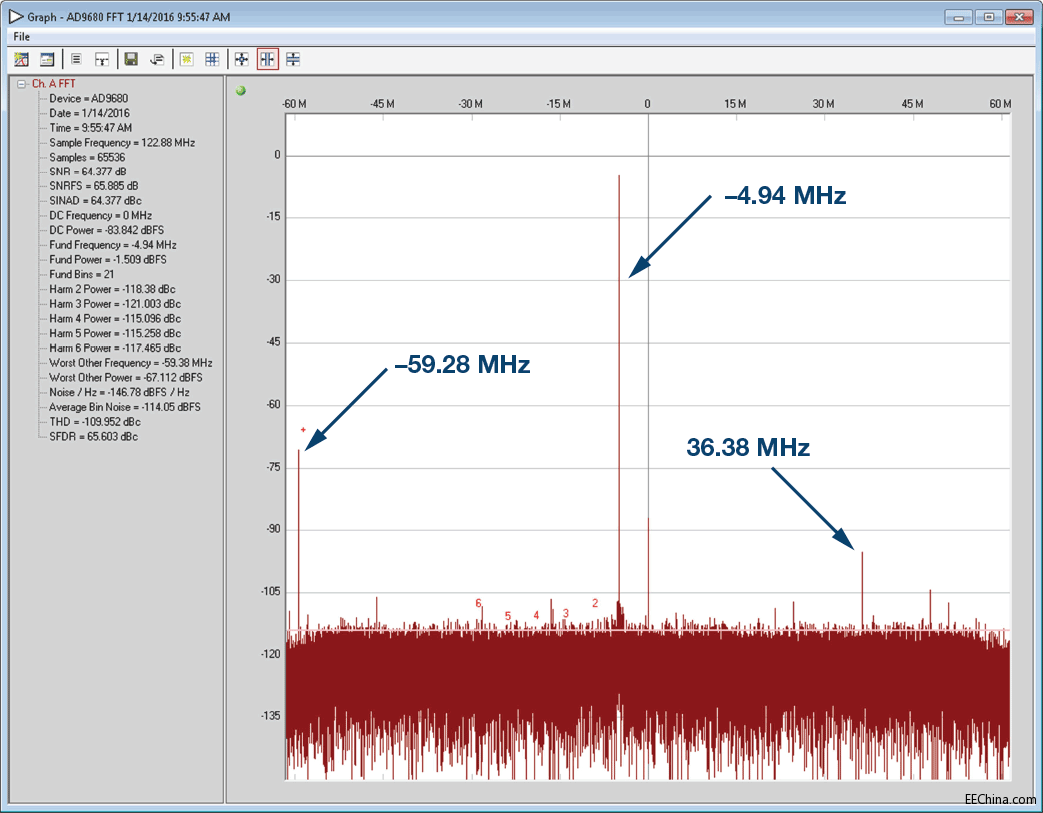

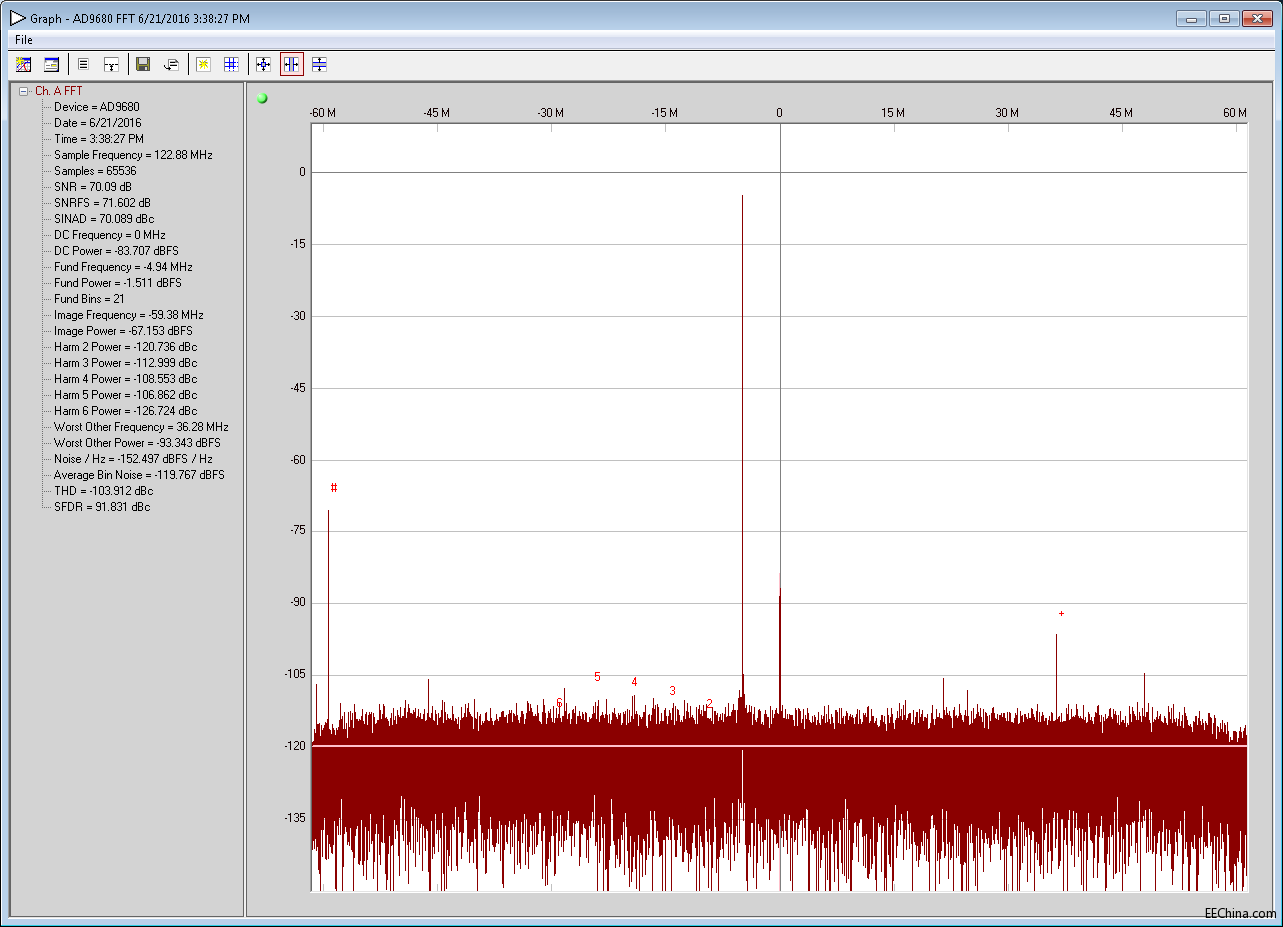

AD9680-500的实测结果如图9所示。基频位于–4.94 MHz。基频镜像位于–59.28 MHz,幅度为–67.112 dBFS,意味着镜像衰减了大约66 dB。二次谐波位于36.38 MHz,并衰减了大约10至15 dB。三次谐波经过充分滤波,实测结果不高于噪底。

图9. 信号经过DDC后的FFT复数输出(NCO = 155 MHz,4倍抽取)。

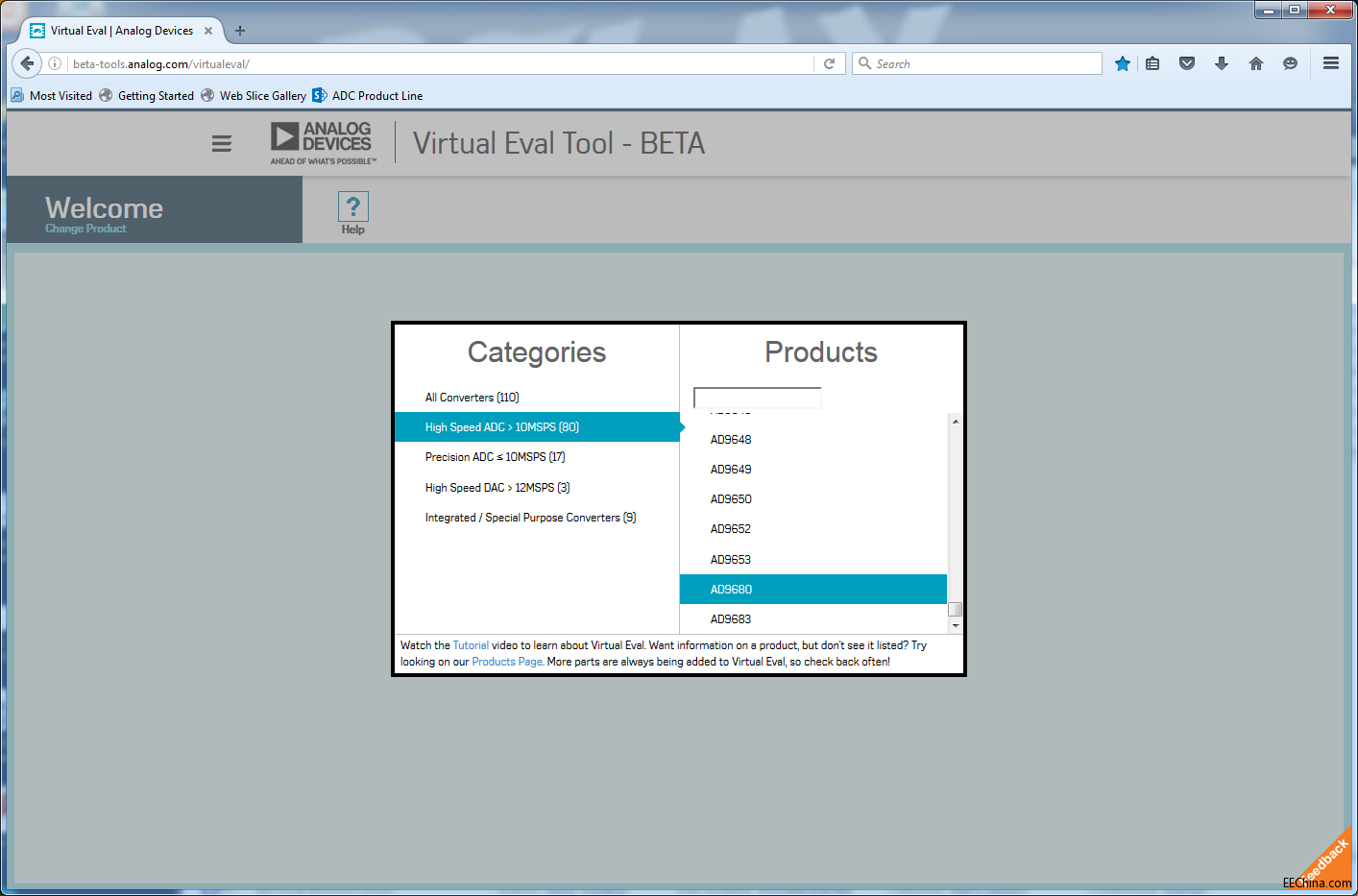

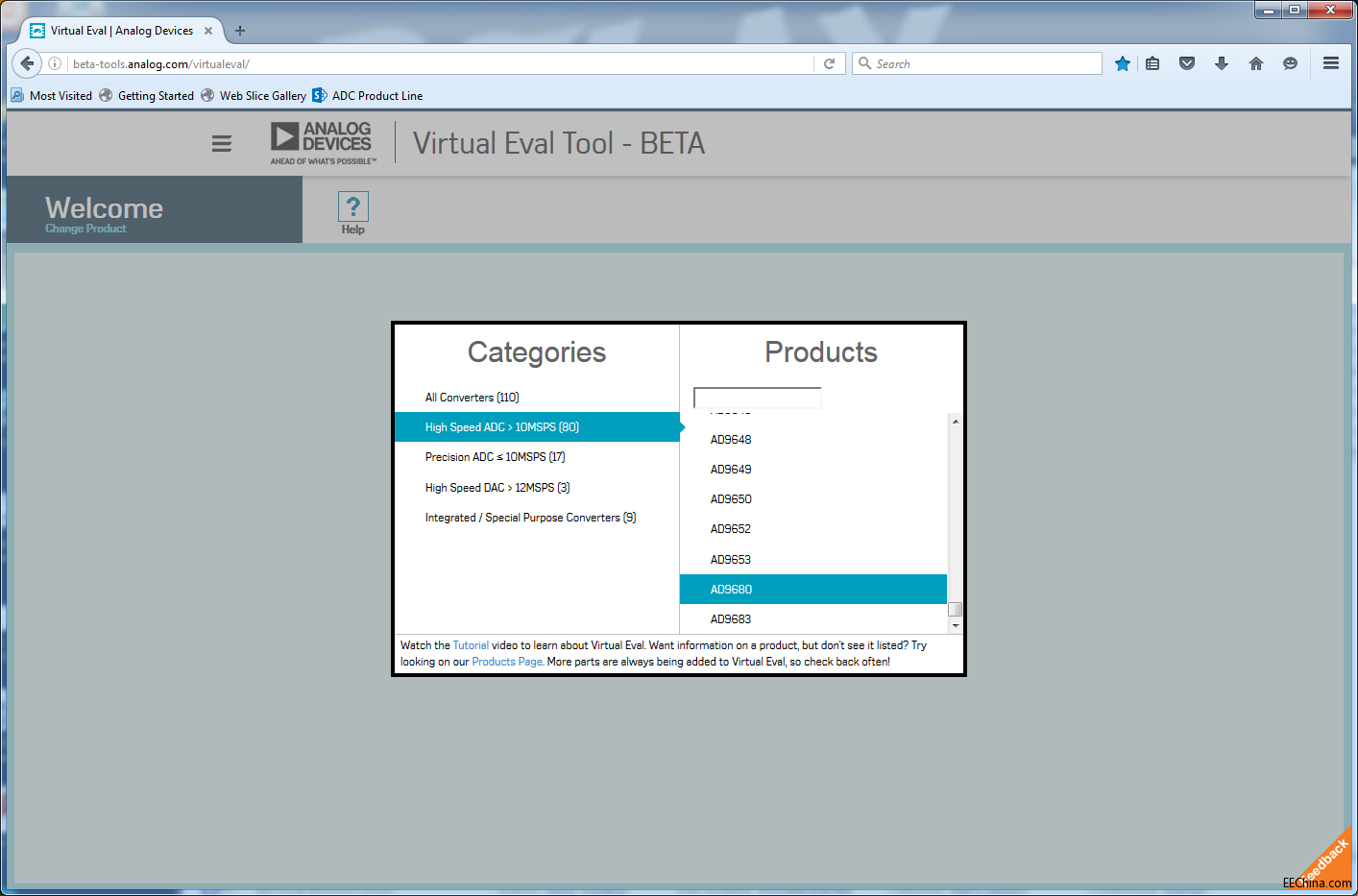

现在可使用Virtual Eval来观察仿真结果与实测结果的对比情况。首先,从网站上打开该工具,并选择要仿真的ADC(见图10)。Virtual Eval工具在ADI网站的Virtual Eval下。Virtual Eval中的AD9680模型含有一项新开发的功能,允许用户仿真不同的ADC速度等级。由于此示例使用了AD9680-500,所以该功能很重要。Virtual Eval加载后,首先提示选择产品类别和产品。注意,Virtual Eval中不仅涵盖高速ADC,而且包含精密ADC、高速DAC以及集成/专用转换器这些产品。

图10. Virtual Eval中的产品类别和选型。

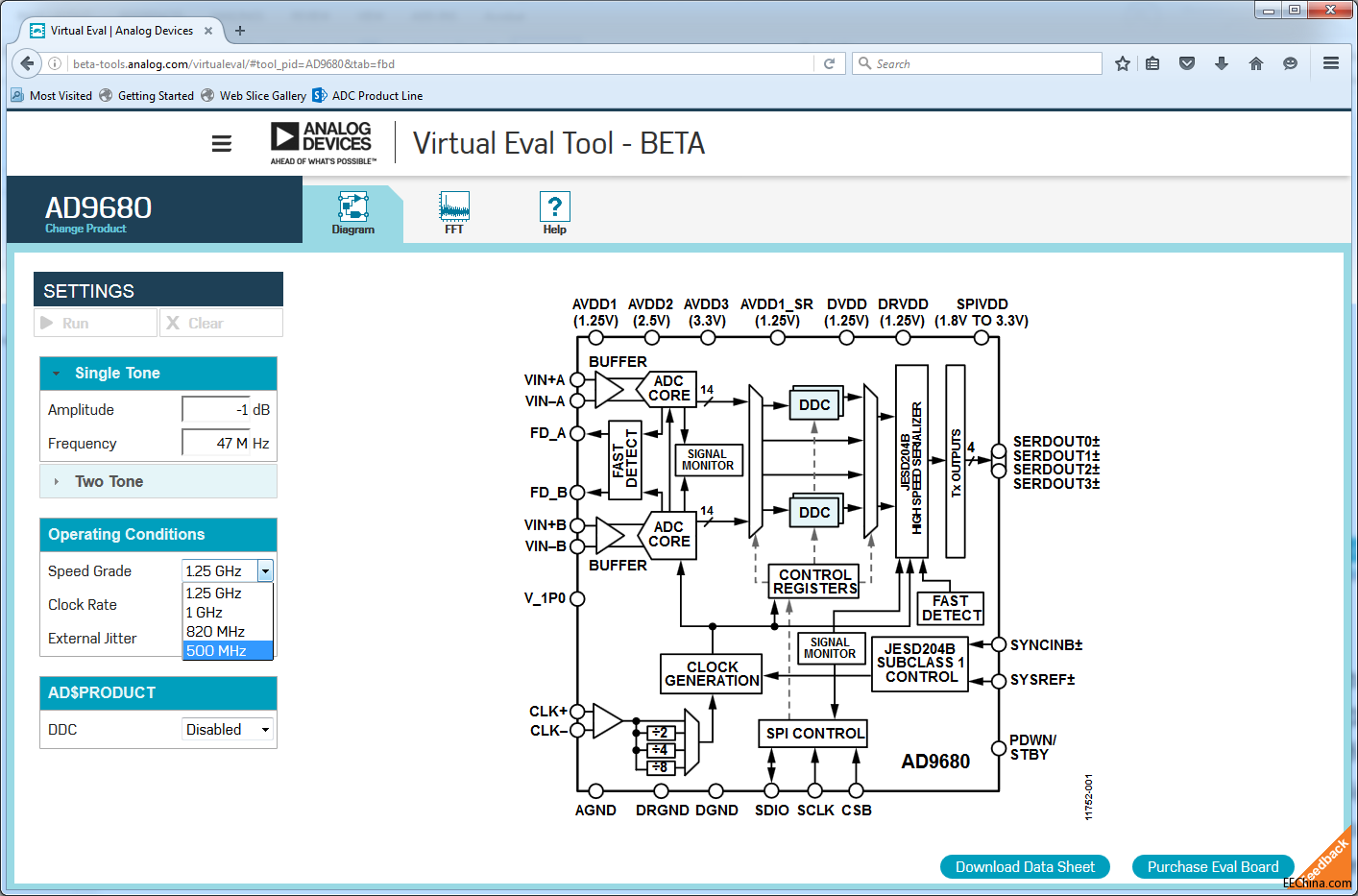

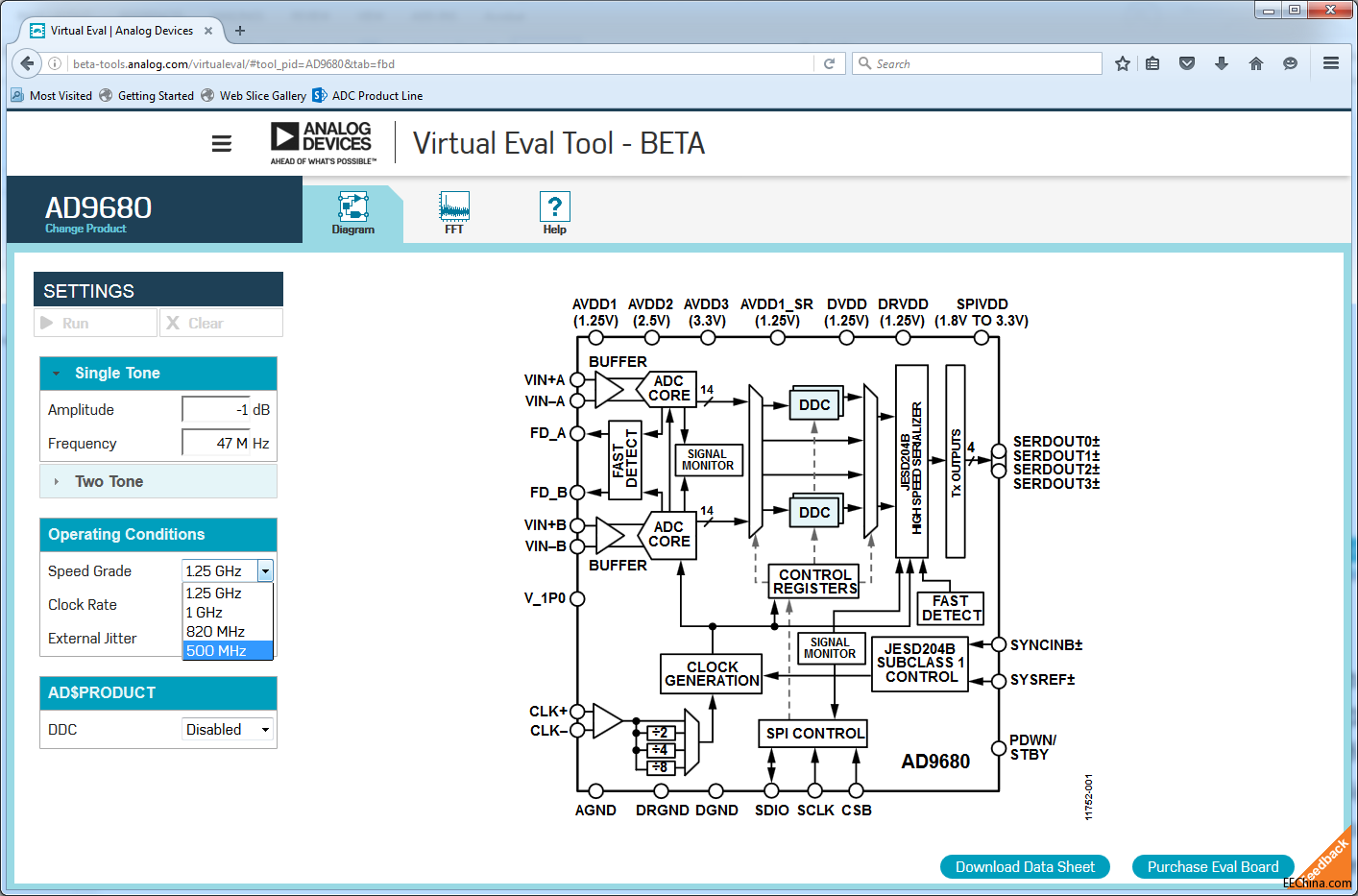

从产品列表中选择AD9680。这将会打开AD9680仿真的主页。VirtualEval中的AD9680模型还含有一个框图,详细介绍了ADC模拟功能和数字功能的内部配置。该框图与AD9680数据手册中的框图相同。在此页面的左侧下拉菜单中选择所需的速度等级。对于本例,速度等级选择500 MHz,如图11所示。

图11. Virtual Eval中的AD9680速度等级选择和框图。

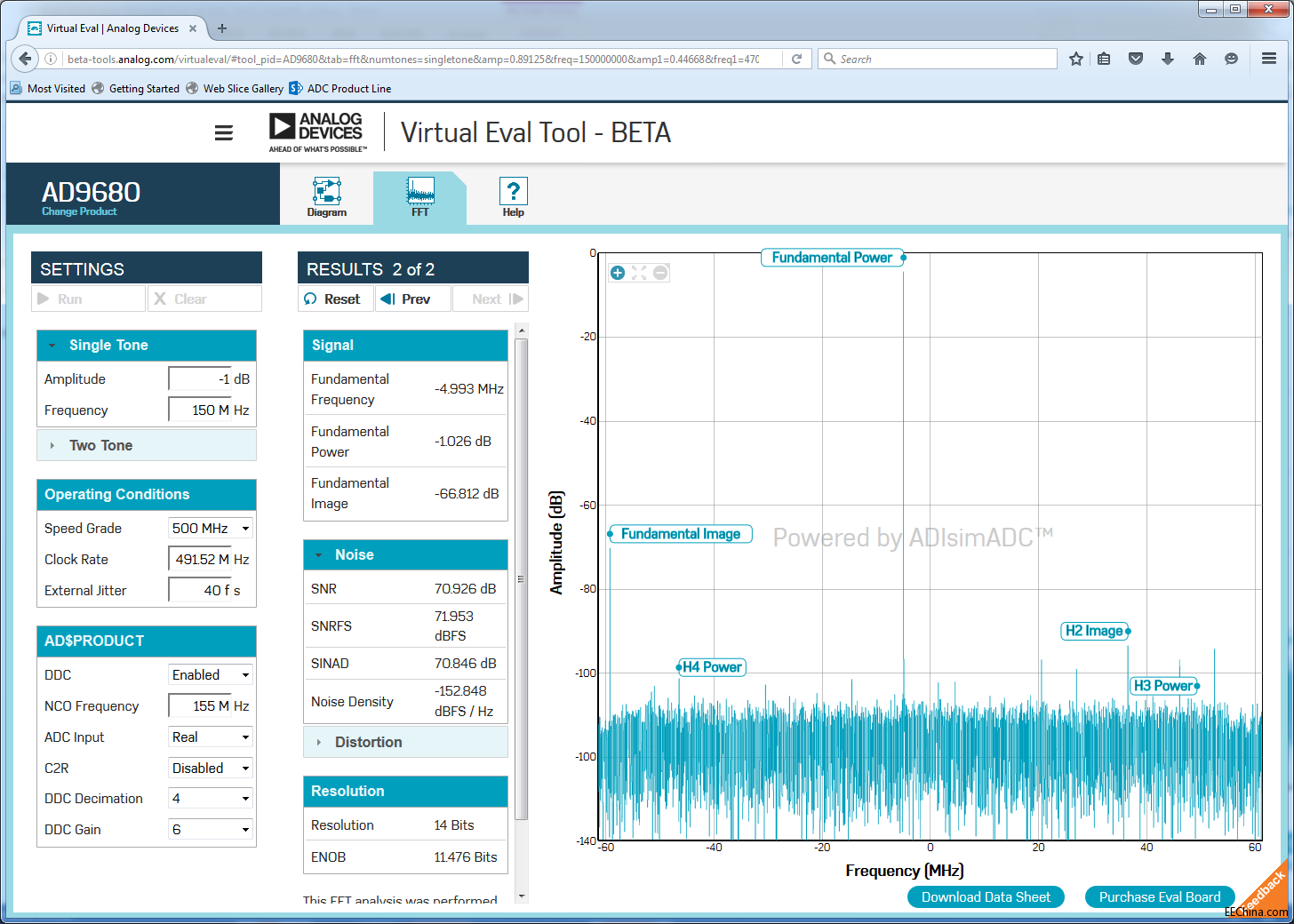

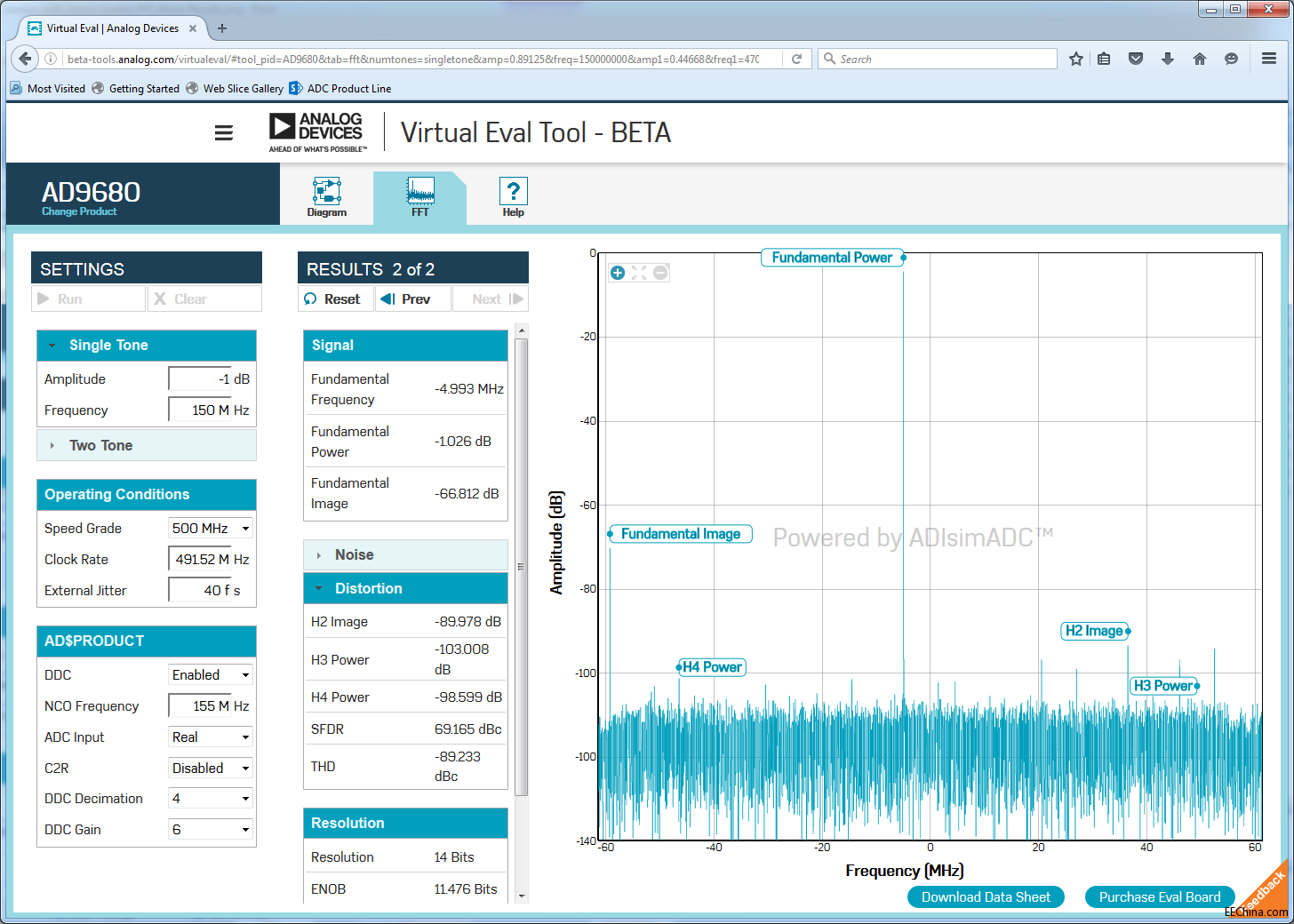

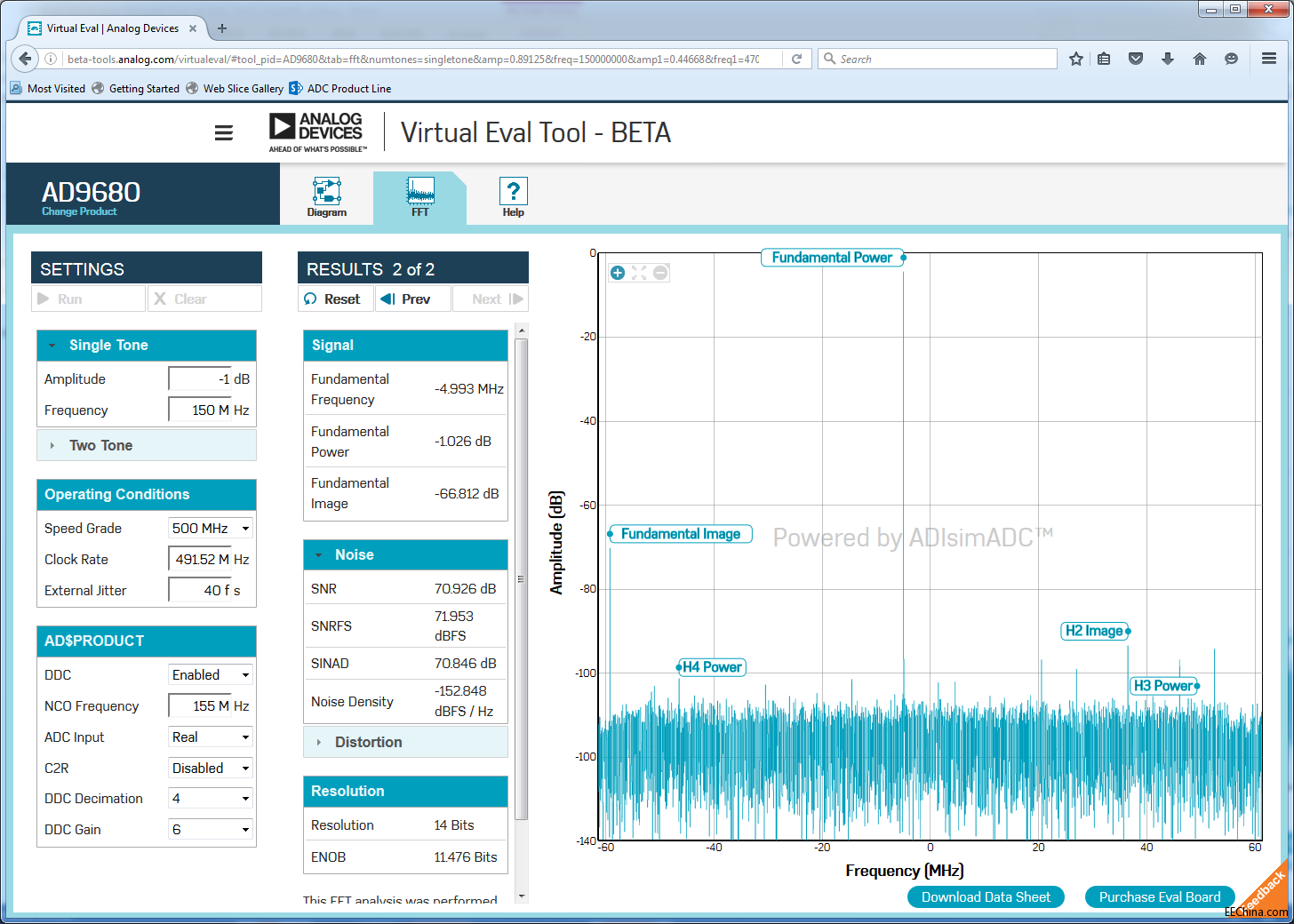

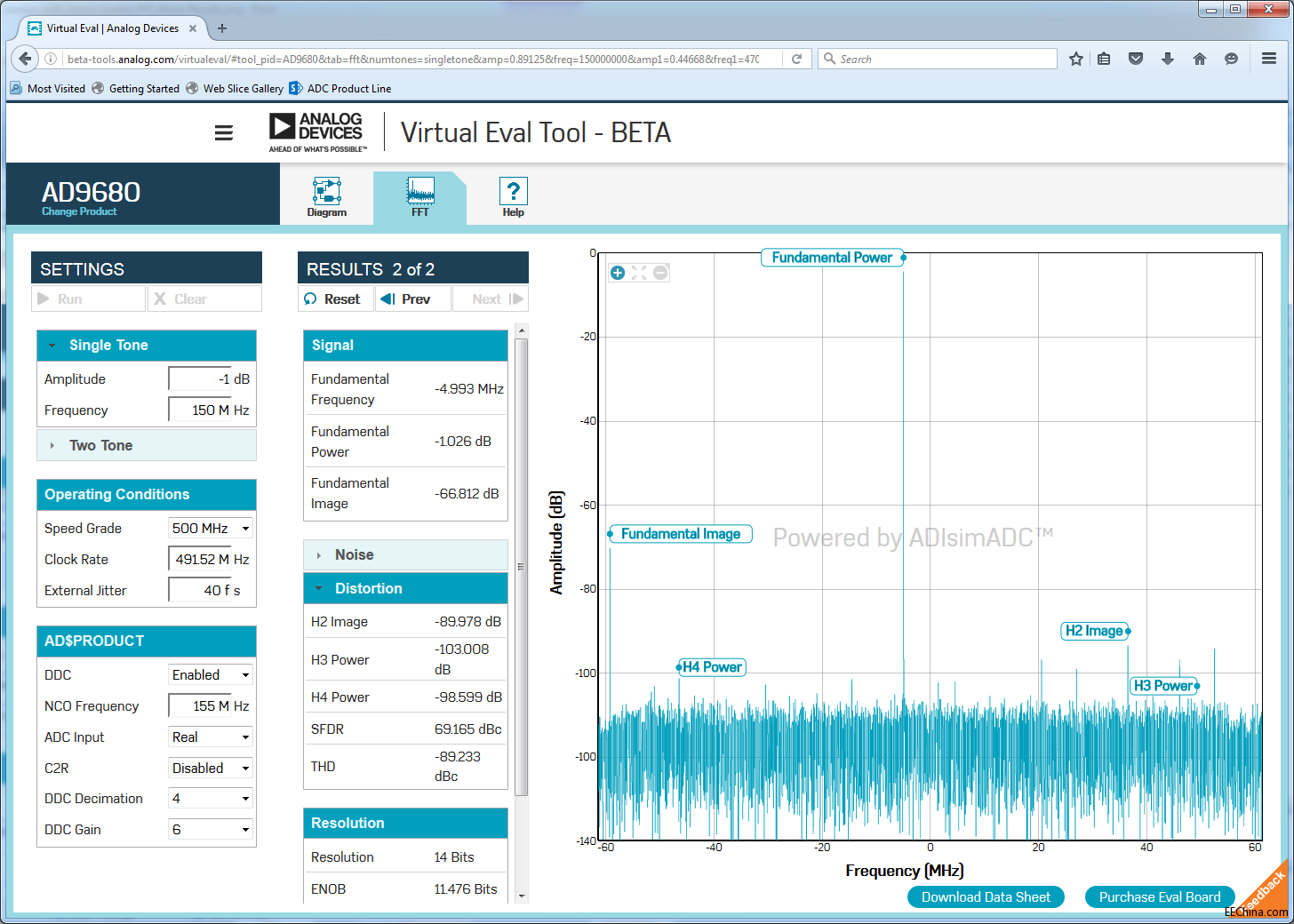

然后,为了执行FFT仿真,必须设定输入条件(见图12)。回顾一下,本例的测试条件包含一个491.52 MHz的时钟速率和一个150MHz的输入频率。DDC使能,NCO频率设为155 MHz,ADC输入设为Real(实数),复数转实数模块(C2R)为Disabled(禁用),DDC抽取率设为Four(4),DDC中的6 dB增益为Enabled(使能)。这意味着DDC将设为具有实数输入信号和复数输出信号,并且抽取率为4。DDC中的6 dB增益使能是为了补偿DDC中混频处理所导致的6 dB损耗。Virtual Eval每次只能显示噪声或失真其中一种结果,因此文中列出两个图表,分别用来显示噪声结果(图12)和失真结果(图13)。

图12. Virtual Eval中的AD9680 FFT仿真—噪声结果。

图13. Virtual Eval中的AD9680 FFT仿真—失真结果。

Virtual Eval中可显示许多性能参数。该工具可提供基频镜像的位置以及各谐波位置,这对于频率规划非常方便。还允许用户查看基频镜像或任何谐波信号音是否出现在所需的输出频谱内,从而使得频率规划更轻松。Virtual Eval仿真得出SNR值为71.953 dBFS,SFDR为69.165 dBc。但需考虑一下,基频镜像通常不会出现在输出频谱中,如果我们消除杂散信号,那么SFDR为89.978 dB(若参考的输入功率是–1 dBFS,则为88.978 dBc)。

图14. AD9680 FFT测量结果。

Virtual Eval仿真器在计算SNR时不包括基频镜像。请务必调整VisualAnalog™中的设置,忽略测量结果中的基频镜像,以得到正确的SNR。该方法适用于对基频镜像不在所需频带内的情况进行频率规划。SNR的实测结果为71.602 dBFS,非常接近于Virtual Eval中的仿真结果71.953 dBFS。与之类似,实测的SFDR为91.831 dBc,非常接近于仿真结果88.978 dBc。

Virtual Eval能够准确地预测硬件行为,表现极为出色。您只需一把 舒适的椅子,一杯热茶或咖啡,即可预测出器件行为。特别是对于带有DDC的ADC(如AD9680),Virtual Eval能够很好地仿真ADC的各种性能(包括镜像和谐波),便于用户进行频率规划,并且尽可能将这些干扰信号保持在频带外。随着载波聚合和直接射频采样得到越来越多的应用,工具箱内备有类似于Virtual Eval的工具将会使您的工作得心应手。此类工具能够准确地预测ADC性能,帮助系统设计人员为某些应用(如通信系统、军事/航空航天雷达系统以及许多其他类型的应用)设计进行适当的频率规划。建议您充分利用ADI新一代ADC器件的数字信号处理功能优势。同时建议您使用Virtual Eval来规划您的下一个设计,提前构想预期性能。

作者

Jonathan Harris是ADI公司高速转换器部(北卡罗来纳州格林斯博罗)的一名产品应用工程师。他担任支持射频行业产品的应用工程师已超过7年。他从奥本大学和北卡罗来纳大学夏洛特分校分别获得电子工程硕士(MSEE)学位和电子工程学士(BSEE)学位。

在本文第一部分 《数字下变频器的发展和更新——第一部分》, 中,我们讨论了在更高频率的RF频段中进行频率采样的行业趋势以及数字下变频器(DDC)如何支持此类无线电架构。文中对AD9680系列产品所含DDC的几个技术方面进行了探讨。其中一个方面就是,更高的输入采样带宽允许无线电架构在更高的RF频率下直接采样,并将输入信号直接转换为基带。DDC可使RF采样ADC对此类信号进行数字化,而无需处理大量的数据吞吐量。DDC中的调谐和抽取滤波机制可以用来调整输入频带和滤除干扰频率。在本部分中我们将进一步分析抽取滤波,并将其应用于第一部分所讨论的示例。此外,我们将讨论Virtual Eval,该产品在改良的新型软件仿真工具中融入了ADIsimADC引擎技术。Virtual Eval将用于验证仿真结果与实测数据的匹配程度。

在第一部分中我们分析了一个示例,利用DDC中的NCO和抽取滤波来观察DDC中频率折叠和转换效果的影响。现在我们进一步分析抽取滤波,以及ADC混叠如何影响抽取滤波的有效响应。同样,我们将以AD9680 为例进行讨论。我们对抽取滤波器响应进行了归一化,使其便于查看和理解,并且可应用于每个速度等级。抽取滤波器响应仅与采样速率成比例。本文的滤波器响应图并没有确切具体地提供插入损耗与频率之间的关系,而是形象地描绘了该滤波器的近似响应情况。通过这些示例可以更好地了解抽取滤波器响应,以便大致了解滤波器通带和阻带所处的位置。

如前所述,AD9680具有四个DDC,各含一个NCO,多达四个级联的半带(HB)滤波器(亦称为抽取滤波器),一个可选性6 dB增益模块以及一个可选复数转实数模块,如图1所示。我们曾在第一部分讨论过,信号首先通过NCO,使输入信号音的频率偏移,然后通过抽取模块,也可选择通过增益模块,以及选择通过复数转实数模块。

图1. AD9680中的DDC信号处理模块。

首先我们将讨论在AD9680中使能复数转实数模块时DDC抽取滤波器的情况。这意味着DDC将配置为接受实数输入和产生实数输出。在AD9680中,复数转实数模块会使输入频率自动向上偏移fS/4。图2所示为HB1滤波器的低通响应。这是HB1响应,显示了实数和复数域响应部分。若要了解滤波器的实际运作,首先要观察滤波器在实数域和复数域内的基本响应,从而可以观察到低通响应。HB1滤波器有一个通带占实数奈奎斯特区的38.5%。还有一个阻带也占实数奈奎斯特区的38.5%,其过渡带占剩余的23%。同样,在复数域,通带和阻带各占复数奈奎斯特区的38.5%(共77%),而过渡带占剩余的23%。如图2所示,滤波器是位于实数域和复数域之间的一个镜像。

图2. HB1滤波器响应—实数域和复数域响应。

现在我们可以观察到,通过使能复数转实数模块将DDC置为实数模式时会发生什么情况。使能复数转实数模块会导致频域中出现fS/4的偏移。如图3所示,可看到频移和产生的滤波器响应。注意该滤波器响应的实线和虚线。实线和阴影区表示这是fS/4频移后新的滤波器响应(产生的滤波器响应不能跨越奈奎斯特边界)。虚线用来显示若未进入奈奎斯特边界本该存在的滤波器响应。

图3. HB1滤波器响应—DDC实数模式(复数转实数模块使能)。

注意,在图2和图3中,HB1滤波器的带宽保持不变。两者之间的区别是fS/4频移和第一奈奎斯特区内的中心频率。然而应注意,在图2中,我们将奈奎斯特区的38.5%用于信号的实数部分,另38.5%用于信号的复数部分。在图3中,复数转实数模块已使能,奈奎斯特区的77%均用于实数信号,而复数域已被丢弃。除了fS/4频移之外,过滤器响应保持不变。还应注意,该转换的一个结果是:抽取率此时等于1。有效采样速率仍然是fS,但奈奎斯特区内仅有77%的可用带宽,而不是整个奈奎斯特区均可用。这意味着,当HB1滤波器和复数转实数模块使能时,抽取率等于1(更多信息请参阅AD9680数据手册)。

下面我们来看看滤波器在不同抽取率(即,使能多个半带滤波器)的响应,以及ADC输入频率混叠对有效的抽取滤波器响应有何影响。图4中的蓝色实线表示HB1的实际频率响应。虚线则表示因ADC混叠效应所产生的HB1有效混叠响应。由于第二、第三、第四……奈奎斯特区的输入频率实际上混叠到ADC的第一奈奎斯特区,因此HB1滤波器响应有效地混叠到这些奈奎斯特区。例如,一个驻留在3fS/4的信号将混叠到第一奈奎斯特区的fS/4。HB1滤波器响应仅驻留在第一奈奎斯特区,并且是ADC混叠导致了HB1的有效响应看起来像是混叠到其他奈奎斯特区,理解这一点非常重要。

图4. ADC混叠导致的HB1有效滤波器响应。

现在我们来讨论HB1 + HB2使能的情况。其结果会使抽取率为2。这里的蓝色实线也表示HB1 + HB2滤波器的实际频率响应。滤波器通带的中心频率仍是fS/4。HB1 + HB2使能将导致可用带宽占奈奎斯特区的38.5%。同样,请注意ADC的混叠效应及其对HB1 + HB2滤波器组合的影响。一个出现在7fS/8的信号将混叠到第一奈奎斯特区的fS/8。类似的,一个5fS/8的信号将混叠到第一奈奎斯特区的3fS/8。这些复数转实数模块使能的示例可以从含有HB1 + HB2很方便地扩展到含有HB3和HB4滤波器二者或其中之一。注意,当DDC使能时,HB1滤波器不可旁通,而HB2、HB3和HB4滤波器可选择使能。

图5. ADC混叠导致的HB1+HB2有效滤波器响应(抽取率=2)。

我们已经讨论了抽取滤波器使能时的实数工作模式,现在我们可以探讨DDC的复数工作模式。仍以AD9680为例。与DDC的实数工作模式类似,这里将展示归一化的抽取滤波器响应。同样,示例滤波器响应图中没有确切表明插入损耗与频率之间的具体关系,而是形象地描绘了该滤波器的近似响应。这样做是为了便于更好地了解ADC混叠如何影响滤波器响应。

在复数模式中使用DDC时,它配置为具有一个复数输出,由实数和复数频域(通常称为I和Q)构成。回顾图2可知,HB1滤波器具有低通响应,通带为实数奈奎斯特区的38.5%。还有一个阻带也占实数奈奎斯特区的38.5%,其过渡带占剩余的23%。同样,在复数域,通带和阻带各占复数奈奎斯特区的38.5%(共77%),而过渡带占剩余的23%。

当HB1滤波器使能,在复数输出模式下操作DDC时,抽取率等于二,输出采样速率为输入采样时钟的二分之一。扩展图2中的曲线可显示出图6所示的ADC混叠的影响。其中的蓝色实线表示实际滤波器响应,蓝色虚线则表示因ADC混叠效应所产生的滤波器的有效混叠响应。7fS/8的输入信号将混叠到第一奈奎斯特区的fS/8,使其位于HB1滤波器的通带内。同一信号的复数镜像驻留于–7fS/8,并将在复数域混叠到–fS/8,使其位于复数域的HB1滤波器通带内。

图6. ADC混叠导致的HB1有效滤波器响应(抽取率=2)—复数。

接下来,我们将讨论HB1 + HB2使能的情况,如图7所示。其结果会使得每个I和Q输出的抽取率为4。这里的蓝色实线也表示HB1 +HB2滤波器的实际频率响应。HB1 + HB2滤波器同时使能将导致每个实数和复数域中的可用带宽为抽取奈奎斯特区的38.5%(fS/4的38.5%,其中fS为输入采样时钟)。请注意ADC的混叠效应及其对HB1 + HB2滤波器组合的影响。一个出现在15fS/16的信号将混叠到第一奈奎斯特区的fS/16。该信号在复数域的–15fS/16有一个复数镜像,并将混叠到复数域第一奈奎斯特区的–fS/16。同理,这些示例也可以扩展到HB3和HB4均使能的情况。本文中并未显示这些内容,但根据图7所示的HB1 + HB2响应很容易推算出来。

图7. ADC混叠导致的HB1 + HB2有效滤波器响应(抽取率=4)—复数。

看到所有这些抽取滤波器响应,您的脑海里可能会有这样的问题:"我们为什么要抽取?"以及"这样做有什么好处?"不同的应用具有不同的要求,而这些要求可以从ADC输出数据的抽取中获利。其中一个原因是要增大RF频带中某段狭窄频带上的信噪比。另一个原因是为了使处理带宽更小,这样可使JESD204B接口的输出通道速率降低,从而便于使用低成本的FPGA。通过使用全部四个抽取滤波器,DDC可实现处理增益,并使SNR改善达10 dB。在表1中,我们可以看到当DDC工作于实数模式和复数模式时,不同的抽取滤波器选择所提供的可用带宽、抽取率、输出采样速率和理想SNR改善情况。

表1. DDC滤波器特性(AD9680)

关于DDC工作模式的讨论有助于深入了解AD9680中抽取滤波器的实数工作模式和复数工作模式。采用抽取滤波可提供多个好处。DDC可工作于实数模式或复数模式,允许用户根据特定应用的需求采用不同的接收器拓扑。结合第一部分所述的内容,还有助于探讨采用AD9680的一个真实示例。该示例将综合实测数据和Virtual Eval中导出的仿真数据,以便于比较结果。

在此例中我们将采用在第一部分中曾使用的相同条件。输入采样 速率为491.52 MSPS,输入频率为150.1 MHz。NCO频率为155 MHz, 抽取率设为4(由于NCO分辨率,实际NCO频率为154.94 MHz)。因 此,输出采样速率为122.88 MSPS。由于DDC进行复数混频,因此 分析中包含复数频域。注意,图8中添加了抽取滤波器的响应, 以深紫色曲线表示。

图8. 信号通过DDC信号处理模块—抽取滤波。

NCO偏移后的频谱:

基频从+150.1 MHz下移至–4.94 MHz。

基频镜像从–150.1 MHz开始偏移,并绕回至+186.48 MHz。

二次谐波从191.32 MHz下移至36.38 MHz。

三次谐波从+41.22 MHz下移至–113.72 MHz。

2倍抽取后的频谱:

基频位于–4.94 MHz。

基频镜像向下转换至–59.28 MHz,并由HB1抽取滤波器衰减。

二次谐波位于36.38 MHz。

三次谐波由HB1抽取滤波器衰减。

4倍抽取后的频谱:

基频位于–4.94 MHz。

基频镜像位于–59.28 MHz,并由HB2抽取滤波器衰减。

二次谐波位于-36.38 MHz,并由HB2抽取滤波器衰减。

三次谐波经过滤波,基本由HB2抽取滤波器完全消除。

AD9680-500的实测结果如图9所示。基频位于–4.94 MHz。基频镜像位于–59.28 MHz,幅度为–67.112 dBFS,意味着镜像衰减了大约66 dB。二次谐波位于36.38 MHz,并衰减了大约10至15 dB。三次谐波经过充分滤波,实测结果不高于噪底。

图9. 信号经过DDC后的FFT复数输出(NCO = 155 MHz,4倍抽取)。

现在可使用Virtual Eval来观察仿真结果与实测结果的对比情况。首先,从网站上打开该工具,并选择要仿真的ADC(见图10)。Virtual Eval工具在ADI网站的Virtual Eval下。Virtual Eval中的AD9680模型含有一项新开发的功能,允许用户仿真不同的ADC速度等级。由于此示例使用了AD9680-500,所以该功能很重要。Virtual Eval加载后,首先提示选择产品类别和产品。注意,Virtual Eval中不仅涵盖高速ADC,而且包含精密ADC、高速DAC以及集成/专用转换器这些产品。

图10. Virtual Eval中的产品类别和选型。

从产品列表中选择AD9680。这将会打开AD9680仿真的主页。VirtualEval中的AD9680模型还含有一个框图,详细介绍了ADC模拟功能和数字功能的内部配置。该框图与AD9680数据手册中的框图相同。在此页面的左侧下拉菜单中选择所需的速度等级。对于本例,速度等级选择500 MHz,如图11所示。

图11. Virtual Eval中的AD9680速度等级选择和框图。

然后,为了执行FFT仿真,必须设定输入条件(见图12)。回顾一下,本例的测试条件包含一个491.52 MHz的时钟速率和一个150MHz的输入频率。DDC使能,NCO频率设为155 MHz,ADC输入设为Real(实数),复数转实数模块(C2R)为Disabled(禁用),DDC抽取率设为Four(4),DDC中的6 dB增益为Enabled(使能)。这意味着DDC将设为具有实数输入信号和复数输出信号,并且抽取率为4。DDC中的6 dB增益使能是为了补偿DDC中混频处理所导致的6 dB损耗。Virtual Eval每次只能显示噪声或失真其中一种结果,因此文中列出两个图表,分别用来显示噪声结果(图12)和失真结果(图13)。

图12. Virtual Eval中的AD9680 FFT仿真—噪声结果。

图13. Virtual Eval中的AD9680 FFT仿真—失真结果。

Virtual Eval中可显示许多性能参数。该工具可提供基频镜像的位置以及各谐波位置,这对于频率规划非常方便。还允许用户查看基频镜像或任何谐波信号音是否出现在所需的输出频谱内,从而使得频率规划更轻松。Virtual Eval仿真得出SNR值为71.953 dBFS,SFDR为69.165 dBc。但需考虑一下,基频镜像通常不会出现在输出频谱中,如果我们消除杂散信号,那么SFDR为89.978 dB(若参考的输入功率是–1 dBFS,则为88.978 dBc)。

图14. AD9680 FFT测量结果。

Virtual Eval仿真器在计算SNR时不包括基频镜像。请务必调整VisualAnalog™中的设置,忽略测量结果中的基频镜像,以得到正确的SNR。该方法适用于对基频镜像不在所需频带内的情况进行频率规划。SNR的实测结果为71.602 dBFS,非常接近于Virtual Eval中的仿真结果71.953 dBFS。与之类似,实测的SFDR为91.831 dBc,非常接近于仿真结果88.978 dBc。

Virtual Eval能够准确地预测硬件行为,表现极为出色。您只需一把 舒适的椅子,一杯热茶或咖啡,即可预测出器件行为。特别是对于带有DDC的ADC(如AD9680),Virtual Eval能够很好地仿真ADC的各种性能(包括镜像和谐波),便于用户进行频率规划,并且尽可能将这些干扰信号保持在频带外。随着载波聚合和直接射频采样得到越来越多的应用,工具箱内备有类似于Virtual Eval的工具将会使您的工作得心应手。此类工具能够准确地预测ADC性能,帮助系统设计人员为某些应用(如通信系统、军事/航空航天雷达系统以及许多其他类型的应用)设计进行适当的频率规划。建议您充分利用ADI新一代ADC器件的数字信号处理功能优势。同时建议您使用Virtual Eval来规划您的下一个设计,提前构想预期性能。

作者

Jonathan Harris是ADI公司高速转换器部(北卡罗来纳州格林斯博罗)的一名产品应用工程师。他担任支持射频行业产品的应用工程师已超过7年。他从奥本大学和北卡罗来纳大学夏洛特分校分别获得电子工程硕士(MSEE)学位和电子工程学士(BSEE)学位。

无线电 ADC 仿真 ADI 滤波器 FPGA DAC 射频 电子 相关文章:

- 软件无线电的电磁兼容分析(02-26)

- 对信息技术设备的无线电骚扰管理方法的研究(02-27)

- 雷达信号及其监测研究(03-02)

- 基于认知无线电技术的IEEE 802.22(10-02)

- 4G移动通信关键技术及特征(03-09)

- 无线电频率资源的合理配置(08-16)