使用HSPICE精确分析多千兆系统

时间:12-17

来源:互联网

点击:

通过一个3200Mbps LPDDR4接口将一个应用处理器连接至DRAM芯片,其难度不亚于2600MHz 4G LTE天线的布线工作。虽然RF前端采用了陶瓷封装,并在各个抗电磁干扰模块中进行了精心布线,但数字信号会穿过球栅阵列封装和高密度小型印刷电路板(PCB),从而使它们更容易受到高频影响。随着数据速率增至甚至超出千兆范围,PCB印制线不能再被视为简单的导体。铜印制线的寄生电阻、电容和电感使其成为一条传输线,从而产生数字设计中通常不去考虑的各类高频效应。例如,由于集肤效应,信号的高频成分要比低频成分经历更大的衰减,从而导致信号失真。平行铜印制线之间的电感和电容会导致串扰,而大开关电流会导致接地反弹。误码率(BER)将会上升,因为更多比特将被解析为“0”或“1”。因此,为了确保信号完整性,需要对PCB印制线的传输线效应以及封装、连接器和电缆的频率响应进行全面分析。通过减少PCB原型设计与测量的大量迭代次数,精准的PCB级SPICE分析可节省时间和金钱。

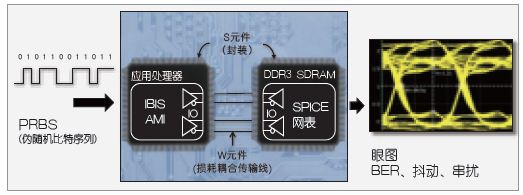

图1显示了一个内存接口,它是多千兆芯片间通信的一个典型例子。相同的概念也适用于USB 3.0、HDMI、多千兆Ethernet设备等高速串行I/O。通信通道由芯片的I/O模型、封装、连接器及电缆的散射参数(S参数)模型以及印制线的损耗耦合传输线模型构成。I/O模型由芯片厂商提供。简单的I/O缓存器可以用IBIS模型精确表示。配备有源预加重和均衡功能的更加复杂的I/O电路通常采用经过加密的晶体管级HSPICE网表的形式,或者采用源于晶体管级表示的IBIS-AMI模型。作为晶体管级仿真的黄金参考模型,HSPICE使用经过晶圆厂认证的晶体管模型提供最为精确的I/O电路行为。不仅如此,大多数芯片厂商使用HSPICE来验证他们的IBIS和IBIS-AMI模型。因此,在电路板一级使用HSPICE最符合芯片厂商的意图。对于IBIS-AMI模型而言,HSPICE具备独特优势,除了逐比特和统计眼图模式之外,它还能在真正的瞬态模式下模拟这些模型。

图1:用于信号完整性分析的典型系统配置。

PCB印制线的损耗耦合传输线可以采用多种方法提取,其中最简单的方法就是使用HSPICE W元件。W元件读入PCB的属性和平行印制线的尺寸,然后使用一个内置的2D解算器提取传输线响应。该模型能够精确表示与频率有关的损耗和耦合,而且不限制耦合线路的数量,可确保系统的被动性和因果关系。大多数PCB布局工具能够提取印制线几何图形,并在HSPICE网表中自动生成W元件模型。第三方准静态2.5D场解算器也可用于生成PCB印制线的宽带模型。取决于所使用的场解算器,这些模型能够以RLGC表的形式被插入到W元件中。对于关键布局,全波长解算器可用于提取PCB印制线的频率响应,即S参数,后者也可用作W元件的输入。

封装、连接器及电缆的S参数模型由组件厂商提供,或由一个网络分析仪测量,或由一个3D电磁场解算器提取。无论哪种情况,S参数模型都能提供一个可靠的组件线性表示,将其分布式本质以及任何与频率相关的行为考虑在内。通过观察史密斯图上的S参数,可以深入了解这些分布式系统,超过使用电路图中的集总元件所能获取的信息。但是,这里存在一个挑战。S参数是频率域模型,原本是为RF和微波设备而发明的,而数字多千兆系统的信号完整性分析主要是在时间域中进行的。HSPICE S元件采用最先进的自动有理函数模型生成技术克服了这个挑战。此外,HSPICE通过部署多时延增强型有理函数模型,捕获长达数米的数据线(如HDMI线)的复杂高频行为。HSPICE利用现代处理器中的并行计算技术精确高速地模拟大型(500端口以上)S参数模型。除了在电路仿真中使用S参数以外,HSPICE还支持多端口线性网络分析(.LIN),它可以从任意电路类型提取S参数。

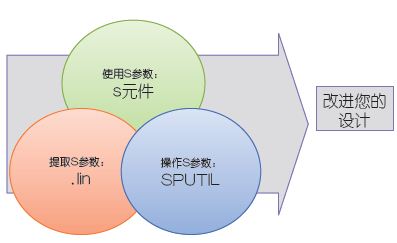

图2:与S参数打交道不仅仅是进行瞬态分析。

S参数模型的灵活性和可靠性有时会因某些S参数质量欠缺而下降。低质量的S参数模型有可能产生较差的仿真结果。质量问题包括但不限于:违反被动性、粗糙的频率抽样和较窄的频率带宽。例如,某个S参数模型的起始频率有可能很高,以至于无法捕获低频瞬态行为;或者其结束频率有可能很低,以至于无法捕获数字转换的高频成分。HSPICE包含一个独立的S参数实用程序,它能够采用不同的方法操作S参数,以确保S参数模型的质量。图2显示了HSPICE如何整合采用多端口线性网络分析(.LIN)的S参数提取、采用瞬态分析(.TRAN)的S参数仿真以及采用S参数实用程序(SPUTIL)的S参数质量保证。

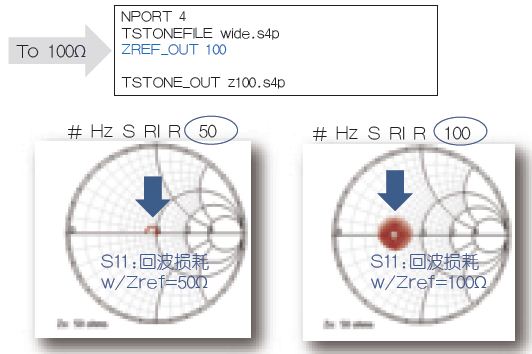

图3:使用HSPICE S参数实用程序(SPUTIL)检查阻抗匹配。

SPUTIL提供众多便捷的S参数操作技术,例如,合并多个数据文件、被动性检查或执行、利用灵活的频点规范重新采样、文件格式转换等。例如,阻抗匹配是高速通道设计的一个重要要求。测试阻抗匹配的最快方法就是使用不同的参考阻抗观察S11。如图3所示,SPUTIL提供一种便捷的方法,使用一个简单脚本转换某个S参数集的参考阻抗。然后,通过观察史密斯图上的S11图找出最小的S11值,从而为设计通道终端阻抗提供一个良好的起点。

对于信号完整性分析中所使用的各种组件和模型的讨论到此结束,现在开始讨论各种分析技术。眼图分析技术被广泛用于评估高速通信通道。眼图将一个长数字比特序列的单位时间间隔叠加为一个紧凑形式,便于人们对系统进行皮秒级观察。生成被测目标系统的一个眼图、检查眼图开口和测量作为累计概率的BER是通道合规测试的关键组成部分。

HSPICE提供不同的技术,用于分析不同仿真速度和精度的眼图。评估多千兆系统的BER要求分析数百万个单位时间间隔。对这些长比特流进行瞬态分析需要耗费几个小时的时间,并产生很大的数据文件。可能需要数千次仿真才能覆盖通道优化设计。在HSPICE中生成逐比特和统计眼图将仿真时间从几个小时缩短至几秒钟,从而大幅提高通道设计效率。

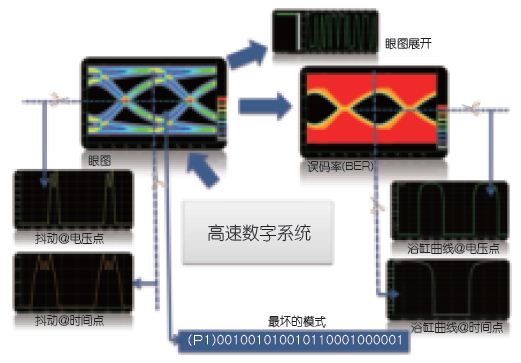

HSPICE采用精确的瞬态分析计算出众多小比特模式的脉冲响应,然后使用统计方法迅速生成眼图,即概率密度函数(PDF)图,将所有可能的比特模式考虑在内,如图4所示。HSPICE通过观察眼图的垂直和水平横截面,自动提取抖动曲线。此外,HSPICE还根据PDF眼图自动生成误码率(BER)图。然后,可以通过提取BER的截面图观察浴缸曲线。HSPICE还捕获特定时刻的最短比特模式,它再现了最里面—换句话说“最坏的”—眼图碎片。在接下来的短瞬态分析中使用这个最坏的比特模式,就可以分析出眼图闭合的原因,然后改进设计。HSPICE能够提取具体比特位置的时间域波形,该技术可用于验证自适应均衡器设计。

图4:HSPICE统计眼图分析。

逐比特眼图分析采用一种快速瞬态技术为特定的比特模式生成眼图,而且所需时间仅为瞬态分析的几分之一,对于通道设计非常有用。瞬态分析可为签核提供最精确的眼图。在时间域瞬态分析中HSPICE支持所有类型的I/O模型,其中包括算法模型(IBIS-AMI)以及与频率有关的元件。并行计算技术被用于加快超长比特序列的仿真速度,同时又不牺牲精确度。

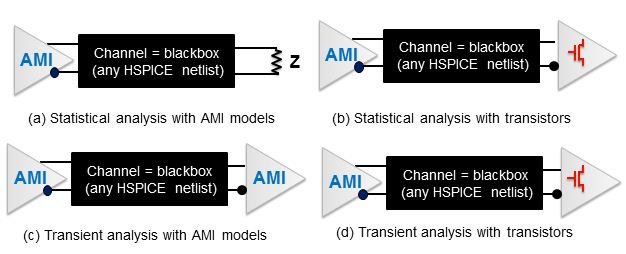

HSPICE具备一种独特能力,能够混用和匹配各类分析技术和模型,以便最好地匹配每一个通道设计和合规测试阶段。如图5所示,HSPICE将通道视为一个黑盒子,让用户能够放入任意组合的有源和无源设备。HSPICE还支持各种不同的发射器和接收器表示。例如,发射器可以是一个晶体管级I/O电路,而接收器可以是一个IBIS-AMI模型,反之亦然。在早期设计阶段,可以采用快速统计眼图分析评估与模式无关的发射器加重。对于此类分析,IBIS-AMI模型在发射器侧使用,只是为了使接收器成为一个理想化的接收器终端。随着设计的不断演进,可以采用逐比特仿真将理想化的接收器替换为一个算法模型,以便测试自适应均衡器如何通过调整其参数实现最大的眼图开口。然后,从逐比特分析切换至全面的瞬态分析,可以捕获通道中可能出现的任何非线性效应。在最后的验证阶段,很有可能使用到发射器和接收器缓存的全晶体管表示。HSPICE能够在同一个测试台上运行所有这些分析。

图5:在统计、逐比特和瞬态眼图分析中结合使用AMI和晶体管级模型。

LTE 电路 PCB 电阻 电容 电感 电流 连接器 PIC USB HDMI 仿真 电路图 相关文章:

- 3G LTE简介(01-30)

- LTE——3G技术的未来发展(02-20)

- 3GPP LTE/SAE网络体系结构和标准化进展(04-14)

- TD向LTE TDD平滑演进(04-21)

- LTE技术热点分析(09-19)

- UMB、LTE、WiMAX谁是移动通信发展方向(09-30)