基于MRF24J40的IEEE802154无线收发器电路方案设计

时间:10-25

来源:互联网

点击:

1、收发器芯片MRF24J40

IEEE802.15.4 无线收发器MRF24J40芯片内部包含有SPI接口、控制寄存器、MAC模块、PHY驱动器四个主要的功能模块,支持 IEEE802.15.4,MiWiTM,ZigBee等协议,工作在2.405~2.48 GHz ISM频段,接收灵敏度为-91 dBm,最大输入电平为+5 dBm,输出功率为+0 dBm,功率控制范围为38.75 dB,集成有20 MHz和32.768 kHz主控振荡器,MAC/基带部分采用硬件CSMA-CA结构,自动ACK6和FCS检测,CTR、CCM和CBC-MAC模式采用硬件加密(AES- 128),电源电压范围为2.4~3.6 V,接收模式电流消耗为18 mA,发射模式电流消耗为22 mA,睡眠模式电流消耗为2μA。

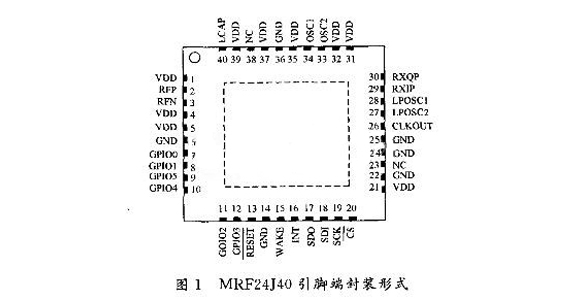

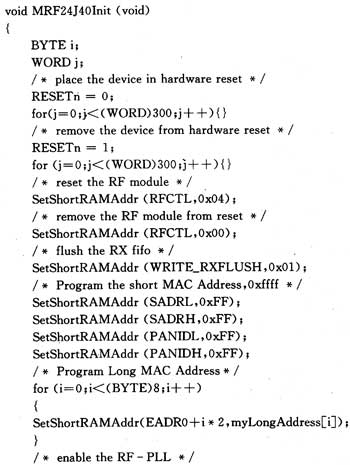

MRF24J40 采用6 mm×6 mm QFN-40封装,引脚端封装形式如图1所示。图中:引脚端RFP和RFN分别为芯片的RF差分输入/输出正端和负端,两者都是模拟输入/输出端口,与系统天线相连接;VDD为电源电压输入引脚端,每个电源电压输入引脚端都必须连接一个电源去耦电容;GND为接地引脚端,必须低阻抗的连接到电路的接地板;GPIOO~GPIO5是通用数字I/O口,其中GPIO0也被用来作为外部功率放大器使能控制,GPIO1和GPIO2也被用来作为外部TX/RX 开关控制;RESET为复位引脚端,低电平有效;WAKE为外部唤醒触发输入端;INT为到微控制器的中断引脚端;SDO,SDI,SCK和CS是 MRF24J40的SPI接口输入输出引脚端,其中SDO是MRF24J40的串行数据输出,SDI是MRF24J40的串行接口数据输入,SCK是串行接口的时钟,CS是串行接口使能控制引脚端;LPOSC1和LPOSC2为32 kHz晶振输入正端和负端;OSC1和OSC2为20 MHz晶振输入正端和负端;CLKOUT为20/10/5/2.5 MHz时钟输出端;LCAP引脚端用来连接一个180 pF的PLL环路滤波器电容;XIP和RXQP为接收I通道和Q通道输出正端。

2、MRF24J40构成的IEEE802.15.4无线收发电路

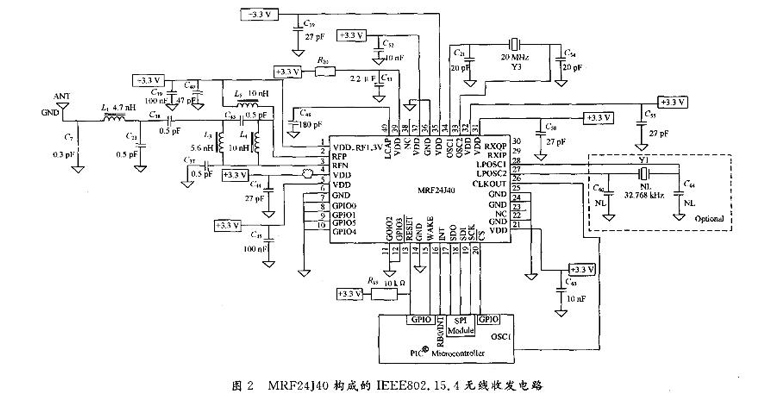

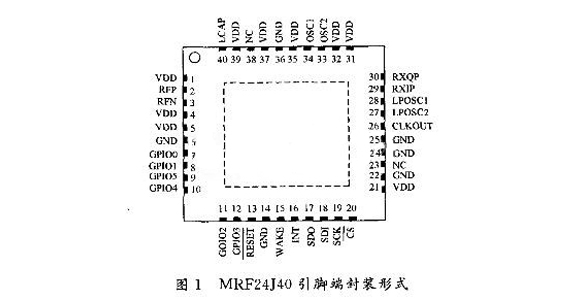

MRF24J40 构成的IEEE802.15.4无线收发电路如图2所示,各电源电压引脚端根据需要分别连接了27 pF,10 nF,100 nF,2.2μF去耦电容器。RF差分输入/输出正端RFP和负端RFN通过L3,L4,G37和C43组成平衡一不平衡变换电路,将MRF24J40的 RF差分输入/输出形式转换为单端输入/输出形式。L1,C23和C33构成π型匹配电路,使平衡一不平衡变换电路阻抗与天线的阻抗相匹配。LPOSC1 和LPOSC2引脚端连接32 kHz晶振和电容,构成32 kHz时钟振荡器电路。OSC1和OSC2引脚端连接20 MHz晶振和电容,构成20 MHz时钟振荡器电路。产生的时钟信号作为芯片内部时钟信号,并可以提供给外部的微控制器使用。

引脚端RESET,WAKE,INT,SDO,SDI,SCK,CS连接到微控制器,在微控制器的控制下完成数据的收发。

3、印制电路板(PCB)设计

3.1 PCB设计基本要求

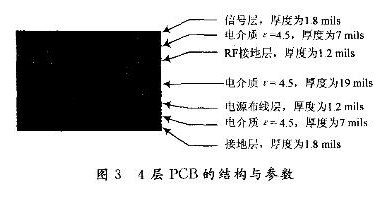

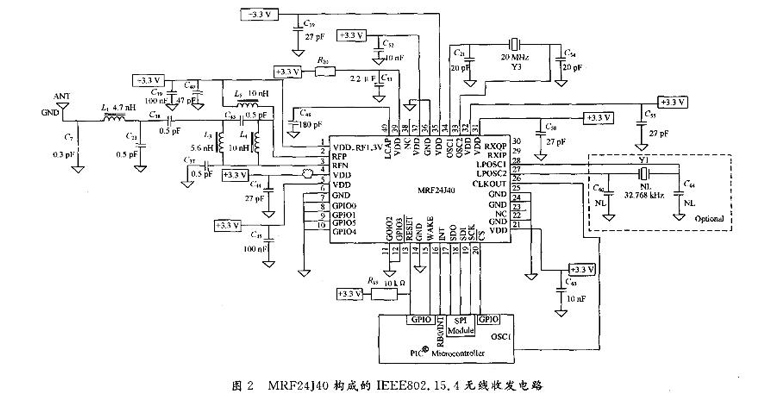

MRF24J40构成的IEEE802.15.4无线收发电路工作频率范围为2.405~2.48 GHz,对PCB的设计有十分高的要求。PCB采用4层结构,如图3所示,分别为信号层,RF接地层,电源布线层和接地层,采用FR4材料。

保持PCB的厚度是十分重要的,任何尺寸的改变将会影响天线的性能或者微带线的特性阻抗。信号层的50 Ω微带线为12 mil(1 mil="0".025 4 mm)。应避免微带线的长度超过2.5 cm,当线长超过2.5 cm,接近电路板的工作频率1/4波长时,导线可以象天线一样工作。除天线外,导线应避免尖锐的转角,以减少EMI的产生。当周期信号和时钟进行转换时,数字线容易产生噪声,布线时应避免使射频信号线接近任何数字线。电源必须以星状拓扑结构形式分配给每个电源引脚端,采用低自感系数的电容器进行退耦。退耦电容器可以采用15~27 pF和100 nF进行组合。还有低电阻电解电容必须放置在每个引脚上来适当去除耦合噪声。电感器的自谐振频率至少应该是工作频率的两倍。PCB地线设计尽可能粗,甚至大面积接地,除了天线部分、元器件引线、电源走线、信号线之外,其余部分均可作为地线。

3.2 PCB天线设计

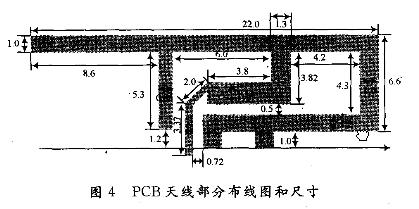

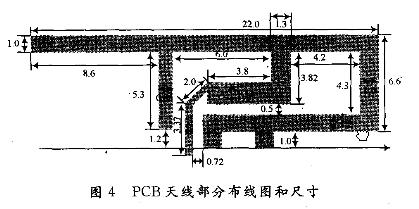

RF差分输入/输出正端RFP和负端RFN连接平衡-不平衡变换电路和兀型阻抗匹配电路,推荐的PCB天线部分布线图和尺寸(单位:mm)如图4所示。

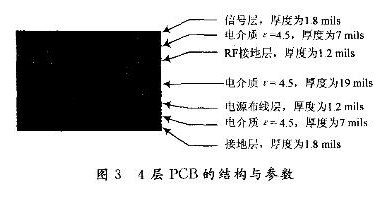

4、MRF24J40的初始化程序

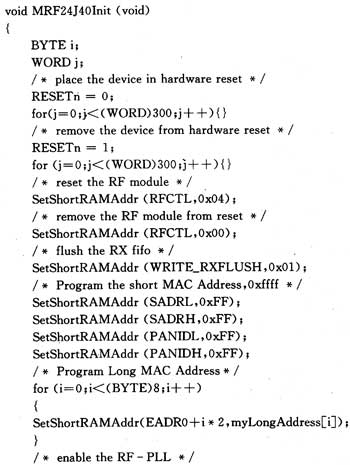

由MRF24J40构成的IEEE802.15.4无线收发电路必须在微控制器的控制下,才能够在IEEE802.15.4网络中应用。电路中进行数据的发送和接收前,必须完成器件的初始化设置。MRF24J40的初始化程序如下所示:

5、结术语

采用MRF24J40构成的IEEE802.15.4无线收发器电路,支持MiWiTM,ZigBee等协议,为IEEE802.5.15.4MAC和 PHY物理层提供硬件层,工作在2.405~2.48 GHzISM频段,接收灵敏度为-91 dBm,发射输出功率为+0 dBm,采用4线式SPI与微控制器接口,适合家居自动化、工业自动化等低数据速率传输的应用。作为“全自动哮喘诊断仪”的无线数据传输通道,效果良好。

IEEE802.15.4 无线收发器MRF24J40芯片内部包含有SPI接口、控制寄存器、MAC模块、PHY驱动器四个主要的功能模块,支持 IEEE802.15.4,MiWiTM,ZigBee等协议,工作在2.405~2.48 GHz ISM频段,接收灵敏度为-91 dBm,最大输入电平为+5 dBm,输出功率为+0 dBm,功率控制范围为38.75 dB,集成有20 MHz和32.768 kHz主控振荡器,MAC/基带部分采用硬件CSMA-CA结构,自动ACK6和FCS检测,CTR、CCM和CBC-MAC模式采用硬件加密(AES- 128),电源电压范围为2.4~3.6 V,接收模式电流消耗为18 mA,发射模式电流消耗为22 mA,睡眠模式电流消耗为2μA。

MRF24J40 采用6 mm×6 mm QFN-40封装,引脚端封装形式如图1所示。图中:引脚端RFP和RFN分别为芯片的RF差分输入/输出正端和负端,两者都是模拟输入/输出端口,与系统天线相连接;VDD为电源电压输入引脚端,每个电源电压输入引脚端都必须连接一个电源去耦电容;GND为接地引脚端,必须低阻抗的连接到电路的接地板;GPIOO~GPIO5是通用数字I/O口,其中GPIO0也被用来作为外部功率放大器使能控制,GPIO1和GPIO2也被用来作为外部TX/RX 开关控制;RESET为复位引脚端,低电平有效;WAKE为外部唤醒触发输入端;INT为到微控制器的中断引脚端;SDO,SDI,SCK和CS是 MRF24J40的SPI接口输入输出引脚端,其中SDO是MRF24J40的串行数据输出,SDI是MRF24J40的串行接口数据输入,SCK是串行接口的时钟,CS是串行接口使能控制引脚端;LPOSC1和LPOSC2为32 kHz晶振输入正端和负端;OSC1和OSC2为20 MHz晶振输入正端和负端;CLKOUT为20/10/5/2.5 MHz时钟输出端;LCAP引脚端用来连接一个180 pF的PLL环路滤波器电容;XIP和RXQP为接收I通道和Q通道输出正端。

2、MRF24J40构成的IEEE802.15.4无线收发电路

MRF24J40 构成的IEEE802.15.4无线收发电路如图2所示,各电源电压引脚端根据需要分别连接了27 pF,10 nF,100 nF,2.2μF去耦电容器。RF差分输入/输出正端RFP和负端RFN通过L3,L4,G37和C43组成平衡一不平衡变换电路,将MRF24J40的 RF差分输入/输出形式转换为单端输入/输出形式。L1,C23和C33构成π型匹配电路,使平衡一不平衡变换电路阻抗与天线的阻抗相匹配。LPOSC1 和LPOSC2引脚端连接32 kHz晶振和电容,构成32 kHz时钟振荡器电路。OSC1和OSC2引脚端连接20 MHz晶振和电容,构成20 MHz时钟振荡器电路。产生的时钟信号作为芯片内部时钟信号,并可以提供给外部的微控制器使用。

引脚端RESET,WAKE,INT,SDO,SDI,SCK,CS连接到微控制器,在微控制器的控制下完成数据的收发。

3、印制电路板(PCB)设计

3.1 PCB设计基本要求

MRF24J40构成的IEEE802.15.4无线收发电路工作频率范围为2.405~2.48 GHz,对PCB的设计有十分高的要求。PCB采用4层结构,如图3所示,分别为信号层,RF接地层,电源布线层和接地层,采用FR4材料。

保持PCB的厚度是十分重要的,任何尺寸的改变将会影响天线的性能或者微带线的特性阻抗。信号层的50 Ω微带线为12 mil(1 mil="0".025 4 mm)。应避免微带线的长度超过2.5 cm,当线长超过2.5 cm,接近电路板的工作频率1/4波长时,导线可以象天线一样工作。除天线外,导线应避免尖锐的转角,以减少EMI的产生。当周期信号和时钟进行转换时,数字线容易产生噪声,布线时应避免使射频信号线接近任何数字线。电源必须以星状拓扑结构形式分配给每个电源引脚端,采用低自感系数的电容器进行退耦。退耦电容器可以采用15~27 pF和100 nF进行组合。还有低电阻电解电容必须放置在每个引脚上来适当去除耦合噪声。电感器的自谐振频率至少应该是工作频率的两倍。PCB地线设计尽可能粗,甚至大面积接地,除了天线部分、元器件引线、电源走线、信号线之外,其余部分均可作为地线。

3.2 PCB天线设计

RF差分输入/输出正端RFP和负端RFN连接平衡-不平衡变换电路和兀型阻抗匹配电路,推荐的PCB天线部分布线图和尺寸(单位:mm)如图4所示。

4、MRF24J40的初始化程序

由MRF24J40构成的IEEE802.15.4无线收发电路必须在微控制器的控制下,才能够在IEEE802.15.4网络中应用。电路中进行数据的发送和接收前,必须完成器件的初始化设置。MRF24J40的初始化程序如下所示:

5、结术语

采用MRF24J40构成的IEEE802.15.4无线收发器电路,支持MiWiTM,ZigBee等协议,为IEEE802.5.15.4MAC和 PHY物理层提供硬件层,工作在2.405~2.48 GHzISM频段,接收灵敏度为-91 dBm,发射输出功率为+0 dBm,采用4线式SPI与微控制器接口,适合家居自动化、工业自动化等低数据速率传输的应用。作为“全自动哮喘诊断仪”的无线数据传输通道,效果良好。

收发器 ZigBee 振荡器 电压 电流 电容 电路 放大器 滤波器 电容器 PCB 射频 电阻 电感 自动化 相关文章:

- 蓝牙无线电调制解调器Siw1701原理与应用(02-19)

- 光纤收发器基本连接方式(10-05)

- GPS Snitch实时目标追踪的奥秘(03-10)

- Broadcom推出业界首款全部基于DSP的10Gb以太网串行收发器(01-08)

- 英飞凌展出集移动WiMAX和无线LAN于一体的RF收发器LSI (03-04)

- 安华高推出单模SFP收发器AFCT-5745xZ系列(03-10)