基于IEEE1588的时钟同步技术在分布式系统中的应用

时间:08-21

来源:互联网

点击:

4 时间戳的生成

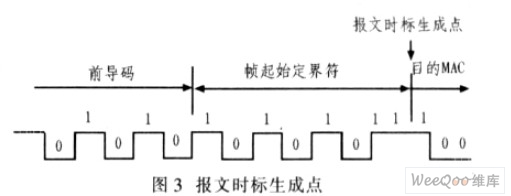

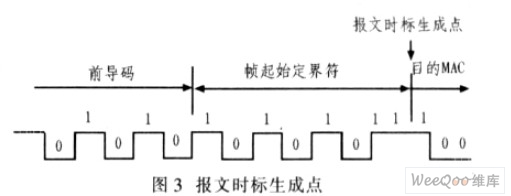

基于以上方法,可有效消除主、从时钟偏差和报文在网络中的传输延迟,从而实现分布式系统的时钟同步。同步信息检测和时间戳生成方法不同,时钟同步精度也不一样,IEEE802.3中规定以太网帧的基本结构:前导码、帧起始定界符、目的MAC、源MAC、长度、数据和帧校验序列。其中,前导码由7个‘1 0’交替的8位字节组成,用于信号同步;而帧起始定界符包含6位交替的‘1 0’及末位的2个1,末位的2个1通知接收端,跟在后面的是帧的实际字段,表示一帧开始。在以太网中,IEEE 1588所定义的各种时钟报文(Sync报文等)均以UDP/IP多播包形式发送的,报文的时标生成点位于帧起始定界符最后一位,如图3所示。

IEEE 1588的同步原理决定了时钟同步的精度主要取决于时间戳的精度。时间戳的加盖有3种方法:

(1)硬件加盖方式 时间戳主要加盖在MAC层和PHY层之间的MII(media independent interface)层,这也是最精确的加盖方式,需用硬件电路实现。

(2)软件加盖方式 时间戳加盖在网络的驱动层,在网络接口的驱动程序中实现,精度略低。

(3)加盖在应用层 因为这种方式无需修改其他系统软件,所以协议栈的操作延迟和负载都能对同步精度造成影响,因此同步精度最低。无论在网络驱动层还是在MII产生的时间戳都必须返回到PTP应用层并经由系统内核处理,然后才发送到PTP终端,由此可以看出时间戳的生成决定了PTP协议的运行。只有获得精确的时间戳才能发挥IEEE 1588所能达到的时钟同步精度。

以太网自身的CSMMCD机制、上一层通信(如TCP及UDP)上进行的误差检测及翻译障碍等,都占用以太网的时间。因此,用软件方式产生时间戳,必须优化加盖时间戳的驱动程序以提高系统内核处理带有时间戳报文的运算效率,同时优化报文发送前在网卡内部的排序,减小程序运行和网络负载对收发报文的影响,从而降低报文发送过程中的软件延迟和抖动。

在以太网中,也可以在物理层放置硬件电路加盖时间戳,这样可以避免协议栈上部较大的时间抖动,消除报文传输中的网络延迟。由于主从时钟不同步的原因除了网络延迟外还有时钟偏差,可以采用频率可调时钟来校正从时钟相对主时钟的时钟偏差,根据从时钟处得出的自身与主时钟的偏差计算出相应的频率补偿值,从而控制时钟计数器的数值达到与主时钟的同步。硬件电路从物理层获得每个发送和接收报文的比特流,并记录时间戳信息,判断其是否为IEEE 1588相关协议报文,如果是相关报文,则把时间戳信息传送给上层软件,否则丢弃该报文的时间戳信息。对于100 M以太网,由于采用4B/SB编码和Scrambler技术,只能在物理层与数据链路层之间的MII层加盖时间戳信息。IEEE 1588时钟同步实现过程如图4所示。

5 基于FPGA的硬件同步方案

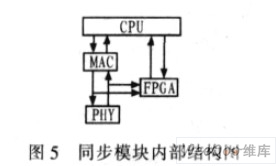

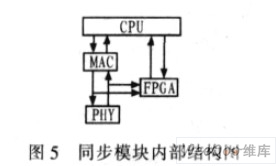

因为采用硬件电路获取时间戳,从而获得更高的同步精度,这里采用FPGA实现时间戳的获取和从时钟相对主时钟的频率纠偏。分布式系统中节点时钟同步模块的内部结构如图5所示。

每个节点包含CPU、以太网媒体访问控制器(MAC)、以太网物理层收发器(PHY)、FPGA等4种主要器件。物理层收发器和MAC控制器通过标准的MII接口相连,CPU通过总线与MAC控制器和FPGA相连。物理层收发器、MAC控制器和CPU构成通讯协议栈完成数据包的发送和接收。

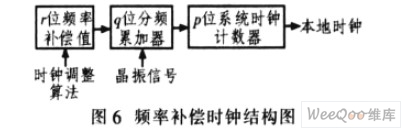

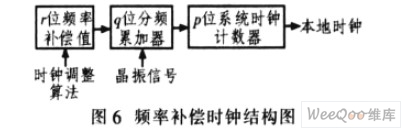

为了使从时钟的晶振频率与主时钟保持一致,FPGA中需要有一个频率可调的时钟以实现晶振纠偏,如图6所示,由r位频率补偿值寄存器、g位分频累加器、p位系统时钟计数器组成,一个普通晶体振荡信号输入FPGA模块。在每个晶振周期,r位频率补偿值寄存器内保存的频率补偿值累加到q位分频累加器中,与累加器中的值相加。

如果发生溢出,则在下一个晶振周期,时钟计数器增加一个增量,这个增量就是整个频率补偿时钟的分辨率;如果没有溢出,则在下一个晶振周期,时钟计数器保持原值。计数器的当前值即为调整后的本地时钟。因此可以通过改变频率补偿值来改变时钟计数器数值增加的频率,实现对晶振频率的补偿。q和r越大,频率补偿值的改变对累加器发生溢出的频率的影响越小,对晶振频率的补偿越精细。本系统选择r=32,q=32,p=64。

使用FPGA不但能够获得最精确的时间戳,而且能够采用数字电路的方法精确补偿从时钟的晶振频率。FPGA的控制器实现时钟调节算法,并由得到的时间戳和本地时钟相比较,得到频率补偿值,从而控制时钟计数器数值,补偿晶振的频率。而CPU则主要负责驱动MAC控制器完成相关的通讯功能。

基于以上方法,可有效消除主、从时钟偏差和报文在网络中的传输延迟,从而实现分布式系统的时钟同步。同步信息检测和时间戳生成方法不同,时钟同步精度也不一样,IEEE802.3中规定以太网帧的基本结构:前导码、帧起始定界符、目的MAC、源MAC、长度、数据和帧校验序列。其中,前导码由7个‘1 0’交替的8位字节组成,用于信号同步;而帧起始定界符包含6位交替的‘1 0’及末位的2个1,末位的2个1通知接收端,跟在后面的是帧的实际字段,表示一帧开始。在以太网中,IEEE 1588所定义的各种时钟报文(Sync报文等)均以UDP/IP多播包形式发送的,报文的时标生成点位于帧起始定界符最后一位,如图3所示。

IEEE 1588的同步原理决定了时钟同步的精度主要取决于时间戳的精度。时间戳的加盖有3种方法:

(1)硬件加盖方式 时间戳主要加盖在MAC层和PHY层之间的MII(media independent interface)层,这也是最精确的加盖方式,需用硬件电路实现。

(2)软件加盖方式 时间戳加盖在网络的驱动层,在网络接口的驱动程序中实现,精度略低。

(3)加盖在应用层 因为这种方式无需修改其他系统软件,所以协议栈的操作延迟和负载都能对同步精度造成影响,因此同步精度最低。无论在网络驱动层还是在MII产生的时间戳都必须返回到PTP应用层并经由系统内核处理,然后才发送到PTP终端,由此可以看出时间戳的生成决定了PTP协议的运行。只有获得精确的时间戳才能发挥IEEE 1588所能达到的时钟同步精度。

以太网自身的CSMMCD机制、上一层通信(如TCP及UDP)上进行的误差检测及翻译障碍等,都占用以太网的时间。因此,用软件方式产生时间戳,必须优化加盖时间戳的驱动程序以提高系统内核处理带有时间戳报文的运算效率,同时优化报文发送前在网卡内部的排序,减小程序运行和网络负载对收发报文的影响,从而降低报文发送过程中的软件延迟和抖动。

在以太网中,也可以在物理层放置硬件电路加盖时间戳,这样可以避免协议栈上部较大的时间抖动,消除报文传输中的网络延迟。由于主从时钟不同步的原因除了网络延迟外还有时钟偏差,可以采用频率可调时钟来校正从时钟相对主时钟的时钟偏差,根据从时钟处得出的自身与主时钟的偏差计算出相应的频率补偿值,从而控制时钟计数器的数值达到与主时钟的同步。硬件电路从物理层获得每个发送和接收报文的比特流,并记录时间戳信息,判断其是否为IEEE 1588相关协议报文,如果是相关报文,则把时间戳信息传送给上层软件,否则丢弃该报文的时间戳信息。对于100 M以太网,由于采用4B/SB编码和Scrambler技术,只能在物理层与数据链路层之间的MII层加盖时间戳信息。IEEE 1588时钟同步实现过程如图4所示。

5 基于FPGA的硬件同步方案

因为采用硬件电路获取时间戳,从而获得更高的同步精度,这里采用FPGA实现时间戳的获取和从时钟相对主时钟的频率纠偏。分布式系统中节点时钟同步模块的内部结构如图5所示。

每个节点包含CPU、以太网媒体访问控制器(MAC)、以太网物理层收发器(PHY)、FPGA等4种主要器件。物理层收发器和MAC控制器通过标准的MII接口相连,CPU通过总线与MAC控制器和FPGA相连。物理层收发器、MAC控制器和CPU构成通讯协议栈完成数据包的发送和接收。

为了使从时钟的晶振频率与主时钟保持一致,FPGA中需要有一个频率可调的时钟以实现晶振纠偏,如图6所示,由r位频率补偿值寄存器、g位分频累加器、p位系统时钟计数器组成,一个普通晶体振荡信号输入FPGA模块。在每个晶振周期,r位频率补偿值寄存器内保存的频率补偿值累加到q位分频累加器中,与累加器中的值相加。

如果发生溢出,则在下一个晶振周期,时钟计数器增加一个增量,这个增量就是整个频率补偿时钟的分辨率;如果没有溢出,则在下一个晶振周期,时钟计数器保持原值。计数器的当前值即为调整后的本地时钟。因此可以通过改变频率补偿值来改变时钟计数器数值增加的频率,实现对晶振频率的补偿。q和r越大,频率补偿值的改变对累加器发生溢出的频率的影响越小,对晶振频率的补偿越精细。本系统选择r=32,q=32,p=64。

使用FPGA不但能够获得最精确的时间戳,而且能够采用数字电路的方法精确补偿从时钟的晶振频率。FPGA的控制器实现时钟调节算法,并由得到的时间戳和本地时钟相比较,得到频率补偿值,从而控制时钟计数器数值,补偿晶振的频率。而CPU则主要负责驱动MAC控制器完成相关的通讯功能。

总线 传感器 自动化 GPS 电路 FPGA 收发器 相关文章:

- 热插拔和缓冲I2C总线 (04-14)

- PCIe总线何时突破Unix服务器坚冰(02-03)

- TMS320VC5402 HPI接口与PCI总线接口设计(04-12)

- 基于Nios II的I2C总线接口的实现(04-09)

- 双口RAM CY7C026在高速数据采集系统中的应用(04-12)

- 计算机在新型多电机同步系统中的应用(07-08)