精密频率合成技术助力多通道频率合成器的应用

多。天线制作成一个阵列形式,习惯用电子的方式控制发射的雷达射束。这种天线被称为"相阵雷达"。对于阵列中每个单个的天线,都分配一个DDS 通道,并且其相位的调整是射束控制的机制。在所有何情况下的射束控制都使所有DDS通道以相同的输出频率工作,因此利用相位偏移特性完成射束控制任务。

FMCW雷达使用相阵天线比脉冲雷达更为困难。在这种配置中,射束很难控制 ,因为当发出信号线性调频信号时要求不断地改变相位差。要克服这种困难,必须在线性调频率期间对每个FMCW 信号进行相位调整。为作到这一点,需要提供一个匹配的等待时间开关以便允许频率、相位和变化幅度同时发生变化。在前面的DDS设计中,当这些参数同时变化时不能在DAC的输出端同时显现,由于其内部波形发生器的管道级延迟效应。

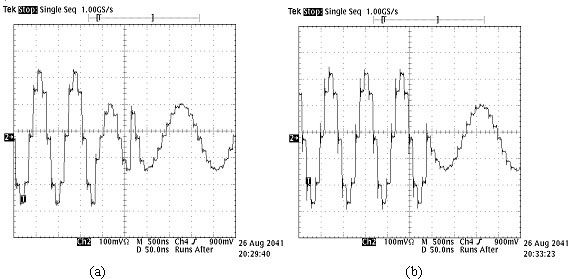

图6示出一个管道匹配的DAC输出和一个非管道匹配的DAC输出之间的差别,其中频率和幅度相差一半并且相位变化180°。曲线(a)清楚地示出幅度在相位之前变化,频率在相位之后变化。在曲线(b)中,管道匹配开关允许,DAC输出同时改变频率、相位和幅度。应当注意:为了更好地示出等待时间匹配的影响,曲线显示的是未经滤波的DAC输出,这就是为什么其输出呈现"阶梯"状的原因。

图6 (a)管道延迟匹配开关禁止; (b)管道延迟匹配开关允许

同步多个AD9959/58器件

最近研究结果表明,50%以上的所有基于DDS的设计采用了多通道,并且几乎75%的多通道系统都要求通道之间同步。另外,几乎15%的多通道系统都需要四个以上的通道。为了支持这些需要四个以上通道的系统,AD9959/58产品包含了能够使多个AD9959/58器件相互之间自动同步的电路。

当所有器件内部时钟发生状态机的状态都相同时,就认为多个器件是同步的,从而使每个器件的SYNC_CLK输出引脚都产生相互相同的相位。多个器件同步可通过将主器件的SYNC_OUT输出引脚简单地连接到从器件的SYNC_IN输入引脚实现。通过串行端口设置bit位,可将器件配置为主器件和从器件。

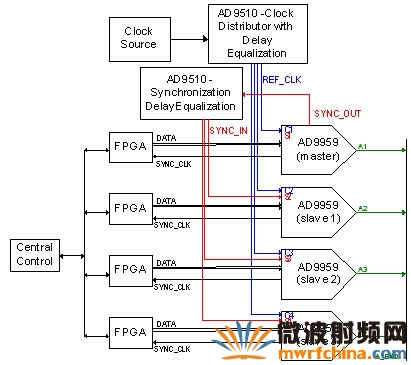

图7示出一种用于同步多个AD9959/58器件的典型配置。

图7. AD9959/58多芯片同步设置框图

参看图7,来自主器件的同步脉冲发送到AD9959/58芯片外的"同步延迟平衡"电路,目的是将这个脉冲同时分配到从器件的SYNC_IN引脚。从器件从主器件采样同步脉冲并且将时钟发生状态机的当前状态和一个 "期望"值作比较。如果从器件的时钟发生状态机与期望值比较的结果正确,那么从器件就是同步的。如果从器件的时钟发生状态机和期望值不同,那么从器件就将时钟发生状态机延迟一个系统时钟周期。只要器件配置为同步,这个采样、比较、执行的过程就会连续进行。那就是说,如果从器件由于基准时钟输入暂时不稳定而不同步,一旦基准时钟达到稳定,从器件会自动重新与主器件同步。

敏锐的读者可能会考虑到,在高系统时钟速率条件下,很难在一个系统时钟周期内将同步脉冲从主器件传送到从器件。为了便于在高速率下同步,允许用户设置从器件,以期望在主器件产生同步脉冲后延后1~16个系统时钟周期。这可以通过串行接口以增量方式对从器件进行设置实现的,即设置期望产生的外部传播延迟的周期数。这种特性的另一个好处是每个从器件可设置不同的 "期望状态",它允许在同步脉冲分配电路中有较大的容许误差。

除了自动同步方式以外,AD9959/58还提供手动同步方式,直接由用户控制。硬件和软件手动同步方式都可提供。硬件手动同步方式允许用户将器件时钟发生状态机对于在SYNC_IN引脚上检测到的每个上升沿(逻辑值 1)延迟一个系统时钟周期。在软件手动方式中,可通过串口写入一个专门的控制位(bit),使该器件时钟发生状态机延迟一个系统时钟周期。在单个系统时钟周期步长中,时钟发生状态机延迟一个系统时钟周期具有改变系统时钟和SYNC_CLK输出信号之间相位关系的作用。

通道之间的隔离性能

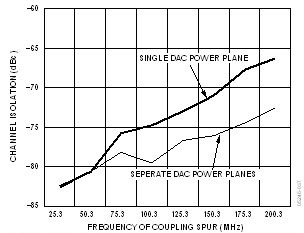

多通道系统的一个关键指标是通道之间的隔离。没有正确的隔离,交流(AC)性能会显著变差,负面地影响性能。图8示出AD9959典型通道隔离性能的实验室结果。在四个通道上进行测量,其中一个通道产生110.3 MHz 固定频率,而其它三个通道在25 MHz~200 MHz频率范围内扫描。在110.3 MHz频率下的通道具有的功率电平与泄漏到其它通道的功率电平之差就是通道之间的隔离度。对于所有可能的情况,记录下优于-65dBc的测量结果。两通道AD9958器件在相同测试条件下其通道隔离度提高-6dBc。

图8 在500MSPS工作条件下的通道隔离,要测试的通道固定在110.3MHz,其他通道以25MHz增量进行频率扫描

其它特性

尽管本文集中于AD9959/58的多

- 基于单片机的直接数字频率合成器的设计(11-14)

- 基于PE3236的L波段频率合成器的设计(08-29)

- 基于锁相环的频率合成器的设计(08-28)

- 频率合成器的高性能架构实现技术(08-03)

- 如何设计并调试锁相环PLL(03-19)

- 锁相环的工作原理及设计方法(06-19)