高速数字系统的串扰问题分析

时间:10-07

来源:互联网

点击:

2.1 耦合长度对串扰的影响

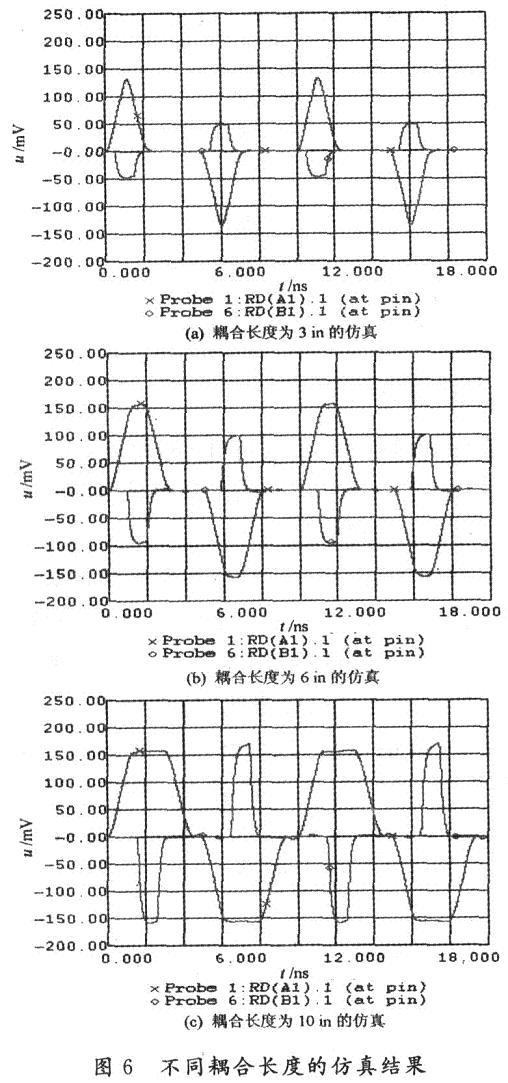

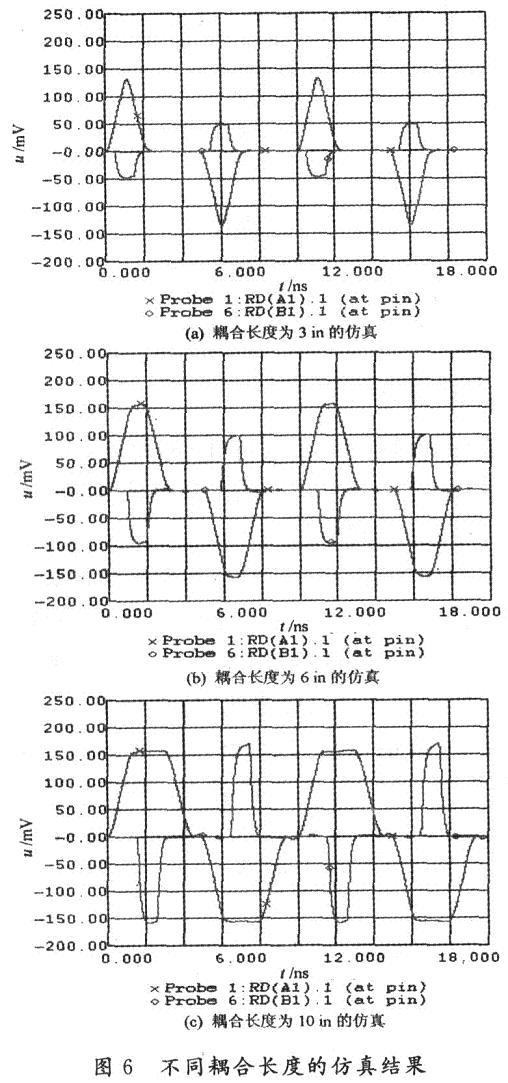

改变两线的耦合长度,分别将耦合长度设置为3 in,6 in,10 in,其他设置不变。

图6(a)是耦合长度为3 in的串扰波形,其中近端串扰峰值为126.34 mV,远端为43.01 mV;图6(b)是耦合长度为6 in的串扰波形,其近端串扰峰值为153.23 mV,远端为99.46 mV;图6(c)是耦合长度为10 in的串扰波形,其近端串扰峰值为153.23 mV,远端为163.98 mV。由此可见,对于远端串扰峰值与耦合长度成正比,耦合长度越长,串扰越大;而对于近端串扰,当耦合长度小于饱和长度时,串扰将随着耦合长度的增加而增加,但是当耦合长度大于饱和长度时,近端串扰值将为一个稳定值。

2.2 线间距对串扰的影响

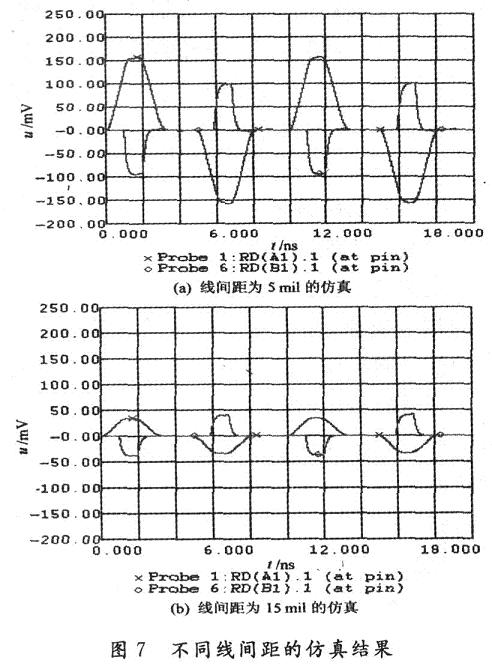

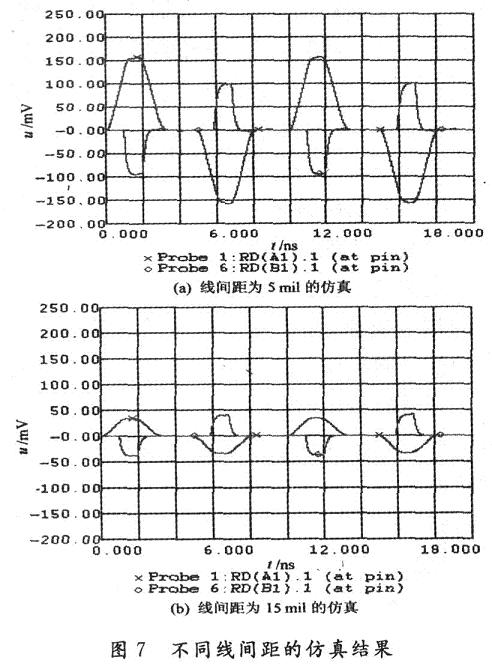

以下是保持其他设置不变,考察线间距的改变对串扰的影响。分别设置线距为5 mil,15 mil,仿真波形如图7所示。

由图7可知,当线间距为5 mil时,近段串扰峰值为153.23 mV,远端为99.46 mV;而线间距为15 mil时,近端串扰峰值为33.40 mV,远端为40.49 mV。可见随着线间距的增大,无论是近端还是远端串扰都将减小,当线间距大于等于线宽的3倍时,串扰已经很小。

2.3 上升时间对串扰的影响

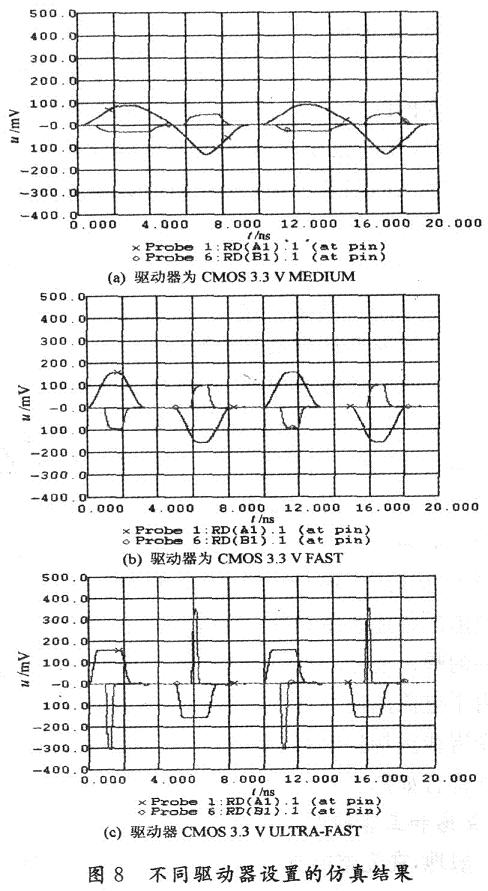

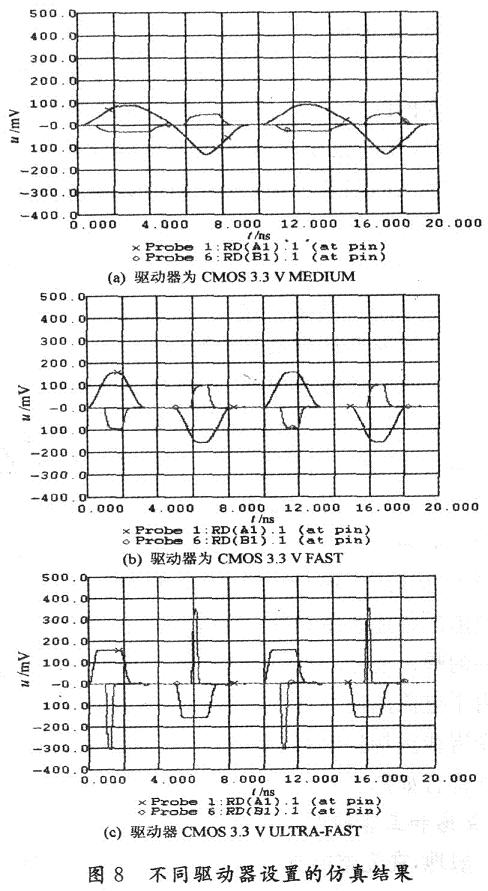

下面考察上升沿时间的变化对串扰的影响,其他设置保持不变。分别设置驱动器为CMOS 3.3 V MEDI—UM;CMOS 3.3 V FAST;CMOS 3.3 V ULTRA—FAST,仿真波形如图8所示。

图8(a)中的近端串扰峰值为153.9 mV,远端串扰为46.3 mV;图8(b)中近端串扰峰值为153.2 mV,远端串扰为99.5 mV;图8(c)中近段串扰峰值为153.2 mV,远端串扰为349.9 mV。可见,当上升沿时间缩短时,远端串扰噪声越来越大。对于近端串扰来说,如果与传输线的时延相比,上升时间较短,则近端串扰与上升时间无关;而如果与传输线时迟相比,上升时间较长,则近端串扰噪声与上升时间有关(随着上升沿时间的减小,近端串扰变大)。

2.4 介质层厚度对串扰的影响

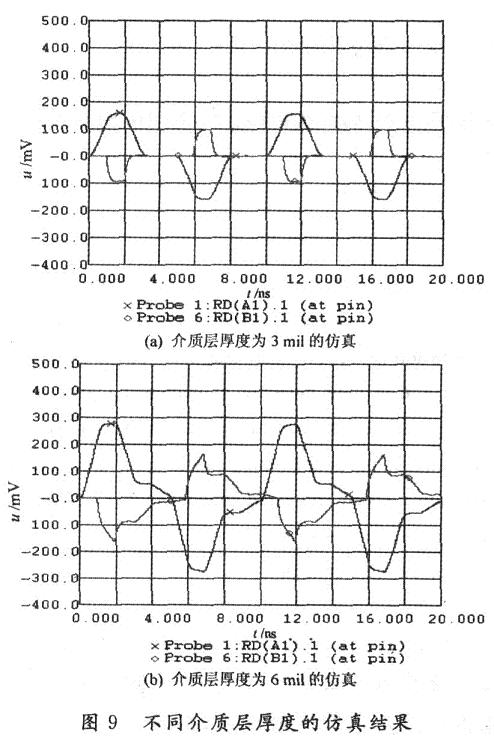

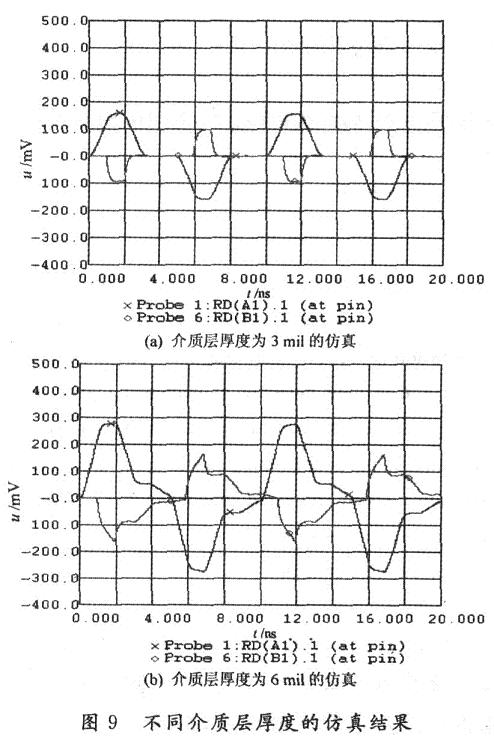

在PCB的叠层编辑器中将介质层厚度分别设置为3 mil和6 mil,其他设置不变,仿真波形如图9所示。

考察以上的仿真波形可知,当介质层厚度为3 mil时,近端串扰峰值为153.2 mV,远端串扰为99.5 mV;当介质层厚度为6 mil时,近端串扰峰值为277.3 mV,远端串扰为163.9 mV。可见,随着介质层厚度的减小,串扰也将变小。

3 解决串扰的方法

串扰在电子产品的设计中普遍存在,通过以上的分析与仿真,了解了串扰的特性,总结出以下减少串扰的方法:

(1)在情况允许的情况下,尽量增大走线之间的距离,减小平行走线的长度,必要时采用jog方式走线。

(2)在确保信号时序的情况下,尽可能地选择上升沿和下降沿速度更慢的器件,使电场和磁场变化的速度变慢,从而降低串扰。

(3)在设计走线时,应该尽量使导体靠近地平面或电源平面。这样可以使信号路径与地平面紧密的耦合,减少对相邻信号线的干扰。

(4)在布线空间允许的条件下,在串扰较严重的两条信号线之间插入一条地线,可以减小两条信号线间的耦合,进而减小串扰。

4 结 语

串扰是信号完整性中的重要内容,影响系统的时序、降低噪声容限,导致系统无法正常的工作。介绍了高速电路中串扰产生的机理,并通过仿真对串扰进行分析,得出串扰的大小与影响串扰相关因素的关系,在此基础上提出了一些减小串扰的方法,对于在高速高密度的电路设计中解决串扰问题有一定的指导意义。

改变两线的耦合长度,分别将耦合长度设置为3 in,6 in,10 in,其他设置不变。

图6(a)是耦合长度为3 in的串扰波形,其中近端串扰峰值为126.34 mV,远端为43.01 mV;图6(b)是耦合长度为6 in的串扰波形,其近端串扰峰值为153.23 mV,远端为99.46 mV;图6(c)是耦合长度为10 in的串扰波形,其近端串扰峰值为153.23 mV,远端为163.98 mV。由此可见,对于远端串扰峰值与耦合长度成正比,耦合长度越长,串扰越大;而对于近端串扰,当耦合长度小于饱和长度时,串扰将随着耦合长度的增加而增加,但是当耦合长度大于饱和长度时,近端串扰值将为一个稳定值。

2.2 线间距对串扰的影响

以下是保持其他设置不变,考察线间距的改变对串扰的影响。分别设置线距为5 mil,15 mil,仿真波形如图7所示。

由图7可知,当线间距为5 mil时,近段串扰峰值为153.23 mV,远端为99.46 mV;而线间距为15 mil时,近端串扰峰值为33.40 mV,远端为40.49 mV。可见随着线间距的增大,无论是近端还是远端串扰都将减小,当线间距大于等于线宽的3倍时,串扰已经很小。

2.3 上升时间对串扰的影响

下面考察上升沿时间的变化对串扰的影响,其他设置保持不变。分别设置驱动器为CMOS 3.3 V MEDI—UM;CMOS 3.3 V FAST;CMOS 3.3 V ULTRA—FAST,仿真波形如图8所示。

图8(a)中的近端串扰峰值为153.9 mV,远端串扰为46.3 mV;图8(b)中近端串扰峰值为153.2 mV,远端串扰为99.5 mV;图8(c)中近段串扰峰值为153.2 mV,远端串扰为349.9 mV。可见,当上升沿时间缩短时,远端串扰噪声越来越大。对于近端串扰来说,如果与传输线的时延相比,上升时间较短,则近端串扰与上升时间无关;而如果与传输线时迟相比,上升时间较长,则近端串扰噪声与上升时间有关(随着上升沿时间的减小,近端串扰变大)。

2.4 介质层厚度对串扰的影响

在PCB的叠层编辑器中将介质层厚度分别设置为3 mil和6 mil,其他设置不变,仿真波形如图9所示。

考察以上的仿真波形可知,当介质层厚度为3 mil时,近端串扰峰值为153.2 mV,远端串扰为99.5 mV;当介质层厚度为6 mil时,近端串扰峰值为277.3 mV,远端串扰为163.9 mV。可见,随着介质层厚度的减小,串扰也将变小。

3 解决串扰的方法

串扰在电子产品的设计中普遍存在,通过以上的分析与仿真,了解了串扰的特性,总结出以下减少串扰的方法:

(1)在情况允许的情况下,尽量增大走线之间的距离,减小平行走线的长度,必要时采用jog方式走线。

(2)在确保信号时序的情况下,尽可能地选择上升沿和下降沿速度更慢的器件,使电场和磁场变化的速度变慢,从而降低串扰。

(3)在设计走线时,应该尽量使导体靠近地平面或电源平面。这样可以使信号路径与地平面紧密的耦合,减少对相邻信号线的干扰。

(4)在布线空间允许的条件下,在串扰较严重的两条信号线之间插入一条地线,可以减小两条信号线间的耦合,进而减小串扰。

4 结 语

串扰是信号完整性中的重要内容,影响系统的时序、降低噪声容限,导致系统无法正常的工作。介绍了高速电路中串扰产生的机理,并通过仿真对串扰进行分析,得出串扰的大小与影响串扰相关因素的关系,在此基础上提出了一些减小串扰的方法,对于在高速高密度的电路设计中解决串扰问题有一定的指导意义。

电子 电路 PCB 连接器 电压 电流 电容 电感 仿真 Mentor 电阻 CMOS 相关文章:

- IC设计产业紧贴创新应用(03-26)

- 基于Multisim数字电子钟设计(05-18)

- 结合MDA-EDA电子散热仿真解决方案(07-20)

- 电子元件及电路组装技术介绍(08-26)

- 面向电子装联的PCB可制造性设计(10-20)

- 印制电路板制作的基础知识(08-04)