PCB设计布线通道计算和设计规划

PCB设计中布线通道如何计算?与设计规则存在什么样的联系?

布线通道计算规则:

PCB板布线通道初步估算方式:

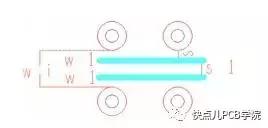

两个过孔之间布线通道:Ni=INT((Wi-2S-W1)/(W1+S1)+1)

其中:

Ni:相邻两过孔间布线通道数

Wi:过孔边沿间距

S:过孔到布线边沿间距

W1:线宽

S1:线间距

两个过孔之间布线通道计算示意图

差分线时:

W1:=2*W2+S2 通道数即为差分线通道数

W2:差分线线宽

S2:差分线对内线间距

差分线计算通道时:将一对差分线(W2/S2)等效成一根单线(线宽为2*W2+S2)处理。

说明:50MIL格点系统,普通信号(5MIL线宽、8MIL线间距)安照2个布线通道设计,时钟信号按照1个布线通道设计,差分信号按照1对差分线通道设计。

高密区域布线规划知识:

(1)建议高密BGA布线采用特殊Fanout布线方式,外围4排管脚引出通过表层Fanout,增大布线通道。

(2) 所有电源,地管脚需要直接Fanout到相应的平面层,避免引出起出100mil长线Fanout,不包含到布线层的布线通道规划。

(3)高密BGA区域布线层数确定规则如下:

最少内层布线层数=INT(M/N)+1

最多内层布线层数=BGA非电源地最密管脚排布层数/两过孔间布线通道数-2

说明:M:除外围4层管脚外BGA区域的非电源地布线连接总数+前两排直接Fanout浪费的布线通道数;N:第5排管脚Fanout环区域的布线通道总数

BGA区域所有除外4层的管脚布线都需要占用第5层环形区域的布线通道,根据此区域的布线通道数和总的布线连接数确定最少内层布线层数。

(4)根据布线瓶颈区确定PCB板布线层数,瓶颈区域PCB板最少布线层数=INT(M/N)+1

说明:M:通过瓶颈区域的布线连接数;N:瓶颈区域的布线通道数

高密BGA区域布线规划需要优先进行总线的划分,定义的各种BUS,然后根据各种总线的分布确定布线的大致区域,最后根据各组总线的所需通道数进行详细的通道具分配和布线规划。

重要信号布线规划知识:

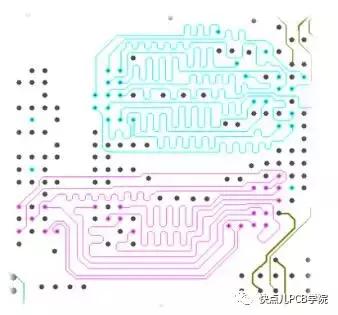

(1)建议200MHz以上或时序余量小于0.2ns的同步并行总线要求拓扑结构保持严格一致,同层并行布线,同步换层

说明:如DDR高速并行总线结构,为达到最佳信号质量,同组DQ/DQS信号相同层布线,地址和控制总线同层布线,同步换层,分别控制表层和内层布线等长

(2)禁止不同类型总线混合布线

说明:如禁止DDR与Local bus混合布线,DDR数据与地址混合布线等,但如果空间有限的情况下,可以采用部分混合布线,但要求地址线与数据线要保证大于3H的距离。

一般DDR布线(红色为地址线,绿色为数据线)

(3)高速信号优先布线

(4)建议高速信号避免表层布线

(5)3.125Gbps以上高速信号布线必须选择过孔Stub最小的布线层,并减少过孔数量。

(6)建议3.125Gbps以下高速信号(包括3.125Gbps)优先过孔STUB最小的布线层

(7)3.125Gbps以上高速信号布线规划时优先考虑布线长度,做到最短。

(8)高速信号布线需要规则至具有完整参考平面层的布线层

(9)模拟信号禁止在数字信号区域布线

(10)不同电平信号禁止混合布线

说明:如LVTTL与CML电平信号

以上便是PCB设计中布线通道计算和设计规划,下期预告:特殊信号线处理。

- Cadence 推出创新的FPGA-PCB协同设计解决方案(04-25)

- 高速PCB布线实践指南(11-01)

- PCB抄板/设计原理图制成PCB板的过程经验(02-04)

- IBIS 模型:利用 IBIS 模型研究信号完整性问题(08-08)

- 巧妙的线路板布线改善蜂窝电话的音质(11-01)

- PCB反设计系统中的探测电路(02-18)