PCB设计中DDR布线要求及绕等长要求

本期讲解的是高速PCB设计中DDR布线要求及绕等长要求。

布线要求

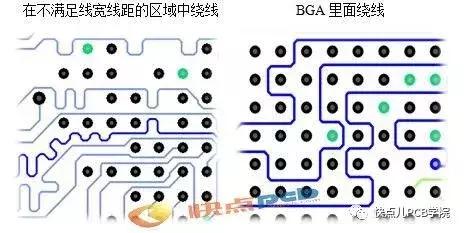

数据信号组:以地平面为参考,给信号回路提供完整的地平面。特征阻抗控制在50~60 Ω。线宽要求参考实施细则。与其他非DDR信号间距至少隔离20 mil。长度匹配按字节通道为单位进行设置,每字节通道内数据信号DQ、数据选通DQS和数据屏蔽信号DM长度差应控制在±25 mil内(非常重要),不同字节通道的信号长度差应控制在1000 mil内。与相匹配的DM和DQS串联匹配电阻RS值为0~33 Ω,并联匹配终端电阻RT值为25~68Ω。如果使用电阻排的方式匹配,则数据电阻排内不应有其他DDR信号。

地址和命令信号组:保持完整的地和电源平面。特征阻抗控制在50~60 Ω。信号线宽参考具体设计实施细则。信号组与其他非DDR信号间距至少保持在20 mil以上。组内信号应该与DDR时钟线长度匹配,差距至少控制在25 mil内。串联匹配电阻RS值为O~33 Ω,并联匹配电阻RT值应该在25~68 Ω。本组内的信号不要和数据信号组在同一个电阻排内。

控制信号组:控制信号组的信号最少,只有时钟使能和片选两种信号。仍需要有一个完整的地平面和电源平面作参考。串联匹配电阻RS值为0~33 Ω,并联匹配终端电阻RT值为25~68 Ω。为了防止串扰,本组内信号同样也不能和数据信号在同一个电阻排内。

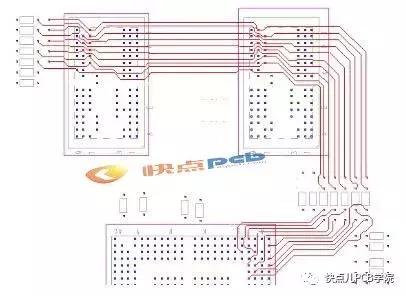

走线方式:对于一驱多的DDR走线方式有菊花链,星型走线(T型走线),下图是地址线从CPU芯片一驱2个DDR

下图是从CPU到两颗DDR地址走线采用星型拓扑,从芯片到两颗DDR的地址走线长度一样。

绕等长要求

先确认以下几点:

1、DDR的线有没有布完,检查是否有漏线

2、信号线是否有优化好,间距规则有没有设并已清完相关DRC

3、DDR布线是否满足要求,如同组走同层,线宽是否正确

4、绕线时需要注意你所做的部分对周边布局布线是否造成影响

5、是否明确绕线规则,如几倍线宽或间距进行绕线与线与线之间的相互约束关系

6、对于中间有串阻的颗粒DDR,明确前后两端是否有信号线长度限制要求

7、参考平面是否确认,注意等长时不要跨参考平面布线

8、对于DIMM DDR的绕线策略为:先做Address的等长,再往两边扩展做data的等长

9、在组内绕线时一定要找出组内最长的信号线,并尽可能缩短,再以其为基准进行绕线

10、绕等长时要确认同组线与线之间的间距要求,高速的DDR要求3W间距

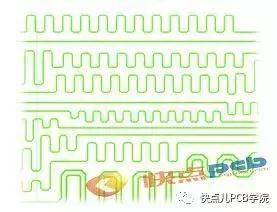

绕线的方式

一般推荐这种(绕线的一端不对着自身信号)

以下几种布线较差不推荐:

以上便是DDR布线要求及绕等长要求,下期预告:高速信号PCB设计知识。请同学们持续关注【快点儿PCB学院】公众号。

- Cadence 推出创新的FPGA-PCB协同设计解决方案(04-25)

- 高速PCB布线实践指南(11-01)

- PCB抄板/设计原理图制成PCB板的过程经验(02-04)

- IBIS 模型:利用 IBIS 模型研究信号完整性问题(08-08)

- 巧妙的线路板布线改善蜂窝电话的音质(11-01)

- PCB反设计系统中的探测电路(02-18)