PCB布线设计中DDR2重要性

时间:12-26

来源:互联网

点击:

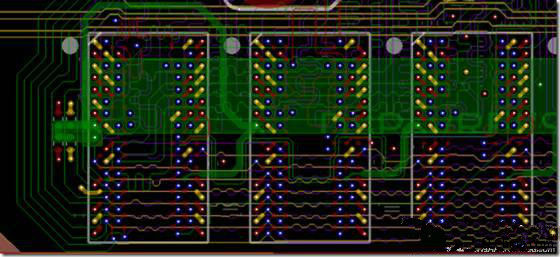

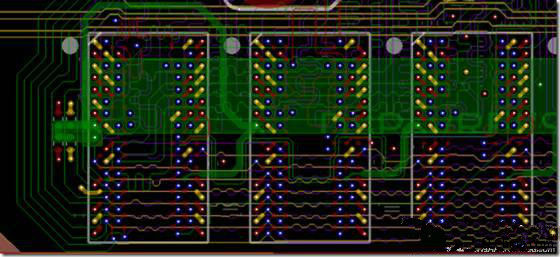

PCB布线设计的好坏直接影响到硬件电路能否正常工作或运行多快的速度。而在高速数字PCB设计中,DDR2是非常常见的高速缓存器件,且其工作频率很高本文将针对DDR2的PCB布线进行讨论。

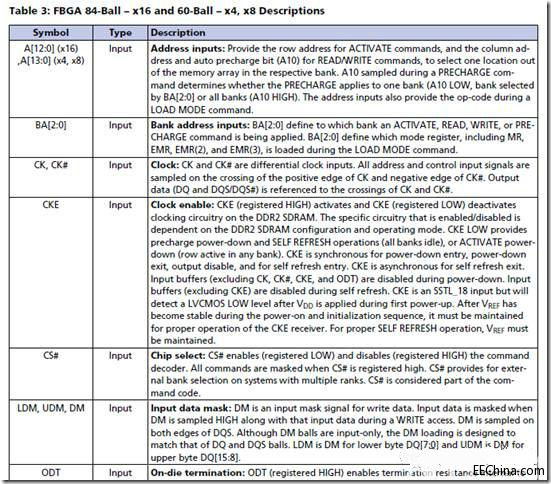

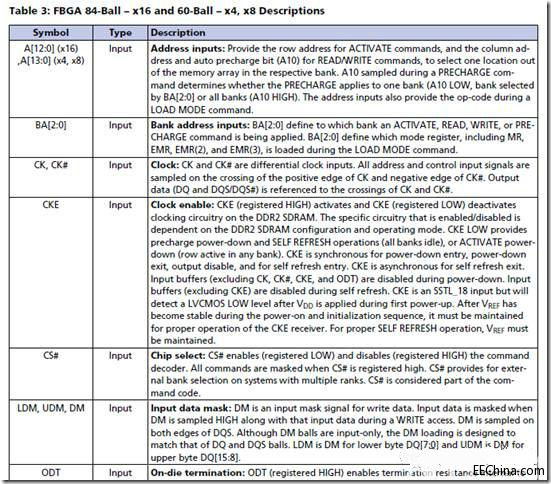

DDR2的型号为MT47H64M16,具体型号功能介绍如图,

设计要点:

1、电路板的阻抗控制在 50~60ohm,差分线为100~120ohm。

2、DQ,DQS 和时钟信号线选择VSS 作为参考平面,因为VSS 比较稳定,不易受到干扰;

地址/命令/控制信号线选择VDD 作为参考平面,因为这些信号线本身就含有噪声。

3、短接技术:

串行端接:主要应用在负载DDR 器件不大于4 个的情况下。对于单向的信号来说,例如地址线,控制线,串行端接电阻放置在走线中间或者是信号的发送端,推荐放置在信号的发送端。

并行端接:主要应用在负载SDRAM 器件大于4 个,走线长度>2inch,或者通过仿真验证需要并行端接的情况下。并行端接电阻Rt 取值大约为2Rs,Rt 的取值范围为36Ω–56Ω,推荐47Ω(MICRON观点)

差分端接:适用CK、CK#差分信号。

布线顺序:

VTT电源平面---时钟线---数据线---地址线---命令控制线---VDD和VDDQ电源。

线宽线距:

(1) 时钟(差分对)除了等长(< 50mil),要需要25mil的安全距离。两个时钟CK之间相差100mil之内。

(2) 地址线不用等长,比时钟要长一些。

(3) 控制线比时钟要长一些。

(4) 每一个Data Group(8bits data + DQS + DM)在同一层走线。DDR2的数据线与DQS是源同步关系,等长处理。同组的数据线以DQS基准等长(<50mil)。组与组之间的长度差不超过1000mil。DQS与CK之间的约束较弱,一般不考虑,长度差别不要超过1000mil就差不多。

(5) 地址/命令/控制信号与时钟是源同步的,走线长度匹配并不严格要求。

当负载较大的时候,DDR2拓扑结构中必须加入并联终结电阻及VTT电源。

DDR2的型号为MT47H64M16,具体型号功能介绍如图,

设计要点:

1、电路板的阻抗控制在 50~60ohm,差分线为100~120ohm。

2、DQ,DQS 和时钟信号线选择VSS 作为参考平面,因为VSS 比较稳定,不易受到干扰;

地址/命令/控制信号线选择VDD 作为参考平面,因为这些信号线本身就含有噪声。

3、短接技术:

串行端接:主要应用在负载DDR 器件不大于4 个的情况下。对于单向的信号来说,例如地址线,控制线,串行端接电阻放置在走线中间或者是信号的发送端,推荐放置在信号的发送端。

并行端接:主要应用在负载SDRAM 器件大于4 个,走线长度>2inch,或者通过仿真验证需要并行端接的情况下。并行端接电阻Rt 取值大约为2Rs,Rt 的取值范围为36Ω–56Ω,推荐47Ω(MICRON观点)

差分端接:适用CK、CK#差分信号。

布线顺序:

VTT电源平面---时钟线---数据线---地址线---命令控制线---VDD和VDDQ电源。

线宽线距:

(1) 时钟(差分对)除了等长(< 50mil),要需要25mil的安全距离。两个时钟CK之间相差100mil之内。

(2) 地址线不用等长,比时钟要长一些。

(3) 控制线比时钟要长一些。

(4) 每一个Data Group(8bits data + DQS + DM)在同一层走线。DDR2的数据线与DQS是源同步关系,等长处理。同组的数据线以DQS基准等长(<50mil)。组与组之间的长度差不超过1000mil。DQS与CK之间的约束较弱,一般不考虑,长度差别不要超过1000mil就差不多。

(5) 地址/命令/控制信号与时钟是源同步的,走线长度匹配并不严格要求。

当负载较大的时候,DDR2拓扑结构中必须加入并联终结电阻及VTT电源。

- Cadence 推出创新的FPGA-PCB协同设计解决方案(04-25)

- 高速PCB布线实践指南(11-01)

- PCB抄板/设计原理图制成PCB板的过程经验(02-04)

- IBIS 模型:利用 IBIS 模型研究信号完整性问题(08-08)

- 巧妙的线路板布线改善蜂窝电话的音质(11-01)

- PCB反设计系统中的探测电路(02-18)