高速PCB设计软件allegro16.6演示差分规则的设置

时间:01-06

来源:互联网

点击:

上一期我们介绍了高速PCB设计软件

allegro16.6差分信号的设定

在高速PCB布线前

需要对差分信号的规则进行设置

因此

本期重点介绍在电气规则和物理规则下

是如何建立差分信号的规则

1、在电气规则下建立差分规则

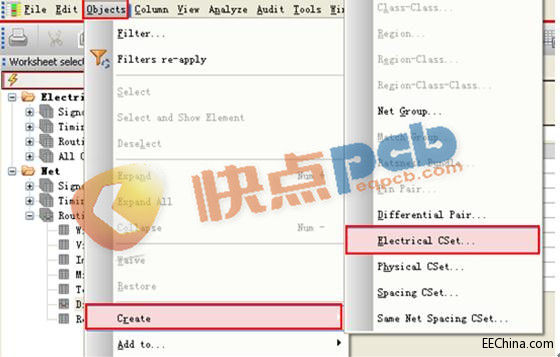

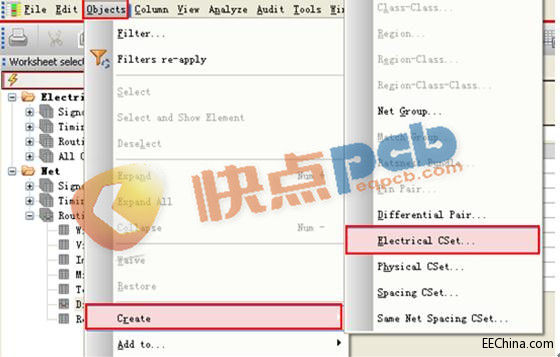

首先,点击左边的工作选择区中的ELECTRICALR 工作表下的 ELECTRICALR constrain set=>Routing=>differential pair,然后选择菜单命令 objects=>create=>ELECTRICALR set,如图下图所示

图1-1电气规则下创建差分规则

在弹出 Create Electrical set 对话框。

图1-2电气规则命名

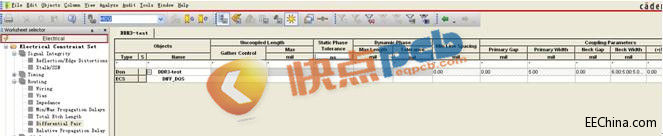

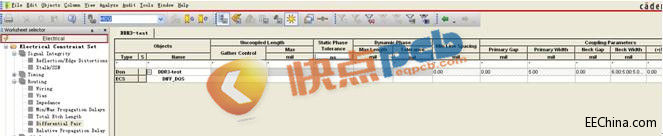

在 Electrical CSet 编辑框输入差分信号规则名称,这时在右边的工作表中可以看到多了一个DIFF_DQS 的约束规则,如下图1-3所示

图1-3规则参数设置

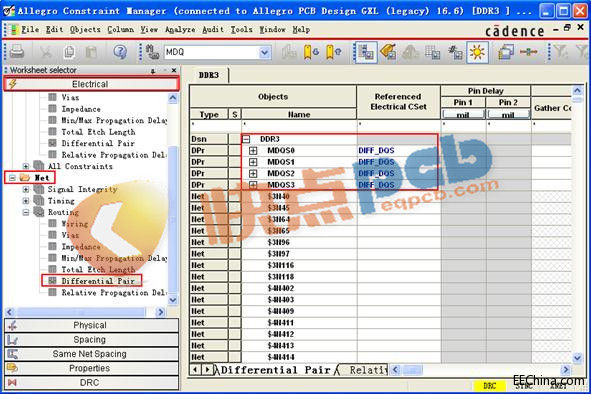

差分信号的约束规则参数主要有以下几个:

Uncoupled Length:差分信号网络中不匹配中的长度,即不能按差分信号走线的总长度。

Min Line Spacing:最小的线间距。

Primary Gap:差分信号最优先选择的线间距。

Primary Width:差分信号最优先选择的线宽。

Neck Gap:差分信号在 NECK 模式下的线间距(用于在布线比较密集的区域)。

Neck Width:差分信号在 NECK 模式下的线宽。

图1-4差分信号参数

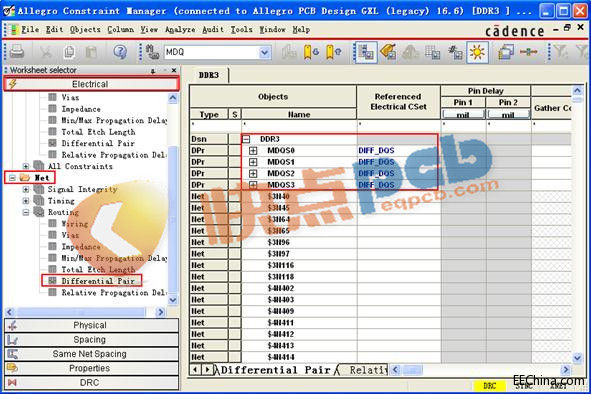

设置好差分信号约束规则后,将该约束规则应用于差分信号上,点击左边的工作表选择区中的Electrical 工作表下的 net 下routing,在右边的工作表找到所建的差分信号,在 referenced Electrical CSet 选择刚才设置好的差分信号约束规则 DIFF_DQS,如下图1-5所示。

图1-5给差分信号赋予差分规则

这样就把设置好的差分规则分配到对应的差分网络了。

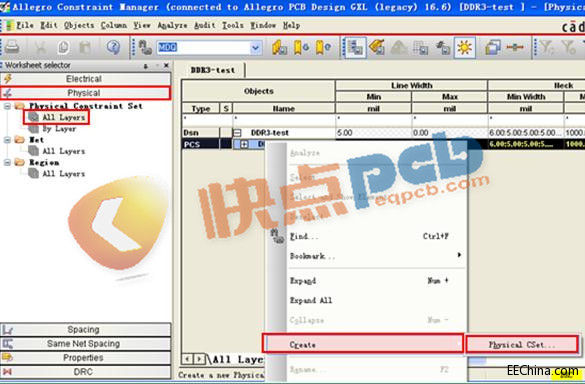

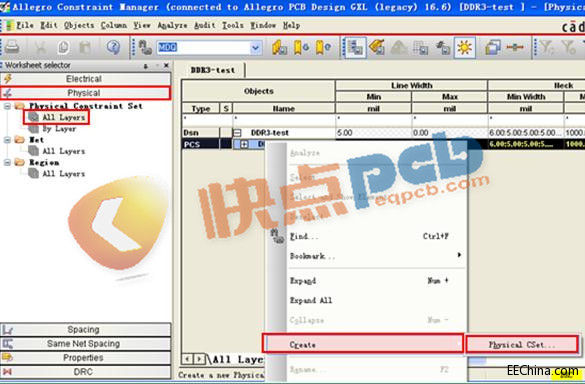

2、在物理规则下建立差分规则

图1-6在物理规则下创建差分规则

如下图1-7弹出命名对话框

图1-7差分规则命名

因为电子规则约束在进行PCB设计布线时更优先,同时电气规则可以设置更多的约束,推荐在电气规则中设置差分走线的约束。

allegro16.6差分信号的设定

在高速PCB布线前

需要对差分信号的规则进行设置

因此

本期重点介绍在电气规则和物理规则下

是如何建立差分信号的规则

1、在电气规则下建立差分规则

首先,点击左边的工作选择区中的ELECTRICALR 工作表下的 ELECTRICALR constrain set=>Routing=>differential pair,然后选择菜单命令 objects=>create=>ELECTRICALR set,如图下图所示

图1-1电气规则下创建差分规则

在弹出 Create Electrical set 对话框。

图1-2电气规则命名

在 Electrical CSet 编辑框输入差分信号规则名称,这时在右边的工作表中可以看到多了一个DIFF_DQS 的约束规则,如下图1-3所示

图1-3规则参数设置

差分信号的约束规则参数主要有以下几个:

Uncoupled Length:差分信号网络中不匹配中的长度,即不能按差分信号走线的总长度。

Min Line Spacing:最小的线间距。

Primary Gap:差分信号最优先选择的线间距。

Primary Width:差分信号最优先选择的线宽。

Neck Gap:差分信号在 NECK 模式下的线间距(用于在布线比较密集的区域)。

Neck Width:差分信号在 NECK 模式下的线宽。

图1-4差分信号参数

设置好差分信号约束规则后,将该约束规则应用于差分信号上,点击左边的工作表选择区中的Electrical 工作表下的 net 下routing,在右边的工作表找到所建的差分信号,在 referenced Electrical CSet 选择刚才设置好的差分信号约束规则 DIFF_DQS,如下图1-5所示。

图1-5给差分信号赋予差分规则

这样就把设置好的差分规则分配到对应的差分网络了。

2、在物理规则下建立差分规则

图1-6在物理规则下创建差分规则

如下图1-7弹出命名对话框

图1-7差分规则命名

因为电子规则约束在进行PCB设计布线时更优先,同时电气规则可以设置更多的约束,推荐在电气规则中设置差分走线的约束。

- Cadence 推出创新的FPGA-PCB协同设计解决方案(04-25)

- 高速PCB布线实践指南(11-01)

- PCB抄板/设计原理图制成PCB板的过程经验(02-04)

- IBIS 模型:利用 IBIS 模型研究信号完整性问题(08-08)

- 巧妙的线路板布线改善蜂窝电话的音质(11-01)

- PCB反设计系统中的探测电路(02-18)