明导:条状过孔成大势所趋

时间:12-17

来源:互联网

点击:

对于28纳米及以下节点,各种新的设计要求使工程师不得不调整传统的数字电路板图设计和验证流程。尤其值得一提的是,过孔的使用受到了很大的影响。新的过孔类型已推出,双重成像(double patterning)、FinFETS 和其它新的设计技巧的加入不仅使过孔的使用显著增多,同时还导致用于定义版图中过孔类型的选择和放置方式的设计规则的数量和复杂度的增加。先进节点工艺中的布局和布线 (P&R) 问题正变得越来越有挑战性。

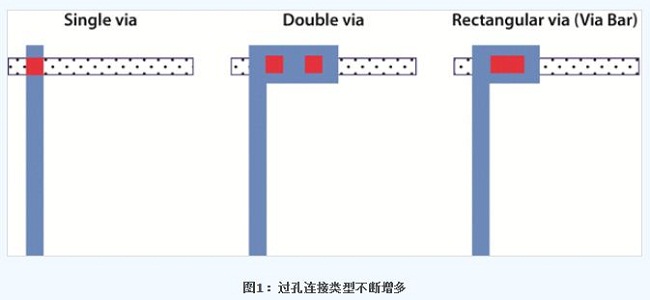

过孔故障一直是影响良率的重大因素。过孔冗余(双过孔)被引入65纳米版图设计中,帮助减少制造过程的变动所引起的过孔故障。对于28纳米节点,明导添加了一种矩形过孔(有时也称条状过孔)。以矩形过孔而非双过孔代替单过孔可以预防过孔故障,同时减少过孔总数。图1显示了三个过孔类型。

减少过孔数量很重要,因为28纳米及以下节点设计所需的传统过孔数量显著增加,究其原因主要有两点:第一,28纳米及以下节点的金属层明显增多,因而需要更多的连接;第二,这些设计节点出现了新的设计要求。例如,由于必须分解几何图形,双重成像层可能会增加所需的过孔数量,而电子迁移限制使得电源/接地线需要更多不同类型的过孔。

随着过孔数量的增多,确保在布局布线过程中正确放置和选择过孔所需的规则的数量和复杂性也显著增加。过孔插入的复杂性迅速提高主要有四个原因:

1,在小的节点设计中,连线更具挑战性,不仅需要新的配置,(这些配置大节点设计不太常用),而且还要考虑先前大节点中并不重要的因素。例如,在20纳米节点上,过孔的选择需要同时评估金属末端-1和+1。绕线不再是仅仅优化过孔,而是同时考虑上下方的金属以及过孔连接金属的方向。

2,更多过孔类型增加了绕线可使用的过孔选择。需要更多绕线规则来定义某种特定过孔何时使用以及如何使用。

3,代工厂定义过孔优先次序 -- 每家代工厂拥有选择特定过孔类型的专有规则。尽管绕线规则允在多种过孔类型之间选择,但是代工厂优先规则会根据几何、环境特征、过孔包住以及许多其它变量掌控这些类型的顺序。此外,这些优先次序可能在过程节点的发展中迅速变化,需要不断更新绕线规则。

4,双重成像(double patterning)-- 双图案分解要求会影响过孔的放置位置和方向,并且必须在布局和布线阶段加以考虑。

但为何这些都成为问题呢?难道绕线工具没有绕线规则来告诉该如何以及在哪里放置布局元素吗?

在数字领域,详细的绕线规则经常都是对设计规则的简化近似,以便可以被编码为库交换格式 (Library Exchange Format, LEF) 规格或绕线工具的技术文件(tech file)。绕线工具通常使用这些简化的 DRC 和 DFM 规则来实现绕线过程中运行时间与准确性的最佳平衡。一旦绕线完成,GDSII 版图就使用签核质量的 DRC/DFM 规则文件和标准验证规则格式 (SVRF) 的规则平台来验证。对于先前的节点,这就能起到充分的作用,因为签核确认时发现的违规数量相对而言还是较低的。

布线工具会报告布局没有违反 DRC/DFM 规则,但签核分析发现大量违规现象。布局和布线后再调试和纠错不仅耗时和占用大量资源,而且处理它们要进行的改动还会导致新的制造违规,或对设计的目标性能产生负面影响。

对于28纳米及以下节点,指导过孔选择和放置的规则远比图表复杂(图2)。不仅仅有更多规则,而且规则更加复杂。正如讨论的一样,视情况而定,可供选择的过孔类型也很多。各代工厂有自己的优先次序,这决定其将选择哪种过孔类型。此外,过孔放置还可能受双重成像等设计因素的影响。

与过孔选择相关的新工艺的要求不仅非常多,而且执行起来相当复杂。如果您使用的是矩形过孔,该如何放置过孔阵列呢?应对双图案需求时,如何准确确定过孔是不是被包住呢?LEF/技术文件不仅需要能够了解和应对这些情况,还必须能够了解和适应特定工厂对优先事项、选择顺序、过孔方向和过孔被包住的要求。

最近的技术进步使得使用这些代工厂验证过的实用工具自动解决这些复杂的过孔摆放问题使其符合 DRC/DFM 规则,而且可以把这些改变自动反标在原始的布局和布线的 DEF 中变得可行。不远的将来,设计师有可能可确保在设计流程的布局和布线阶段能够高效、准确和迅速地实现设计所需的100%过孔优化。

- 点评:全方位剖析中国集成电路核心技术发展之困(01-08)

- 布线工程师如何充分掌控时钟信号?(02-01)

- 高速数字电路设计之串音分析(11-01)

- PCB反设计系统中的探测电路(02-18)

- PCB电路版图设计的常见问题 (11-01)

- 电源完整性分析应对高端PCB系统设计挑战(11-01)