PCB线路上的噪声

当发现数字电路出现电磁干扰现象后,主要的原因是在电源线和地线上,用示波器可以观察到明显的噪声电压。虽然许多人可以断定这些噪声是造成电路电磁干扰问题的原因,但却不知道采取何种手段来解决.为了达到消除噪声的目的,有必要首先明白这些噪声是如何产生的。

1,电源线上的噪声

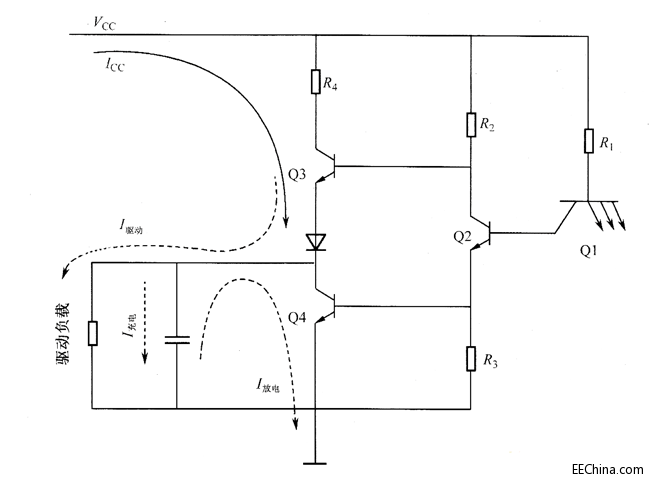

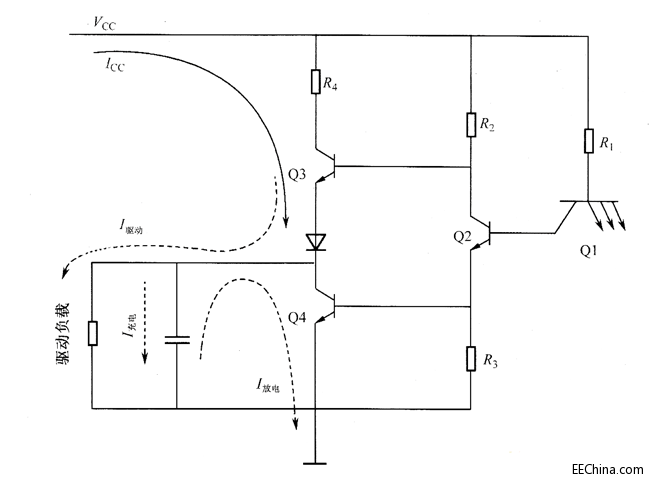

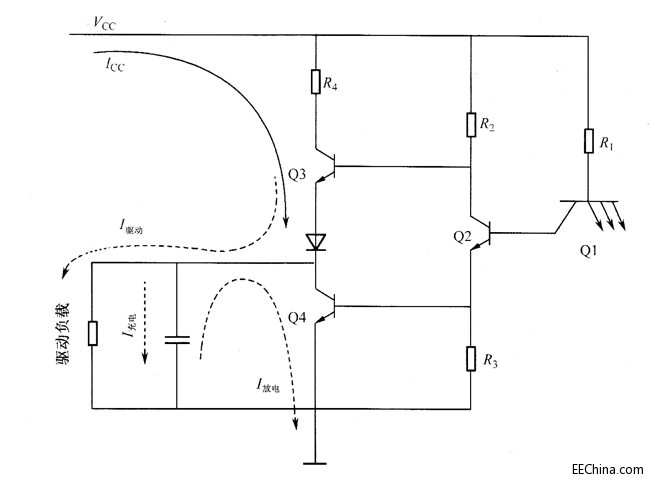

如图1所示是比较典型的门电路输出级,当输出为高电平时,Q3导通,Q4截止;当输出为低电平时,Q3截止,Q4导通。这两种状态都会在电源与地之间形成高阻抗,这样就限制了电源的电流。

图1 典型的门电路输出级

而当状态发生变化时,暂时会有Q3和Q4管同时导通,这时在电源和地之间形成了短暂的低阻抗,产生了30~100 mA的尖峰电流。当门输出电平从低变为高时,电源不仅要保持输出电流,还要给寄生电容充电,使这个电流峰值达到饱和。由于电源线有不同程度的电感,因此当电流发生突变时,则产生感应电压。这就观察到在电源线上的噪声。由于存在电源线阻抗,所以会造成电压的短暂跌落。

2.地线上的噪声

当产生上述尖峰电流的同时,地线上也会流过电流,特别是当输出电平从高变为低时,寄生电容放电,地线上的峰值电流更大。由于地线总有不同程度的电感,也会感应出电压,这就形成了地线噪声。地线和电源线上的噪声不仅会使电路运行不好,还会产生较强的电磁辐射。

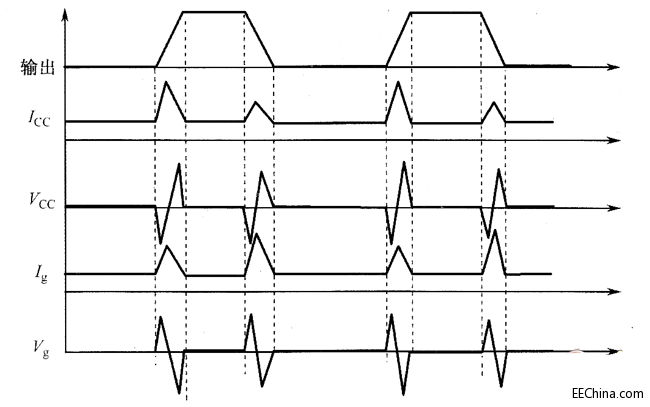

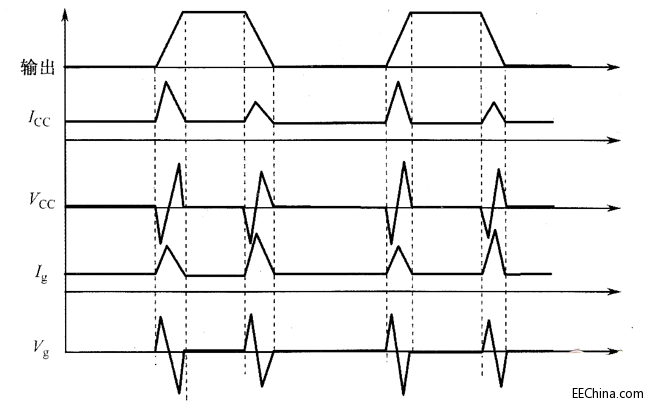

如图2所示就是形成的电源线、地线噪声电压波形。

·“Icc”(电源上电流):在不同的输出状态时,幅值是不同的。稳定时,电流也稳定。

当输出从低变为高时,瞬间短路,电流增加,同时给寄生电容充电,电流更大;当输出电平从高变为低时,瞬间短路,电流增加,但不给寄生电容充电,因此电流较输出电平从低变高时要小。

· 电压“Vcc”(电源上电压):当Icc发生突变时,电源线的电感L会产生感应电压“Ldi/dt”。

“Ig”(地线电流):电源线上的电流与电路中寄生电容放电而形成的电流。输出稳定,电流稳定。当输出电平从低变高时,瞬间短路,电流增加。当输出电平从高变低时,瞬间短路,电流增加,同时寄生电容放电,电流峰值较输出电平从低变高时更大。

“Vg”(地线电压):当“Ig”发生突变时,地线的电感L会有感应电压“Ldi/dt”产生。

图2 电源线、地线噪声电压波形

虽然解决地线噪声电压的方法可以在线路板上设置电源线网格来减小电感量,但要占有大量的布线空间。为了减小电源线电感量,可采取下面的方法:

采用储能电容,其作用是为芯片供给电路输出状态发生变化时所需的大电流,这样就减小了感应出的噪声电压,避免了电流突变。储能电容将电流变化限制在较小的范围内,减小了辐射,所以在线路板上使用电源线网格或电源线面(电源系统具有很小的电感)时增加一些储能电容。

因为储能电容是为芯片提供瞬态高能量,所以在布线阶段要尽量靠近芯片,也就是使储能电容的供电回路面积尽量小,或使储能电容与芯片电源端和地线端之间的走线尽量短。

芯片与储能电容之间的走线长度是芯片自身引脚的长度加上线路板走线的长度。因此,要减小这两部分的总长度,就得选用电源引脚与地引脚靠得很近的芯片,避免使用芯片安装座、表面安装形式的芯片等。

另外,每个芯片的储能电容在放电结束后,都要及时补充电荷,为下次放电做好准备。为了减小对电源系统的骚扰,可通过称为二级储能的电容来提供电荷。当线路板上的芯片较少时,一只二级储能电容安装在电源线的入口处就可以了,该二级储能电容的容量应为芯片储能电容总容量的5倍以上。如果线路板上芯片较多,每5~10片设置一个二级储能电容。这个电容应该使用钽电容,并且要求串联电感尽量小,不要使用铝电解电容而导致内部电感的产生。

- 点评:全方位剖析中国集成电路核心技术发展之困(01-08)

- 布线工程师如何充分掌控时钟信号?(02-01)

- 高速数字电路设计之串音分析(11-01)

- PCB反设计系统中的探测电路(02-18)

- PCB电路版图设计的常见问题 (11-01)

- 电源完整性分析应对高端PCB系统设计挑战(11-01)