适用于2G/3G/4G的无线终端基带芯片

LTE整个上行1ms子帧的数据处理,需要92892cycles,即3024us@330MHz,整个下行链路处理花费1878110cycles,即 3031us@330MHz。由于所有的算法是分布在多个VE 上实现的,几个算法是可以并行处理的,整体1ms处理时延上行是2.083ms@330MHz,下行只有1.52ms@330MHz。在上下行配置为 SA17条件下,每5ms有两个上行子帧,三个下行子帧,上行吞吐量达到17.5Mbps,

下行吞吐量达到60Mbps,达到TD-LTE Cat3的上行峰值速率要求。

5.2 TD-SCDMA 的性能数据

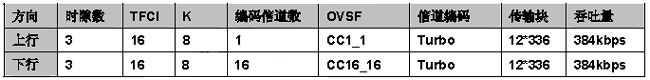

对于TD-SCDMA系统的物理层,以上下行吞吐量分别为384kbps的处理为例,对其性能进行测试。具体测试用例的参数如表4所示:

表4:测试用例参数

主频245MHz时,各个算法模块的每子帧数据处理所需的平均时间如表5所示:

表5:算法效率实测数据

TD- SCDMA整个10ms帧的时间内,在上下行分别达到384kbps流量的条件下,整个上行链路处理花费207053cycles,即 864μs@245MHz,整个下行链路处理花费460376cycles,即1236us@245MHz。由于其中不同部分的算法分布在不同的VE上,实际上各个部分是可以并行运行的,真正一帧数据的时延上行小于864μs,下行小于1236μs的,用1/5的运算量就完全满足实时性要求。

5.3 功耗与面积

目前的MPW样片采用65nm工艺,未使用功耗控制。在主频245MHz下,所有的内核与外设都全速运行,整颗芯片在峰值功耗在1.09W左右。 SL3000在65nm工艺流片,成品芯片的面积是79mm2。根据经验,如采用40nm或以下的工艺和低功耗设计,物理层设计进一步优化,无论是功耗还是面积都会有较大的优化空间。预计面积在30mm2,功耗预计0.5W。

6. 小结

本文基于对 2G/3G/4G的需求分析,介绍了一颗终端基带芯片SL3000的架构,以及基于SL3000 构建的多模终端参考方案,并提供了在此芯片上实现的多模系统的运行性能。从各项测试数据和验证结果来看,SL3000是一颗具有多模功能,且满足 2G/3G/4G性能需求的基带平台,能够比较灵活地通过软件编程而实现多种无线通信系统包括一些自定义的系统的终端。经过进一步的优化设计,其功耗和面积可以和同类多模ASIC芯片相当,但SL3000具有更大的编程灵活性,以适应其它信号处理、如雷达、测试仪表的需求。

- 无线通信系统中的闭环MIMO技术综述(03-16)

- 无线通信系统的GUI设计与仿真实现(01-10)

- 无线通信系统小区间干扰控制技术(03-13)

- 解决无线通信系统频率干扰设计(06-11)

- 基于Zigbee技术家用无线网络的构架(12-14)

- 无线通信领域中的模拟技术发展趋势(蜂窝基站)(09-22)