RF至13GHz超快速建立PLL

端与滤波器最后一个电容的组合电容值必须为1.5 pF左右。但是,VCO单独测得的输入电容为52 pF。

对于环路滤波器电容,建议采用C0G/NP0陶瓷电容(比标准电容具有更快的放电时间),以最大程度缩短相位建立时间。

该电路要求具有出色的布局、接地和去耦技术,如教程MT-031和MT-101所述。可在CN-0302设计支持包中找到完整的原理图、布局文件和物料清单。

测试结果

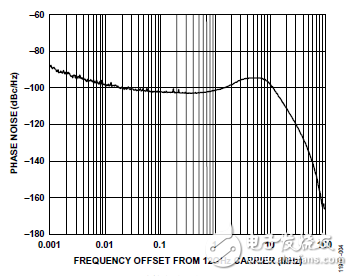

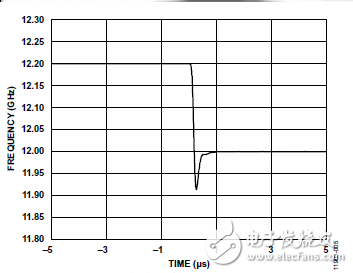

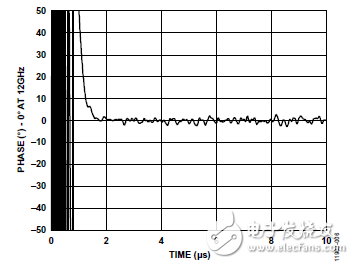

电路的测量相位噪声如图4所示。200 MHz跳频的频率和相位建立时间分别如图5和图6所示。

图4. 12.002 GHz时的相位噪声(LBW = 2.4 MHz)

图5. 200 MHz跳频建立时间(12.2 GHz至12.0 GHz)

图6. 200 MHz相位建立时间(12.2 GHz至12.0 GHz)

电路评估与测试

2.4 MHz有源滤波器PCB修改

使用AD8065而非OP184,为实现2.4 MHz有源滤波器而需要

对标准EV-ADF4159EB1Z所做的修改如下所示:

• 以AD8065ARZ代替U4(8引脚SOIC)

• 以220 、1%、0603代替R1

• 以3 k、1%、0603代替R2

• 以120 、1%、0603代替R3

• 以12 pF、10%、0603代替C1

• 以82 pF、10%、0603代替C2

• 以2.7 pF、5%、0603代替C3

• 保持C4、180 pF不变

设备要求

• 针对AD8065运算放大器和2.4 MHz LBW滤波器元件修改的EV-ADF4159EB1Z评估板

• ADF4159评估软件

• 运行Windows®的PC,带USB端口

• +15 V电源

• +5.5 V电源

• 频谱分析仪:R&S:FSUP26、FSQ26、FSW26、Agilent E5052B或同等设备。

测试设置功能框图

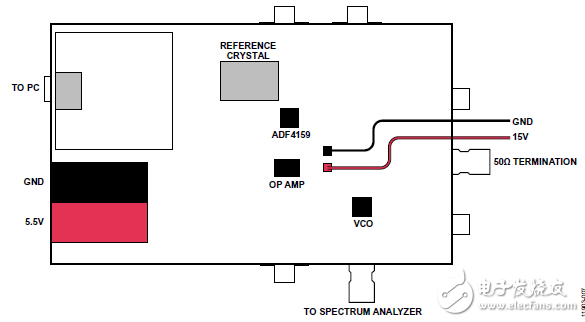

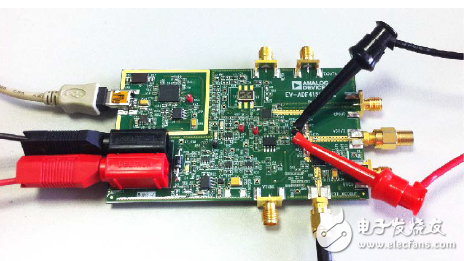

测试设置的功能框图如图7所示,该设置的照片如图8所示。有关运行测试和设置软件的详情,请参见用户指南UG-383。

图7. 测试设置功能框图

图8. EV-ADF4159EB1Z板和测试设置的照片(显示外部连接)

AD8065 ADF4159 有源滤波器 运算放大器 相关文章:

- 如何测量随偏压变化的MLCC电容(05-22)

- 雷达没那么神秘就这点事!(01-13)

- 基于Zigbee技术家用无线网络的构架(12-14)

- 无线通信领域中的模拟技术发展趋势(蜂窝基站)(09-22)

- 新一代移动通信系统及无线传输关键技术(06-19)

- 蜂窝移动通信基站电磁辐射对人体影响的探讨(04-10)