最适合的选择——ZigBee SoC解决方案

在开发2.4 GHz ZigBee®无线网络应用时,设计工程师通常会面临系统分割的选择:对ZigBee的连接性及网络处理解决方案而言,最佳的整合层级为何?从效能、功耗及成本的角度来看,何者是最适合的选择——是将2.4 GHz无线收发器及处理核心整合为单芯片解决方案的ZigBee系统单芯片(SoC)比较好?还是具有独立收发器及主处理器的离散式方案较佳?

在解决这些问题之前,先让我们仔细分析ZigBee技术。根据IEEE针对低功率无线网络所推出的802.15.4 MAC/PHY规格,ZigBee凭借增加网状网络协议及应用文件档案来扩展IEEE 802.15.4,让各装置之间能够完全互相操作。ZigBee使用高可靠、可扩充的网状网络协议,可支持数千个节点。ZigBee应用文件档案则针对家庭/商业自动化、智慧能源、健康医疗及零售设备定义共通语言。ZigBee也提供设备的测试及认证,以确保从射频到应用层的互相操作性。

针对传感及控制网络,ZigBee已被设计为高度可靠、低成本、低功率的无线网络解决方案。系统分区的选择最终将对ZigBee解决方案的网络效能、功耗及成本造成极大的影响。

系统分区

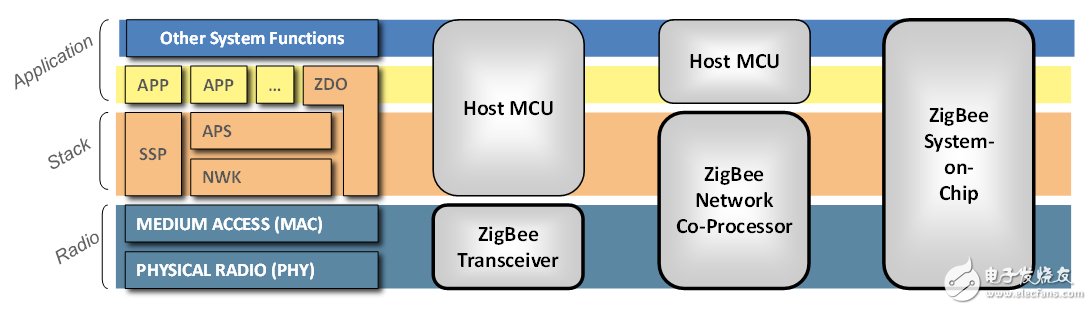

图1显示三种基本的系统分区选择:ZigBee系统单芯片、ZigBee网络协同处理器(NCP)加上主处理器,以及ZigBee收发器加上主处理器。

在系统单芯片的设计中,IEEE 802.15.4的标准,射频是嵌入式处理器的一个外设,所有的封包处理及应用处理都在单芯片内执行。系统单芯片一般会包括微处理器的硬件外设 ,以支持运算负荷繁重的功能,例如AES(高级加密标准)的加密。

在网络协同处理器(NCP)的设计中,ZigBee协议栈是在射频及网络处理器芯片上运作,然后运用其SPI或UART接口连接至主处理器。主处理器仅处理那些被设备应用传送或接收的封包。至于那些路由封包的处理,包括安全处理,则是在网络处理器上进行,毋需中断主处理器。因此,SPI或UART处理时间的影响仅会发生在封包的来源或目的地。

一个ZigBee收发器仅包含RF收发器及关键时序的MAC/PHY功能,主处理器则支持MAC的上层、网络协议及应用编码。所有的封包都必须传送至主处理器进行处理。仅进行路由的那些封包则会被传送至主处理器后再返回至射频端,以进行再次传输,基本上是通过UART或SPI接口进行。通常AES加密的运作是在收发器芯片上执行;因此需要额外的UART或SPI传输来支持安全处理。

图1:ZigBee系统分区选择

网络性能

系统设计必须考虑吞吐量(throughput)及延迟(latency),以确保网络可符合产品的设计目标。吞吐量是用来测量网络可支持多少的数据传输量,这是非常关键的指标,用来测定网络的扩充性。延迟则是测量节点间的讯息传输速度,这也是非常关键的指标,用来测定网络的响应能力。吞吐量及延迟都与组件分割有关,系统架构必须纳入考虑。

ZigBee是一种复合式的网状网络协议,包括保持在启动状态的路由器中枢,以及一般是在睡眠状态中的终端装置。路由器负责在终端装置间;或是从终端装置至中央控制器传递讯息。ZigBee网络的吞吐量及延迟会与路由器处理数据封包及将它们传送至适当目的地的速度有关。

本文选自电子发烧友网6月《智能工业特刊》Change The World栏目,转载请注明出处。

路由器的效率与系统分区有关。若系统使用系统单芯片或网络协同处理器,则可以在不唤醒或中断主处理器的情况下处理所有的路由,封包一般会在5-10 ms内被传送。若系统使用收发器,则这个收发器就必须唤醒或中断主处理器去处理每一个封包。这样的唤醒或中断延迟时间可能会大于100 µs。此外,数据封包必须在收发器和主处理器之间传送。ZigBee封包可能大至127字节(1016位),以一般的SPI/UART数据传输率传送一个封包至处理器后再返回收发器,可能需耗费0.5-4 ms。ZigBee在MAC及网络层、有时甚至在应用层都会使用AES加密。如果主处理器或收发器都未支持高效AES加密,则可能需要额外的UART或SPI数据传输。

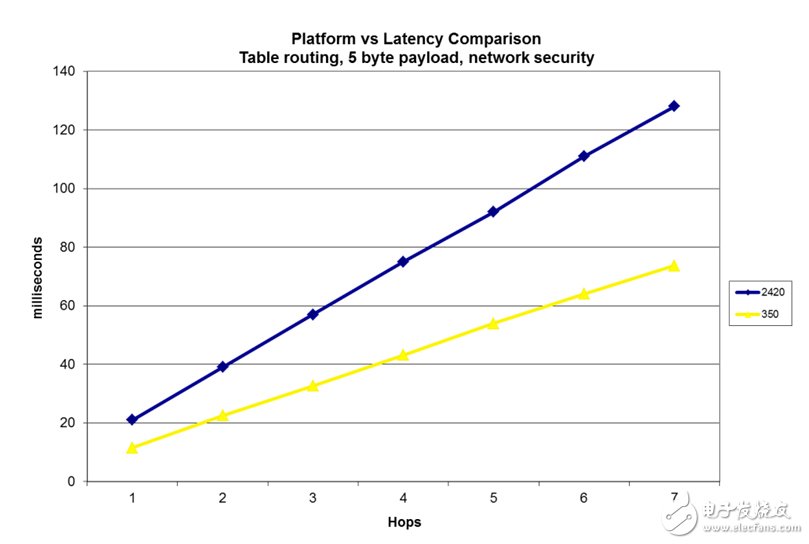

图2显示系统分割对于小型5字节有效负载的网络效能的影响,其中仅ZigBee收发器有支持AES加密。在使用系统单芯片或网络协同处理器的网络中,单一中继点(hop)的延迟为10 ms,在使用收发器的网络中则是20 ms。由于每个节点需要花费两倍的时间去处理一个封包,因此使用收发器的网络吞吐量会减少50%,这会让可支持装置的最大活动数量减半。针对那些极为重视时间的应用,例如照明,延迟的增加将限制可允许的中继点最大数量,如此会降低网络的扩充性及可靠性。

图2:延迟vs.系统分割

功耗

Zi

- WIFI模块轻松实现接入物联网案例(02-09)

- 你的低功耗蓝牙信标是否安全且私密?(02-10)

- 基于CP2200简易型以太网接口设计(07-24)

- OK Labs技术白皮书——SecureIT Mobile企业版(02-28)